timing check

描述设计时序时,所有的时序检查都有一个参考事件(reference event)和一个数据事件(data event),数据事件常常是数据信号,而参考事件常常是时钟信号,它们通过一个布尔表达式相联接,还包括一个可选的notifier寄存器选项,这个寄存器用来打印错误信息或者传播X态。

检查时序窗口的稳定性,包括:setup、hold、setuphold、recovery、removal和recrem。

$setuphold

$setuphold(reference_event, data_event, setup_limit,hold_limit, notifier, [timestamp_cond, timecheck_cond,delayed_reference_signal, delayed_data_signal]);

其中setup limit 和hold limit 的数值是从SDF 文件取出反标到网表上的。

$setup (data_event, reference_event, limit, notifier);

当reference_event time - limit < data_event time < reference_event time时,就会报告setup time violations。

$hold (reference_event, data_event, limit, notifier);

当reference_event time < data_event time < reference_event time + limit时,就会报告hold time violations。

$setuphold (reference_event, data_event, setup_limit, hold_limit, notifier);

setup和$hold 两者的联合。

例如:

setup (negedge d, posedge clk, 2, notifier); 和 $hold (posedge clk, negedge d, 1, notifier);

setup和hold都为正值:

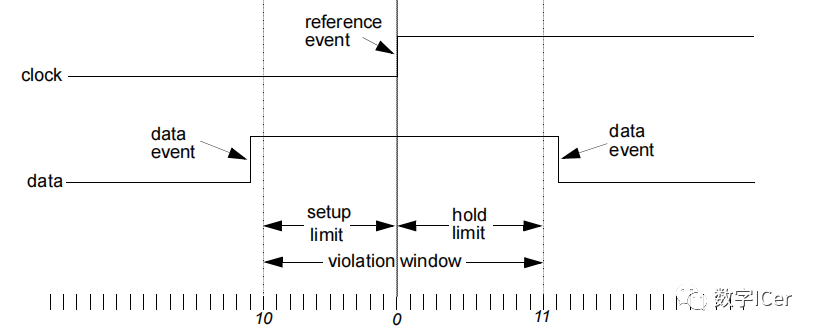

如下面例子 setup limit 和 hold limit 都为正值:

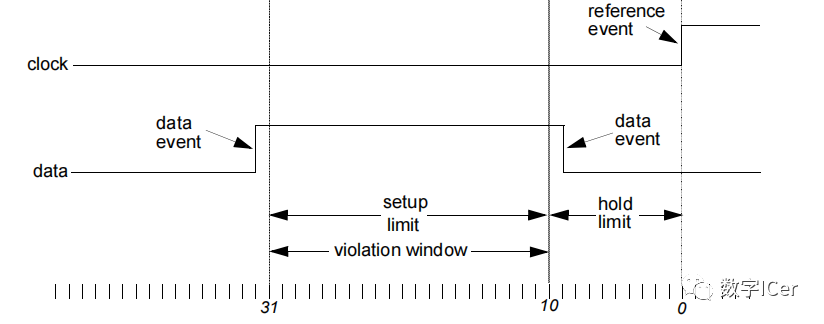

$setuphold (posedge clock, data, 10, 11, notifyreg);

其中,data要在时钟上升沿10ns保持稳定(假设时间单位是ns),在clk上升沿之后11ns内保持稳定;如果在时钟clk上升沿到来之前,data小于10ns或时钟clk上升沿到来之之后小于11ns,则为时序违例;

Positive Setup and Hold Limits

Positive Setup and Hold Limits

上图中,可见,

对于setup检查Data Event 要早于 Clock Event;

对于hold 检查Data Event 要晚于 Clock Event;

符合这种情况的时序,setup limit 和 hold limit 用正值来表示。

setup为负值,hold都为正值:

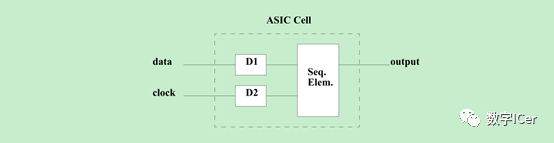

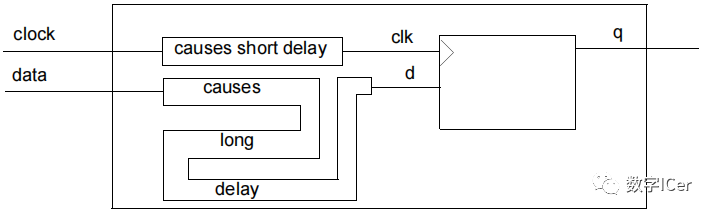

在讨论这个问题之前需要弄明白,我们现在所说的setup hold timing check是针对std cell的,在实际的std cell中不仅仅有DFF还有一些buffer之类的cell。

一个典型的std cell的简化结构如上图所示,D1和D2表示两个delay cell。而实际上我们要保证的是DFF的setup 和hold timing check是正值,由于D1和D2两个cell的delay不同就导致了在对std cell做timing check时出现了负值的timing check。再次强调,这里的负值的timing check是针对std cell的并不是针对DFF的。

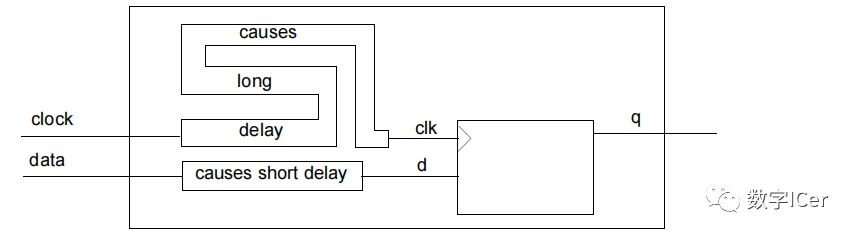

当标准单元内部clk上有较长的延迟时,对于setup检查Data Event就可以晚一些来,如果晚于Clock Event(时刻为 0),用负值来表示。

$setuphold (posedge clock, data, -10, 31, notifyreg);

Negative Setup Limit

Negative Setup Limit

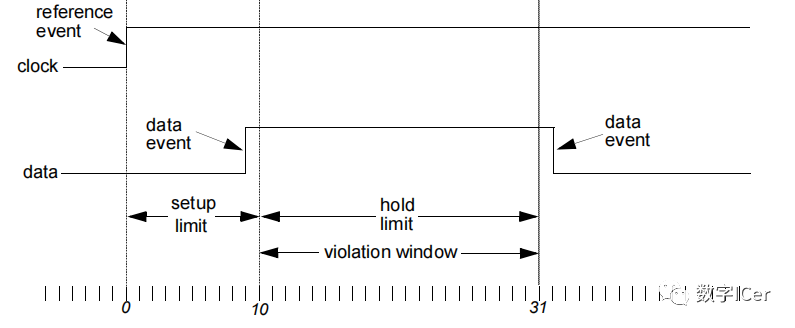

setup为正值,hold都为负值:

当标准单元内部data上有较长的延迟时,对于hold检查Data Event就需要早一些来,如果早于Clock Event(时刻为 0),用负值来表示。$setuphold (posedge clock, data, 31, -10, notifyreg);

Negative Hold Limit

Negative Hold Limit

需要注意的是不论setup 或者hold出现负值,但setup和hold的和必须是正值。这是因为setup必然要发生在hold的前面。

$recrem

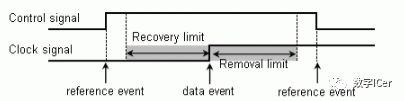

复位信号的恢复时间检查:

$recovery (reference_event, data_event, limit, notifier);

当data_event time - limit < reference_event time < data_event time时,就会报告recovery time violations。

复位信号的移除时间检查

$removal (reference_event, data_event, limit, notifier);

当data_event time < reference_event time < data_event time + limit时,就会报告removal time violations。

复位信号的恢复/移除时间检查:

$recrem (reference_event, data_event, recovery_limit, removal_limit, notifier);

$recrem是$recovery和$removal两者的联合。

recovery (posedge clr, posedge clk, 2, notifier); 和 $removal (posedge clr, posedge clk, 3, notifier);

数据事件常常是时钟信号,而参考事件常常是控制信号,比如清除信号或者置位信号,如下图:

启用负时序检查

当时序存在负值时,必须要用 recrem 来表示;而不能用单独的 hold,removal;

同时使用负时序检查,必须在编译设计时包含+neg_tchk和-negdelay选项。如果省略此选项,VCS将将所有负限制更改为0。

如果在+neg_tchk选项中包含 +no_notifier选项,则表示notifer寄存器不进行翻转,X态不会传播,但是vcs还是会报告timing violation;

相反,如果在+neg_tchk选项中包含+no_tchk_msg选项,则vcs不报告timing violation。但VCS仍然会创建时钟和数据信号的延迟,并在存在时序违例时翻转notifer寄存器。

+notimingcheck 表示在vcs编译过程中不进行 setuphold,recrem 等函数的编译,vcs产生delayed_reference_signal 和delayed_reference_data但是不会去标记这些delay的值,从而不进行任何的timing检查。

-

数据

+关注

关注

8文章

7067浏览量

89108 -

时序

+关注

关注

5文章

389浏览量

37347

发布评论请先 登录

相关推荐

环路增益的稳定性

使用SPICE工具检查运放稳定性

基于利用Pspice模型的放大器环路稳定性设计

如何提高lwip的稳定性?

浅析环路稳定性原理与DCDC Buck环路稳定性

电力系统中的电压稳定性介绍

电感的稳定性

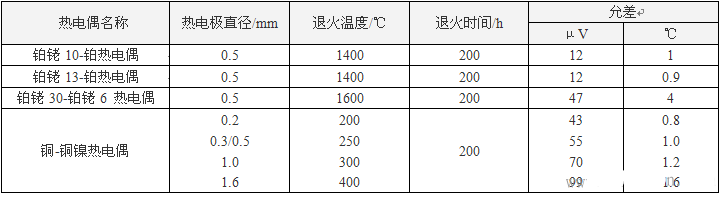

什么是热电偶稳定性?如何检测热电偶稳定性?

如何检查时序窗口的稳定性

如何检查时序窗口的稳定性

评论