电子发烧友网报道(文/周凯扬)对于高效的数据并行负载处理来说,矢量架构的吸引力越来越大,主流ISA都开始注意到这一点。就拿我们熟悉的前超算王者——日本的富岳来说,其处理器富士通A64FX就是基于Arm可伸缩矢量扩展(SVE)的。

Arm也在随后推出的Armv9架构中提出了改良版的SVE2,并在其中加入了对NEON的兼容,SVE2在HPC之外的市场应用中做出了指令优化,甚至可以用于手机、汽车等智能设备中。

正是因为有了SVE的存在,富岳才得以单靠通用处理器完成高性能的大数据运算,而不是像其他主流超算一样,还要靠堆积GPU、FPGA和AI加速器等片外加速器才能实现可观的性能,我国的神威太湖之光同样运用了这样的矢量设计思路。但以上这些都是专有架构,微架构不透明的同时也限制了开源和定制化方案的出现,而这些均可以在RISC-V上一一实现。

RISC-V矢量处理器的吸引力

RISC-V的矢量扩展RVV自2015年提出以来,已经有了长足的进展,也有了正式的1.0版本规范。与传统的SIMD指令相比,RVV提供动态的矢量长度修改,做到了更高的效率、更小的代码体积和更简单的循环结束。我们近期已经看到了不少RISC-V处理器被广泛使用的新闻,比如谷歌选择在其TPU上加入SiFive的X280处理器,其实看重的就是它在矢量处理上的优势。

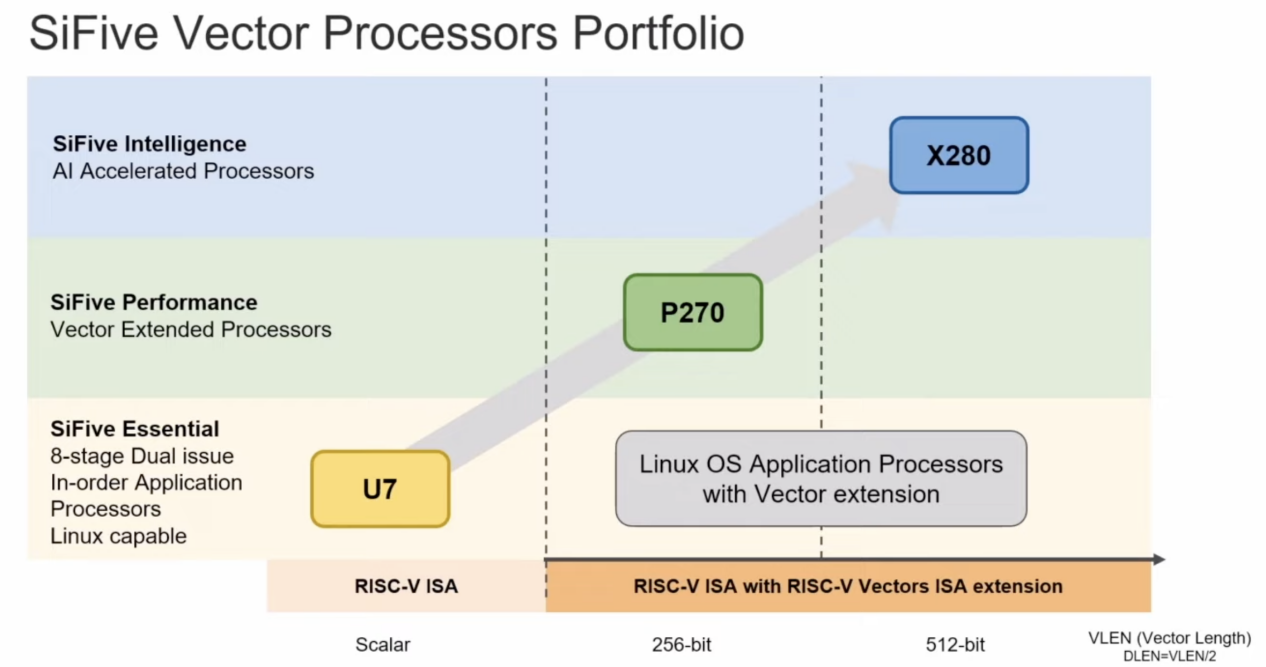

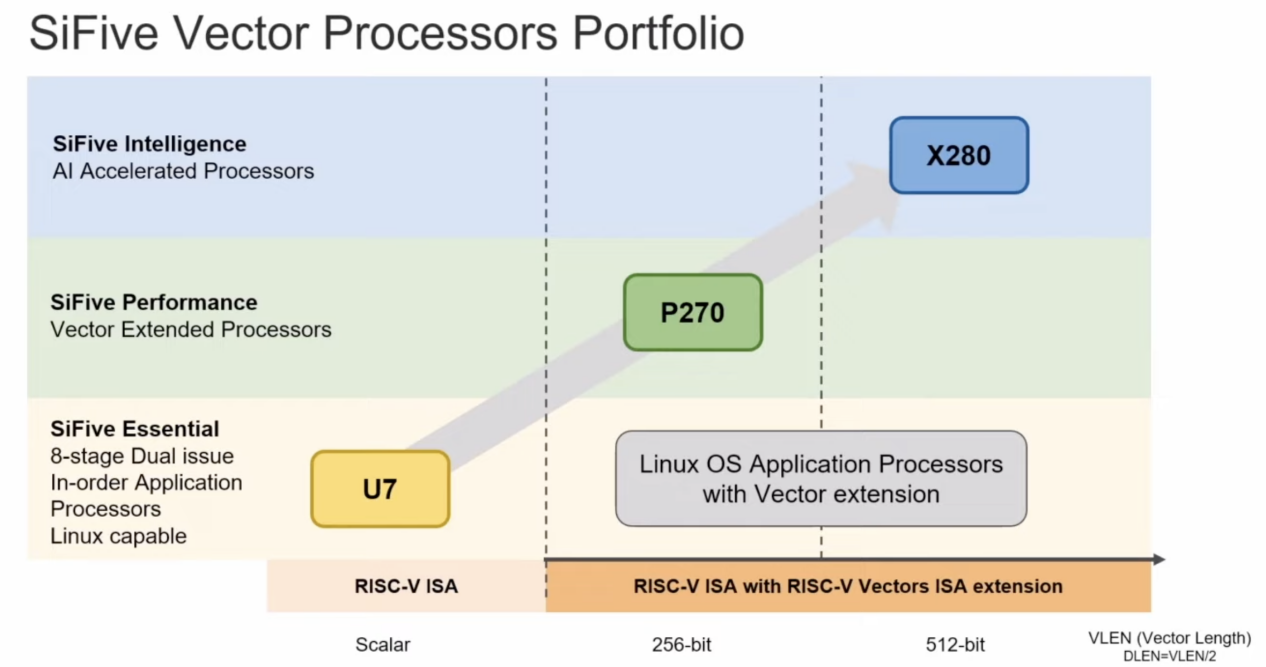

SiFive矢量处理器 / SiFive

所以我们看到在SiFive的处理器产品中,像Performance P270和Intelligence X280都拥有优秀的矢量处理能力,后者更是引入了一个512位矢量寄存器长度的架构,在完全支持矢量扩展标准的同时,还支持动态可变矢量长度的运算。SiFive也在其矢量扩展上做出了改进,称其为SiFive智能扩展,与直接基于RV64GCV架构的设计相比,X280的智能扩展在INT8格式下的矩阵乘法运算时可将执行速度提高12倍。

而且这不仅仅造福的是数据中心,还有受制于功耗却又需要高吞吐量和单线程性能的边缘应用,比如AR/VR、数码相机等等。SiFive同样测试了可用于移动端或嵌入式设备的轻量级神经网络MobileNet,相较基于RISC-V标量的架构,SiFive智能扩展可以将速度提升144倍。

同样的还有晶心科技推出的RISC-V矢量处理器NX27V,该处理器采用了5级流水线的设计,晶心为其设计了强大的矢量处理单元,拥有32个矢量寄存器,最高支持512位的矢量长度,为了进一步支持AI应用,晶心还为其增加了BF16和INT4的数据格式支持。据正在打造可扩展的高性能AI超算的初创公司Luminous Computing透露,他们打造的系统用到了数百个NX27V VPU核心,极大地提升了该系统的深度学习性能。

开源RISC-V矢量处理器

RISC-V作为开源架构最棒的一点就在于,总是不缺香山处理器这样优秀的开源方案。比如2019年推出的Ara就是一款高效矢量协处理器,用于辅助OpenHW的CVA6 RISC-V应用处理器Ara,只不过Ara刚发布之际还是基于早期的RVV规范设计的。

来自苏黎世联邦理工学院(ETH)和华为苏黎世研究中心的研究员们借助Ara的启发,基于RVV1.0发表了一个开源的高效RISC-V矢量处理器设计。他们基于格芯的22FDX工艺进行了吞吐量和PPA的验证,整个系统运行频率为1.34GH,在关键的矩阵乘法内核下,FPU的利用率可以达到98%以上。

相较之下,SiFive的X280和另一个开源矢量协处理器Vicuna宣称的FPU利用率大于90%,伯克利的开源方案Hwacha可以做到95%以上。为了展示从RVV扩展这么多年以来的改进,他们也与基于RVV 0.5版下的设计做了对比,结果是在面积占用上有了15%的提升,吞吐量也有了6%的提升,双精度计算效率也做到了37.1GFLOPS/W。

结语

AI时代下,矢量处理的应用场景已经远超我们的现象,包括深度学习、推荐系统、键值存储和HPC等,都已经广泛利用了矢量计算。但如何做到高效高性能,才是未来所有ISA的努力方向,而RISC-V作为后来者,反而能在这上面找到弯道超车的机会。

Arm也在随后推出的Armv9架构中提出了改良版的SVE2,并在其中加入了对NEON的兼容,SVE2在HPC之外的市场应用中做出了指令优化,甚至可以用于手机、汽车等智能设备中。

正是因为有了SVE的存在,富岳才得以单靠通用处理器完成高性能的大数据运算,而不是像其他主流超算一样,还要靠堆积GPU、FPGA和AI加速器等片外加速器才能实现可观的性能,我国的神威太湖之光同样运用了这样的矢量设计思路。但以上这些都是专有架构,微架构不透明的同时也限制了开源和定制化方案的出现,而这些均可以在RISC-V上一一实现。

RISC-V矢量处理器的吸引力

RISC-V的矢量扩展RVV自2015年提出以来,已经有了长足的进展,也有了正式的1.0版本规范。与传统的SIMD指令相比,RVV提供动态的矢量长度修改,做到了更高的效率、更小的代码体积和更简单的循环结束。我们近期已经看到了不少RISC-V处理器被广泛使用的新闻,比如谷歌选择在其TPU上加入SiFive的X280处理器,其实看重的就是它在矢量处理上的优势。

SiFive矢量处理器 / SiFive

而且这不仅仅造福的是数据中心,还有受制于功耗却又需要高吞吐量和单线程性能的边缘应用,比如AR/VR、数码相机等等。SiFive同样测试了可用于移动端或嵌入式设备的轻量级神经网络MobileNet,相较基于RISC-V标量的架构,SiFive智能扩展可以将速度提升144倍。

同样的还有晶心科技推出的RISC-V矢量处理器NX27V,该处理器采用了5级流水线的设计,晶心为其设计了强大的矢量处理单元,拥有32个矢量寄存器,最高支持512位的矢量长度,为了进一步支持AI应用,晶心还为其增加了BF16和INT4的数据格式支持。据正在打造可扩展的高性能AI超算的初创公司Luminous Computing透露,他们打造的系统用到了数百个NX27V VPU核心,极大地提升了该系统的深度学习性能。

开源RISC-V矢量处理器

RISC-V作为开源架构最棒的一点就在于,总是不缺香山处理器这样优秀的开源方案。比如2019年推出的Ara就是一款高效矢量协处理器,用于辅助OpenHW的CVA6 RISC-V应用处理器Ara,只不过Ara刚发布之际还是基于早期的RVV规范设计的。

来自苏黎世联邦理工学院(ETH)和华为苏黎世研究中心的研究员们借助Ara的启发,基于RVV1.0发表了一个开源的高效RISC-V矢量处理器设计。他们基于格芯的22FDX工艺进行了吞吐量和PPA的验证,整个系统运行频率为1.34GH,在关键的矩阵乘法内核下,FPU的利用率可以达到98%以上。

相较之下,SiFive的X280和另一个开源矢量协处理器Vicuna宣称的FPU利用率大于90%,伯克利的开源方案Hwacha可以做到95%以上。为了展示从RVV扩展这么多年以来的改进,他们也与基于RVV 0.5版下的设计做了对比,结果是在面积占用上有了15%的提升,吞吐量也有了6%的提升,双精度计算效率也做到了37.1GFLOPS/W。

结语

AI时代下,矢量处理的应用场景已经远超我们的现象,包括深度学习、推荐系统、键值存储和HPC等,都已经广泛利用了矢量计算。但如何做到高效高性能,才是未来所有ISA的努力方向,而RISC-V作为后来者,反而能在这上面找到弯道超车的机会。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

RISC-V

+关注

关注

44文章

2235浏览量

46054

发布评论请先 登录

相关推荐

《RISC-V能否复制Linux 的成功?》

,创建实现自有加速器算法的自定义异构集群。RISC-V作为一种ISA,我们一开始是在处理器内核中采用吸引人的通用构建块,然后在此基础上进行构建,同时还利用最好的商业工具增强使用者的信心。所以,IP

发表于 11-26 20:20

什么是RISC-V?以及RISC-V和ARM、X86的区别

图纸,处理器就是房子。

RISC和RISC-V的区别

RISC全称Reduced Instruction Set Computer,即精简指令计算

发表于 11-16 16:14

RISC-V,即将进入应用的爆发期

计算机由控制整体的CPU(中央处理器)和加速器两部分构成。在AI计算中,功耗和效率是两个关键因素。RISC-V架构通过其简洁的设计和定制化的扩展,可以实现高效的能量使用。该架构能够通过

发表于 10-31 16:06

risc-v在人工智能图像处理应用前景分析

的兼容性和可靠性,并为其在人工智能图像处理领域的应用提供更有力的保障。

综上所述,RISC-V在人工智能图像处理领域具有广阔的应用前景。其开源性、灵活性、低功耗和高性能等特点使得它成为

发表于 09-28 11:00

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !

加入RISC-VAdvocate行列!我们正在寻找来自世界各地的RISC-V爱好者,通过全球推广和参与,成为支持RISC-V进步的关键参与者。作为一名RISC-VAdvocate,您将

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地

获三份益

青稞RISC-V,更懂下游客户的MCU内核

通用RISC-V架构进入MCU行业难免水土不服。沁恒通过“架构级”创新,解决下游开发/应用过程中的痛点问题,让青稞RISC-V更接

发表于 08-30 17:37

risc-v的发展历史

了基于RISC-V指令集的服务器处理器,安谋科技也推出了RISC-V MCU等产品。

学术界与开源社区:RISC-V架构在学术界和开源社区中也得到了广泛的研究和应用。许多研究机构和开发

发表于 07-29 17:20

rIsc-v的缺的是什么?

RISC-V作为一种开源的指令集架构(ISA),自其诞生以来就受到广泛关注和应用,但它也存在一些不足之处。以下是RISC-V架构目前存在的主要缺点:

1. 性能问题

相对于专用ISA的性能差距:尽管

发表于 07-29 17:18

RISC-V适合什么样的应用场景

设计使得开发者可以灵活选择所需的指令集和模块,以满足嵌入式系统的各种性能要求。

3. 人工智能(AI)和机器学习(ML)

高性能计算:RISC-V结合AI加速器或协处理器,可以提供高效的人工智能

发表于 07-29 17:16

为什么要有RISC-V

RISC-V(“RISC five”)的目标是成为一个通用的指令集架构(ISA):①、它要能适应包括从最袖珍的嵌入式控制器,到最快的高性能计算机等各种规模的

发表于 07-27 15:05

浅析RISC-V领先ARM的优势

RISC-V的开源特性和定制化能力使其在某些特定领域具有更强的竞争力。

综上所述,RISC-V相对于ARM的优势主要体现在开源与免费、定制化能力强、生态系统的快速发展、安全性与可靠性以及应用领域广泛等方面。这些优势使得

发表于 06-27 08:45

Ubuntu现已适配RISC-V单板计算机Milk-V Mars

科技高性能RISC-V多媒体处理器昉·惊鸿-7110(JH-7110)。RISC-V单板计算机Milk-VMarsMilk-VMars是全球首款信用卡大小的四核高性

国产RISC-V MCU推荐

,CH583搭载32位青稞RISC-V处理器WCH RISC-V4A,低功耗两级流水线,高性能,拥有多档系统主频,最低32KHz ,拥有特有高速的中断响应机制。

单片搞定Wi-Fi和蓝牙

许多网友也

发表于 04-17 11:00

什么是RISC-V?RISC-V的关键技术

RISC-V不仅仅是一个流行语;它建立在坚实的技术基础之上,使其有别于其他指令集架构 (ISA)。RISC-V的核心是基于精简指令集计算(RISC)原则,强调效率和性能。

发表于 03-26 09:34

•3438次阅读

RISC-V 基础学习:RISC-V 基础介绍

计算机指令设计架构后。我们来看看 RISC-V。

RISC-V 的 “V”, 有两层意思,一方面代表第5代 RISC;另一方面, “

发表于 03-12 10:25

通用计算仍有差距,RISC-V可靠矢量处理弯道超车

通用计算仍有差距,RISC-V可靠矢量处理弯道超车

评论