01

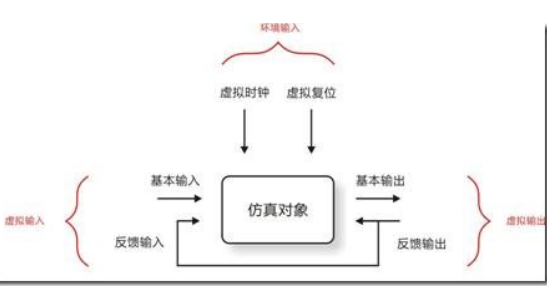

对于仿真的激励测试,其实会有代码覆盖率一说,不过我们平常可能更多是功能覆盖,代码覆盖估计关注的人要少些,不过作为相对系统性的学习,还是大概看下这个功能吧~

02

涉及到的测试代码文件就文末自行获取了,直接开始正题吧。

把文件准备好后,打开Modelsim,将路径切换到对于的文件路径

例:cd E:/Soft_File/Sim_File/coverage

接着创建工作库(work)=> 编译.v文件(指定覆盖测试的类项)

vlib work vlog *.v +cover=bcesxf

附:代码覆盖率,在Modelsim中提供了以下几种覆盖的类型,简单说明一下

A-语句覆盖(Statement coverage):逐行统计每个语句的执行情况

B-分支覆盖(Branch coverage):统计每个条件“if/then/else”和“case”的执行情况

C-条件覆盖(Condition coverage):算是分支覆盖的扩展吧,把判断条件都覆盖到

D-表达式覆盖(Expression coverage):和条件覆盖又有点相似,就表达式左右侧的比对

E-跳转覆盖(Toggle coverage):逻辑节点的跳转,状态发生变化的意思

F-FSM覆盖(FSM coverage):有限状态机的状态、转换还有路径统计

G-SystemVerilog类覆盖(SystemVerilog class coverage):这部分没咋涉及过,应该是SV的类统计

然后命令中的 +cover=bcesxf大概就知道是指什么了吧?除了x要特殊一丢丢

branch, condition,expression, statement, extended toggle, finite state machine

03

启动覆盖测试吧~

vsim -coverage test_sm

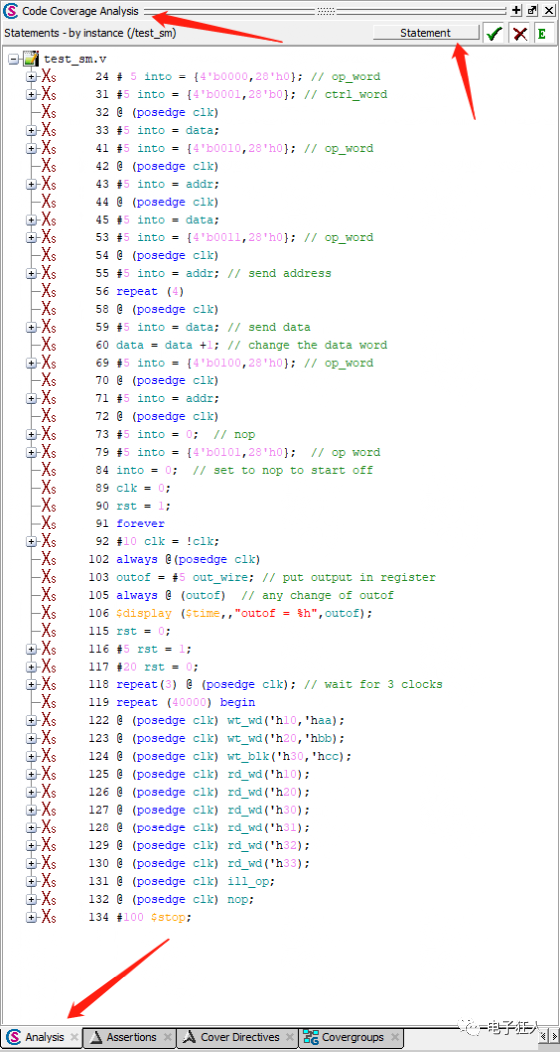

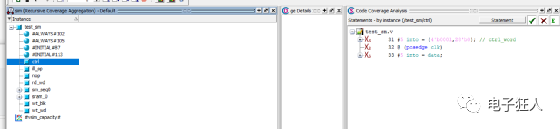

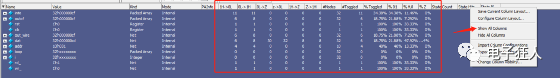

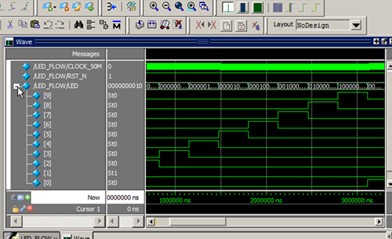

先关注这个界面,通过这个界面可以执行指定的的覆盖测试,然后分析的结果会以那个小图标的形式显示出来,或者,然后有对应的右下标字母,字母和刚刚介绍的一个意思,还会有个E的字样,就是被排除在覆盖测试之外产生的一些状态。

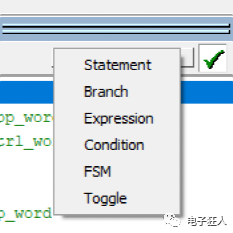

可以在这选对应的覆盖测试

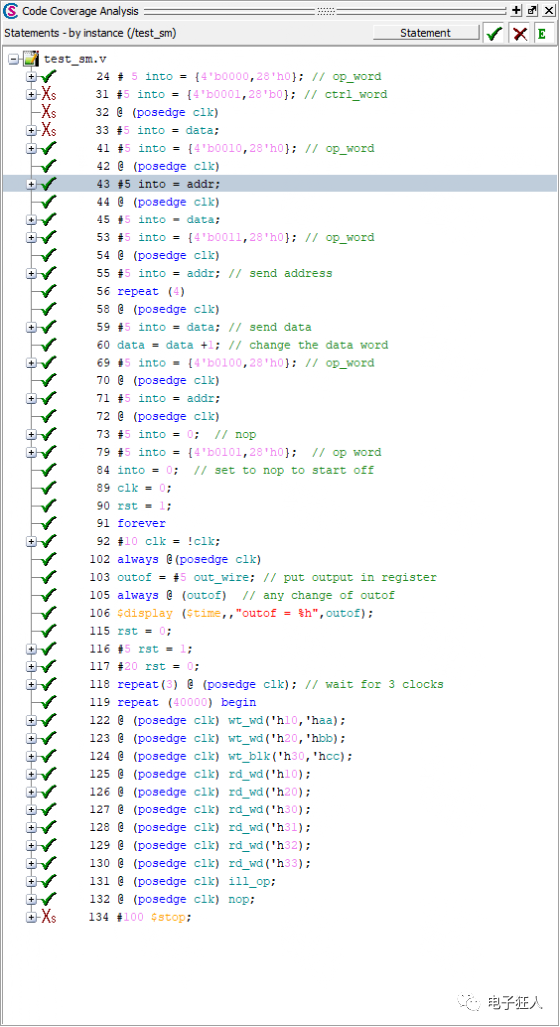

稍微运行一下,做语句覆盖测试,结果发生改变

run 1ms

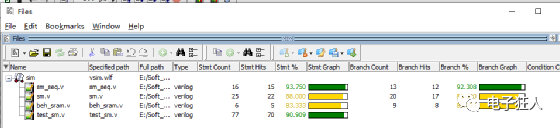

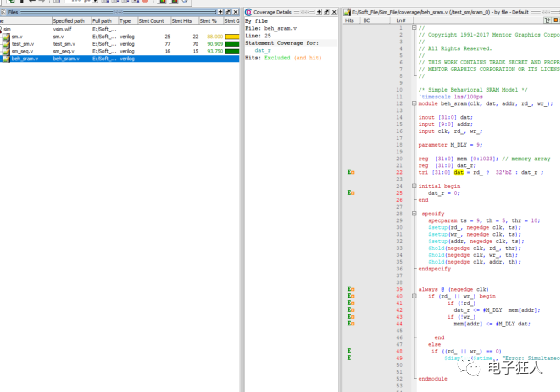

在Files的窗口也能看到相应的代码覆盖率

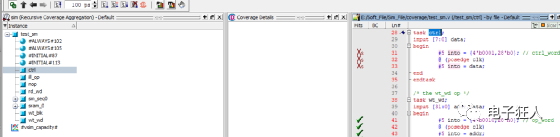

打开sim的窗口,选中不同的目标,在右侧的分析窗口会变成相应的代码覆盖情况

直接双击对应的目标,会直接显示其在源码中的位置

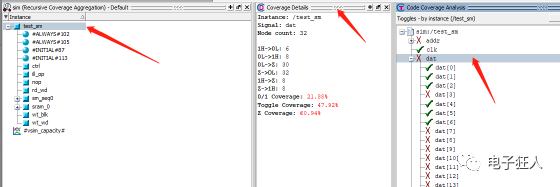

接着在分析界面将覆盖类型换成Toggle,然后选中test_sm,分析界面再点dat,详细说明的界面就会出现对应的跳转情况

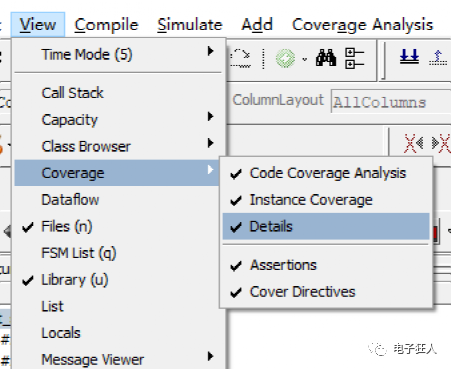

要是没这个Details的界面,可以在菜单里,View > Coverage > Details 将其使能

切换到sim窗口,选中test_sm,然后View > Objects,再然后右键后Show All Columns

这时可以看到相应跳变的静态指示

04

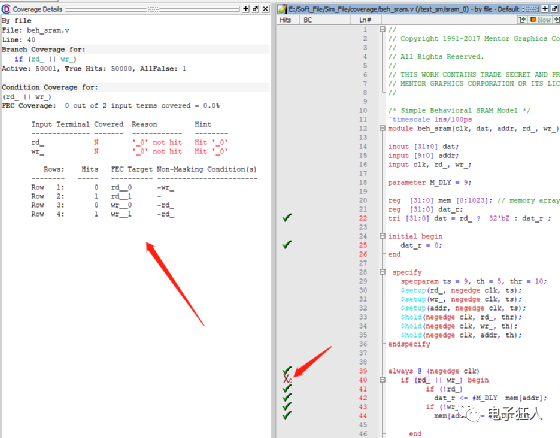

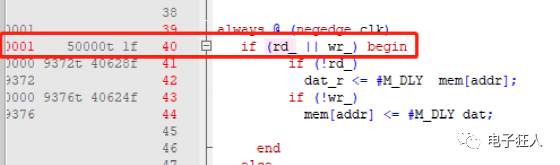

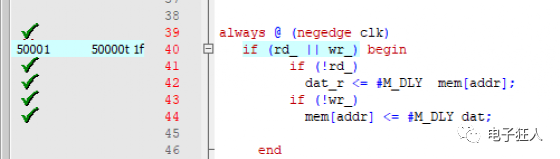

在Files的界面中双击beh_sram.v打开源码界面,然后看到40行,条件覆盖没满足的情况,点Xc那个图标,在详细界面可以看到对应的描述

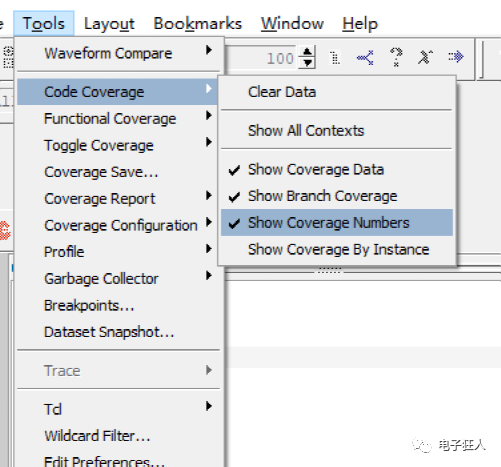

接着将覆盖次数显示出来,Tools > Code Coverage > Show coverage numbers

软件大小有点问题,50001只显示到了0001......

关掉数字的显示,恢复图标显示的情况,鼠标直接放到对应的代码位置,也能显示

05

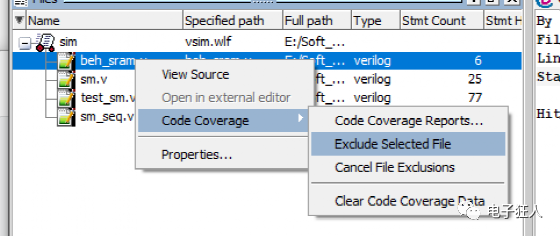

在Files界面,可以选定要排除覆盖测试的文件,右键 > Code Coverage > Exclude Selected File ,Cancel...就可以取消排除。

然后可以看到整体发生变化,代码界面的√和×都变为了E的字样

E*指的就是被排除在外,但测试时还是被击中过,E就是完全被排除在外了,可以点那个图标,然后看详细描述里的信息理解。

06

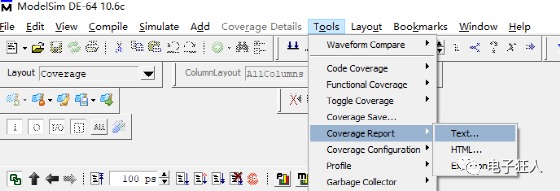

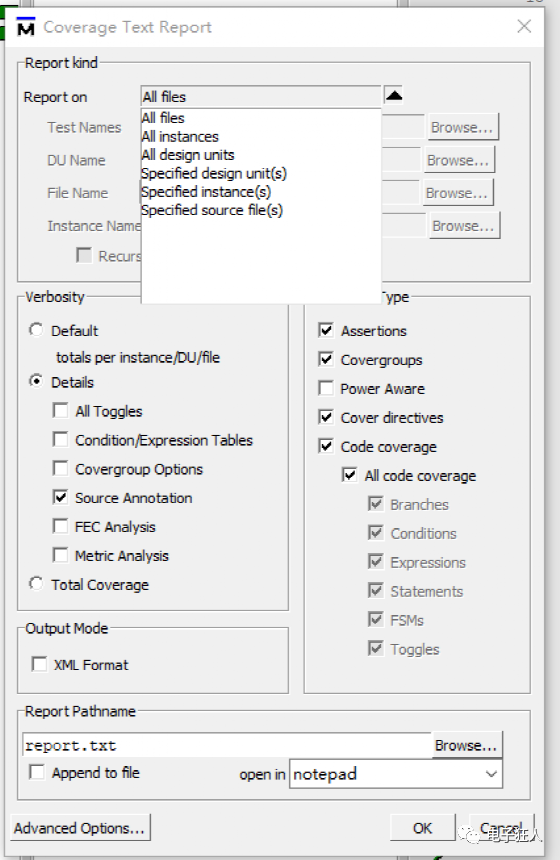

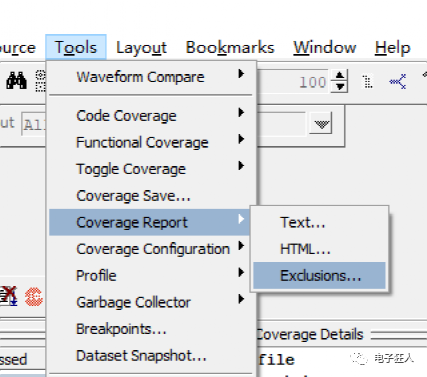

完成代码覆盖的测试后,可以将其导出,Tools > Coverage Report > Text ,类型就看自己需要了

(也可以在Instance, sim, files 界面右键找对应的导出键)

根据要的内容做报告

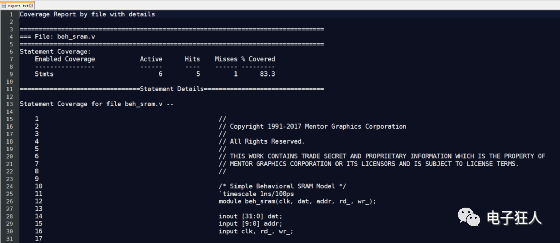

导出后,文件内容

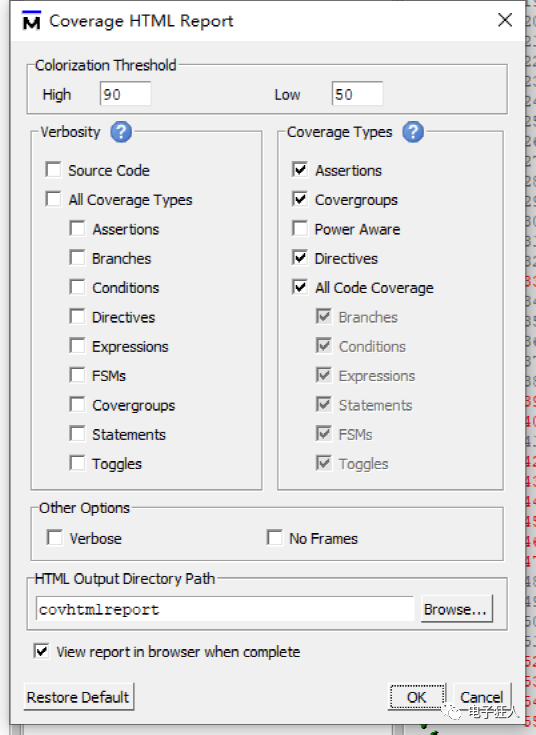

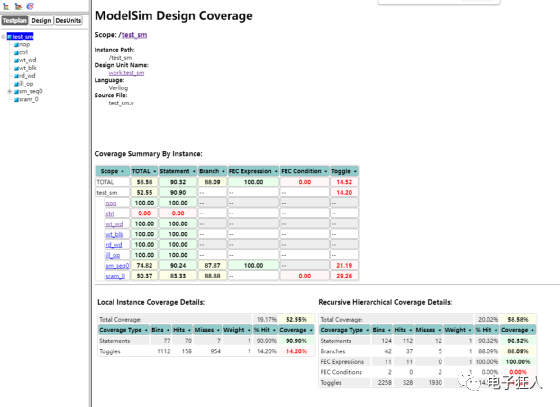

导出那个HTML就相对图形化显示

如果要把使用了排除覆盖测试的文件状态也导出,就可以用这个

基本就这样了,结束本次仿真吧~

quit -sim

-

仿真

+关注

关注

50文章

4094浏览量

133687 -

ModelSim

+关注

关注

5文章

174浏览量

47279 -

代码

+关注

关注

30文章

4793浏览量

68701

原文标题:Modelsim的仿真之路(代码覆盖率)

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Altera ModelSim 6.5仿真入门教程

Modelsim的功能仿真和时序仿真

使用 ModelSim 进行设计仿真详解

modelsim仿真详细过程(功能仿真与时序仿真)

仿真软件ModelSim及其应用,ModelSim的仿真流程

Modelsim仿真教程Modelsim的基础入门基础教程免费下载

Modelsim与MATLAB的联合仿真

基于ModelSim使用二联合Quarus自动仿真教程

Modelsim的仿真之路

Modelsim的仿真之路

评论