三级单元(TLC)、多级单元(MLC)、单层单元(SLC)、伪单层单元(pSLC)——有许多闪存技术。开发人员需要了解存储的基本机制和存储级别的效果,以了解哪些闪存产品最适合特定应用。只有这样,他们才知道该问供应商什么问题。

应用的不同方面可以决定嵌入式工业系统内存模块的选择。这些包括读写速度、耐用性(或闪存介质的使用寿命)、保留期(存储数据的生命周期)、断电时的数据安全性、耐温度和抗振性、产品的长期可用性等。NAND芯片的老化是一种特定于闪存的效果,在决策过程中也起着重要作用。

NAND闪存器件的单元只能承受有限数量的块擦除周期。在分离存储栅极的氧化层中,具有增加能级的电子(热电子)在被编程电压加速后被捕获。在适当的时候,这会改变阈值电压,直到电池不再可读。

闪光老化 – 何时结束?

还有第二种老化效应:通过氧化层形成导电路径。这导致电池逐渐失去其充电状态,从而失去存储的位。

高温会大大放大这种效应。使用25nm MLC NAND器件的研究表明,在55°C下五年后,保留率下降到约75%。在85°C时 - 相对适度的增加 - 保留率降至10%以下。

此外,随着时间的流逝,随着细胞越来越接近其最大程序擦除周期(P / E周期),效果会变得更强。这里对留存率的影响是巨大的。例如,低成本MLC NAND闪存器件的原始保持能力为10年,在达到3,000个P / E周期后可以下降到大约一年。

同样,低成本TLC NAND闪存芯片的充电状态和阈值电压挑战需要八个不同的可区分的电荷水平,以便每节电池写入三位。在这些设计中,退行性效应明显得多,原始的保留时间表在仅500个市盈率周期后从一年退化到三个月。

虽然更昂贵的SLC设备经历相同的退化,但在这些影响发生之前,必须发生大约100,000个P / E循环。显著较高的市盈率循环容差是SLC尽管成本较高,但其仍然是工业应用首选闪存技术的重要原因。

成本折衷方案:

引入pSLC工艺是为了平衡成本,并意识到减少不同电荷水平的数量使NAND芯片上的数据存储更加稳健。与SLC相比,pSLC为每个电池的第一个“强”位使用了更具成本效益的MLC芯片,并取得了一些惊人的结果。pSLC模式明显快于MLC闪存上的标准过程,并将退化前的P/E循环次数从3,000个增加到20,000个。在相同条件下,数据耐久性提高了 6.7 倍,而每存储成本仅为每比特成本的两倍。

耐久性规格注意事项:工作负载是决定性的

开发人员在选择存储设备时需要确切地知道制造商的规格代表什么。有两个测量值特别表明了 SSD 的耐用性:写入 TB 数 (TBW) 和每天驱动器写入数 (DWPD)。TBW 表示在设备的生命周期内总共可以写入的数据量,而 DWPD 表示在保修期内每天可以写入的最大数据量。

有时复杂的制造商规范的挑战在于,开发人员无法确定它们是否对所讨论的应用程序有任何意义。规格值在很大程度上取决于测试期间的工作负载类型。例如,来自瑞士比特的 480 GB 固态硬盘表现出 1,360 TBW、912 TBW 和 140 TBW 的耐用性,具体取决于测量过程。顺序写入产生的最强值为 1,360 TBW,而“客户端工作负载”和“企业工作负载”分别占第二和第三个值。客户端工作负载基于 PC 用户的行为,主要生成顺序数据访问操作,而企业工作负载模拟多用户服务器环境的行为,其中 80% 的数据被随机访问。

此类耐久性测试基于JEDEC标准化组织制定的指导方针,有助于确保产品和制造商的可比性。但是,工作负载规格通常不包括在数据表中。许多制造商乐于宣传基于仅在少数应用中使用的顺序写入的惊人耐力值。如上例所示,对于顺序写入和企业工作负载,闪存解决方案的耐久性值很容易相差 10 倍。买家必须谨慎行事。

受压闪存

记忆细胞的衰老通过擦除加速;但是,需要块擦除才能写入。这可能会导致一个欺骗性的结论,即在纯读取应用程序(如引导介质)中,由于数据保留时间延长,因此数据在长期内是安全的。不幸的是,这是一种误解。还有其他情况会导致读取错误,并间接导致NAND单元的磨损。

在每个写入过程中,与被编程单元相邻的细胞都会受到压力。这些显示电压略微增加,称为“程序干扰”。阅读也会引起压力“阅读干扰”,其中相邻页面收集电压。随着时间的推移,这些细胞中储存的电位增加。这会导致读取错误,在删除块后,读取错误会再次消失。由于电压较低,读取的效果比写入的效果弱,但仍然会发生位错误。这些在纠错码(ECC)中通过删除块进行补偿。

但是,开发人员仍然必须考虑,在重复读取相同数据的应用程序中,这种影响特别大,这意味着即使在仅用于读取的内存介质中,也必须删除块并定期写入页面作为纠错的一部分。因此,这种中等年龄也一样。

内部问题

这种中等老化会导致闪存设备的“内部问题”。擦除、写入和读取不仅由实际应用触发,还由众多控制器和固件进程触发。这里发生的事情往往被忽视,但会再次影响性能和耐力等性能因素。

除了纠错之外,这些内部机制中的另一种是磨损均衡。当一个单元发生故障时,必须将整个块标记为“坏块”。出于耐力目的,如果可能的话,推迟这种失败是很重要的。这可以使用磨损均衡来实现,磨损均衡是使用物理内存地址时的均匀分布。另一种内部机制是垃圾回收,即重新复制以释放块。

这些过程补充了使数据存储首先成为可能的机制:逻辑地址和物理地址之间的映射。闪存介质控制器的效率是通过来自主机的用户数据与写入闪存的实际数据值之间的比率来衡量的。这是使用写入放大因子 (WAF) 表示的。

减少 WAF 是延长耐久性的关键之一。存在影响 WAF 的工作负载因素,例如顺序访问和随机访问之间的差异、数据块相对于页面的大小以及块本身的大小。因此,固件还决定了闪存介质是否适合某个应用。

制造商如何提高效率

为了更好地理解,接下来是关于闪存工作原理的另一个讨论。必须连续对单元格块的页面进行编程,但只能删除完整的块。在标准流程中,逻辑地址和物理地址之间的映射是指块。这对于顺序数据非常有效,因为块的页面是连续写入的。连续收集的视频数据是应用实例的一个例子,其中基于块的分配是理想的。

对于随机数据,这是不同的。在这里,页面写在许多不同的块中。这意味着对于每次内部重新编程,每页必须删除一个完整的块。因此,WAF 很高,并且耐久性降低。因此,基于页面的映射更适合于非顺序数据。在这里,固件确保不同来源的数据按顺序保存在一个块的页面上。这减少了删除次数 - 对耐用性有积极影响 - 并且写入性能提高。但是,基于页面的映射会增加闪存转换层 (FTL) 的分配表。制造商通过集成的 DRAM 对此进行了补偿。因此,基于页面的映射的好处并非徒劳无功。

丰富的超额配置作为质量功能

如果数据介质的利用率迫使 WAF 上升,则基于页面的映射也是有益的。闪存介质上存储的数据越多,固件必须来回移动的位就越多。制造商能够通过简单的过度配置来防止数据介质过载的问题。这是指仅保留用于内部活动的闪存区域。传统上,这是总面积的7%,根据千兆字节规格,这是十进制值和二进制值之间的差异。

如果为过度配置保留了 12% 而不是 7%,则会产生令人惊讶的效果。对于具有相同硬件的两个 SSD 的耐久性比较(企业工作负载的 TBW),240 GB Swissbit 型号 X-60 durabit(保留 12% 的面积用于超额配置)实现的值几乎是 256 GB 机型的两倍。然后,如果看一下DRAM对耐用性的影响,240 GB硬脑膜版本的差异比256 GB的标准版本高出10倍(注意:正如使用MLC作为pSLC时已经实现的那样,通过放弃内存容量或应用过度配置可以达到显着的积极耐久性效果)。

数据维护

纠错和磨损均衡是通用闪存产品中也使用的机制。对于高质量的工业SDD或闪存卡,制造商进一步努力防止数据丢失和系统故障。因此,ECC监控、读取干扰管理和自动读取刷新等不同机制的组合可确保根据需要监控和刷新所有存储的数据。这样可以提前预防系统故障。(注意:应确保数据完整性,而不涉及主机应用程序。这允许进程在存储卡中自主运行 - 而不仅仅是当累积位错误跟随主机应用程序的读取请求时,通常就是这种情况)。

因此,高级数据维护管理独立于应用程序的请求搜索潜在错误。为此,所有写入的页面(包括固件和 FTL 的分配表)都将在后台读取并根据需要刷新。这种预防性纠错有各种触发因素,包括对市盈率循环次数、读取数据量、读取重复/重读以及温度升高的重复切换次数的定义数量。

知道要选择什么

了解闪存技术的不同方面是为工业应用选择最合适的存储解决方案的关键。当然,还应考虑电源故障保护机制、特别是稳健的处理以及扩展温度范围的规格等标准。

为特定应用程序指定的模块的长期可用性也很重要。这就是为什么一种类型的闪存 - 3D NAND - 在这里根本没有代表。这项技术仍然太新,无法确保长期可用性,创新周期和设计变更对于工业产品生命周期来说仍然过于临时。

最终,在选择工业存储技术的过程中,这些NAND闪存设备的耐用性和数据保留的经验值至关重要。优化这些值是工业闪存产品制造商的关键任务,客户应在购买前按压这些数字。

-

芯片

+关注

关注

456文章

50967浏览量

424978 -

闪存

+关注

关注

16文章

1794浏览量

115000 -

NAND

+关注

关注

16文章

1685浏览量

136257

发布评论请先 登录

相关推荐

工业环境中的测距与定位应用解决方案

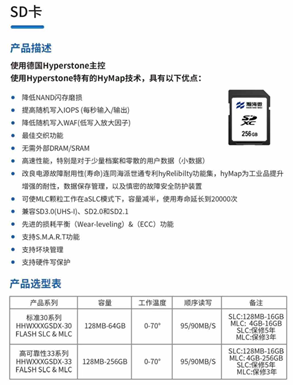

工业SD卡:专为严苛环境设计的高端存储设备

工业园区智慧照明物联网解决方案

e络盟携手Flexxon,拓展先进工业级存储解决方案的全球分销网络

emc存储解决方案的优势

液氮罐运输和存储温度监测解决方案

DigiKey 宣布与内存和存储解决方案领导者之一的 Kingston Technology 建立全球合作伙伴关系

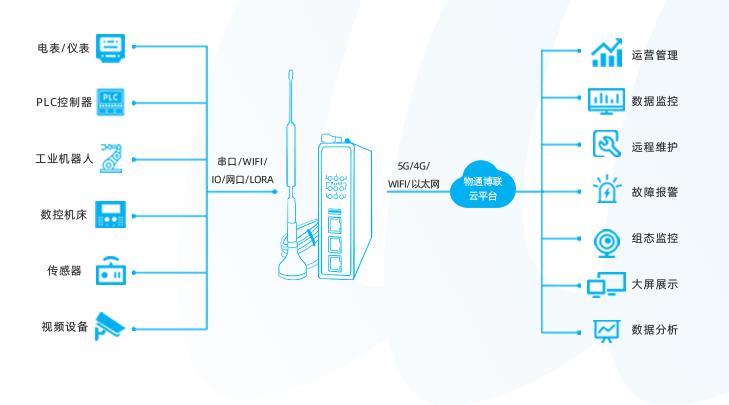

基于工业网关和云平台的工厂设备数据采集解决方案

工业物联网解决方案有什么用

罗彻斯特携手Intelligent Memory提供传统DRAM和NAND存储解决方案

开放式高实时高性能PLC控制器解决方案-基于米尔电子STM32MP135

NVMe Host Controller IP实现高性能存储解决方案

广和通AI解决方案“智”赋室外机器人迈向新天地!

逐步迈向工业存储解决方案

逐步迈向工业存储解决方案

评论