简介

时钟是芯片正确高效运行的基础,正确的时钟配置是芯片能正确运行的必要条件,其重要性不言而喻。AT32各系列产品的时钟配置部分可能存在细微的差异和需要注意的事项,本文档就着重针对各系列的情况来详细介绍如何结合雅特力提供的V2.x.x的板级支持包(BSP)来配置时钟。

以下介绍时钟配置的方法主要分两种:

1、以手动编写代码调用BSP中提供的驱动函数接口来进行时钟配置。

2、采用时钟工具来配置并生成相应的源码文件。

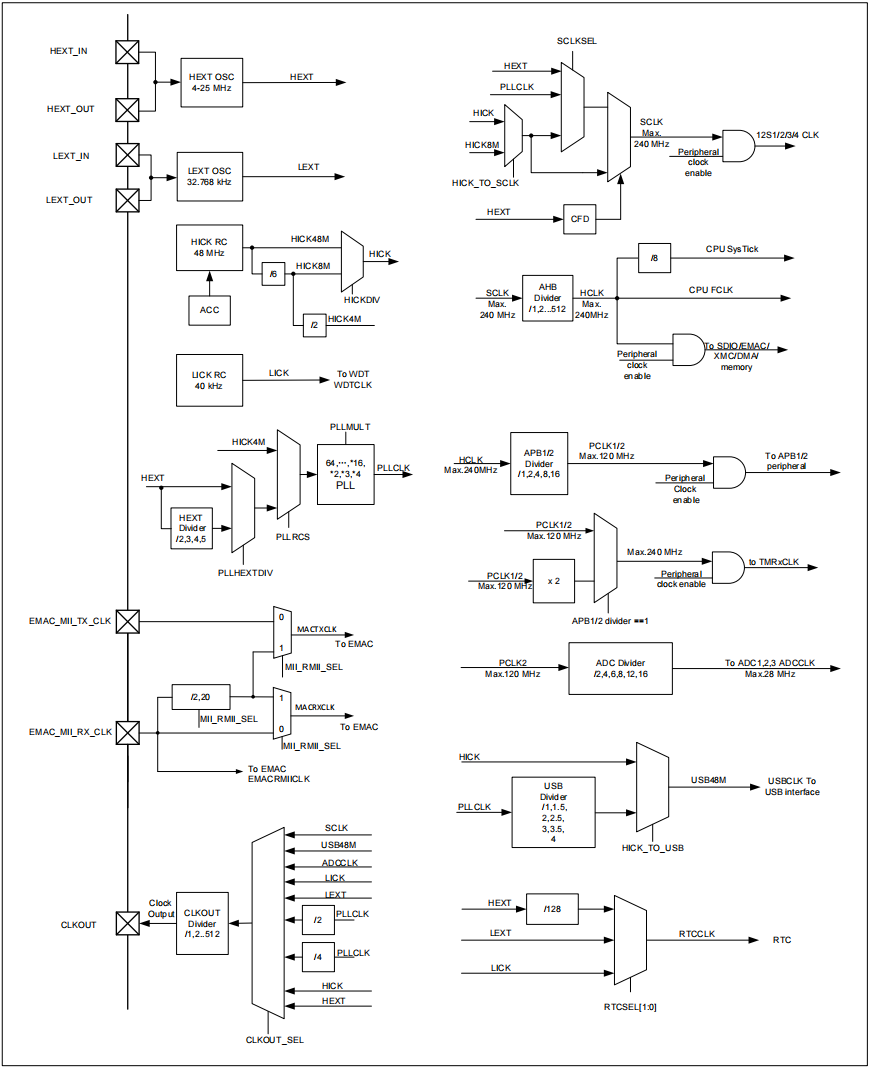

时钟树

在进行时钟配置之前,应充分了解对应芯片的时钟树结构,这样在进行时钟配置时才会游刃有余。对于系统时钟频率及路径的配置我们需要关注时钟源、倍频及系统时钟部分。类似如下图:

图1. 时钟框图

可由图中得到以下几个关键信息:

1) SCLKSEL:系统时钟可以由HEXT、PLLCLK、HICK三大时钟源提供。

2) HEXT:HEXT是外部高速时钟,其可以外接范围是4~25 MHz的晶振或时钟源。

3) HICK:HICK RC是内部高速振荡器,频率为48MHz。HICK时钟由内部振荡器给出,但在初始情况下由HICKDIV控制并默认6分频后为8MHz,亦可配置为不分频,保持48MHz的频率。

4) PLLCLK:PLL时钟=PLL输入时钟*PLL倍频系数。

5) PLL输入时钟:PLL的输入时钟由PLLRCS及PLLHEXTDIV共同决定,其细分可分为三个来源:HICK 4MHz、HEXT和HEXTDIV,HEXTDIV由HEXT分频系数决定,默认为2分频。

代码配置解析

以下将以库函数接口为核心来对时钟配置流程和方法进行说明。

函数接口

各系列产品对应提供的BSP中对硬件的时钟设置部分已封装好接口函数以供调用,以下罗列出时钟配置常用的函数接口,各函数的具体参数及返回值类型等请参考at32f403a_407_crm.c/.h文件。

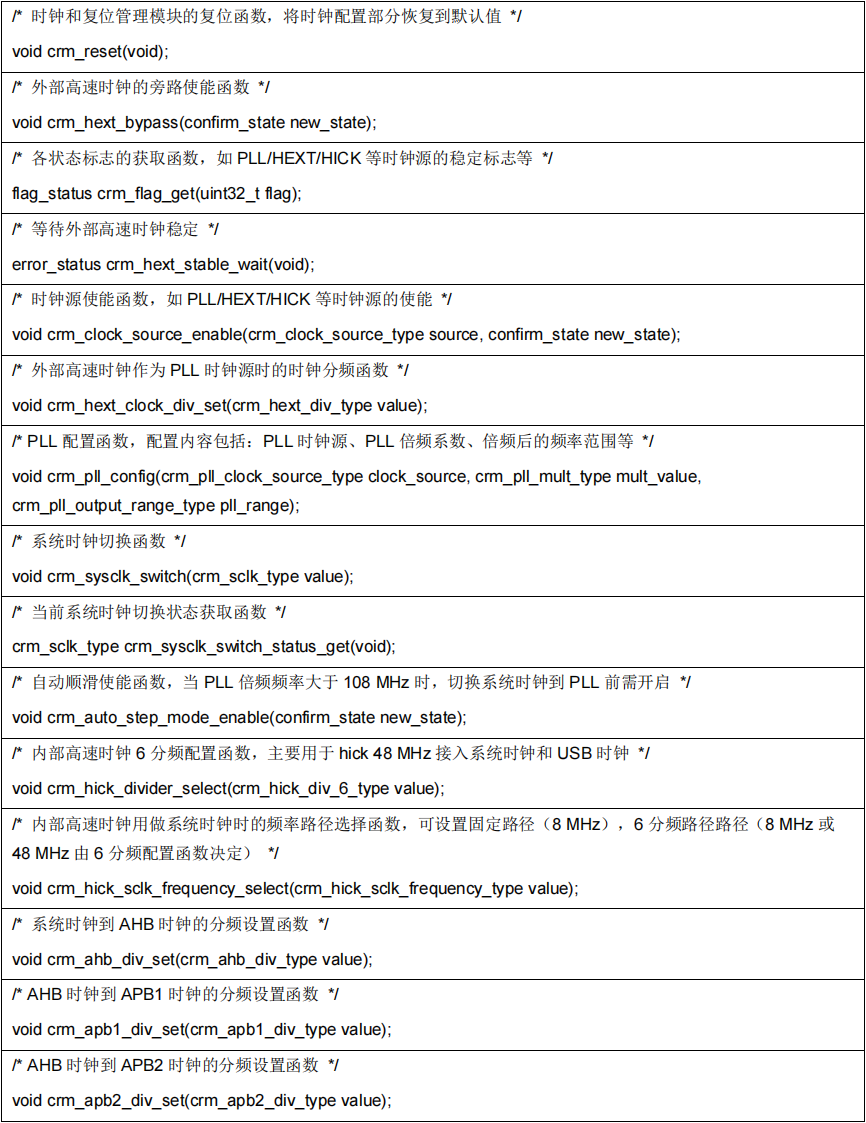

时钟配置流程

按常规应用来讲解时钟配置流程,其内容可大致分为如下步骤:

图2. 时钟配置流程图

复位(CRM Reset)

首先按规范流程应复位CRM配置参数,其主要是将系统时钟切换到HICK,其余的系统时钟配置寄存器写入默认值,待后续进行新配置参数的写入。函数调用的代码实现如下:

时钟源配置(Clock Source Configuration)

与系统时钟相关的高速时钟源主要包括HEXT和HICK,PLL也是使用以上时钟源来进行倍频。需要在配置使能PLL前将所使用的PLL参考时钟源开启并等待其稳定。

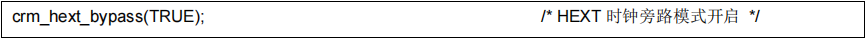

HEXT

外部高速时钟如采用外接有源时钟的方式时,可开启旁路模式来进行使用,采用晶振时,不能开启旁路模式,旁路模式应在外部高速时钟源使能前进行设定,其默认情况为关闭。旁路模式使能代码实现如下:

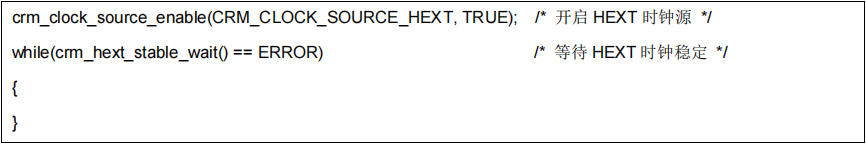

使能HEXT时钟源并等待HEXT时钟稳定,代码实现如下:

HEXT

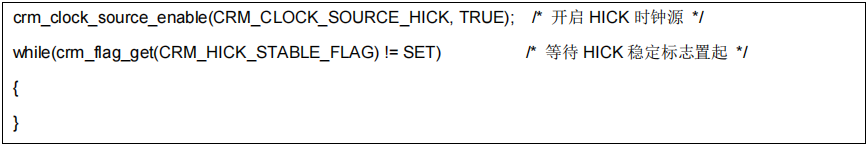

内部高速时钟是由芯片内部振荡器提供,使能HICK时钟源并等待HICK时钟稳定,代码实现如下:

PLL配置(PLL Configuration)

PLL配置主要包括:PLL时钟源、PLL倍频系数、PLL倍频频率范围等的设置。倍频时钟公式为: PLLCLK=PLL输入时钟*PLL倍频系数。

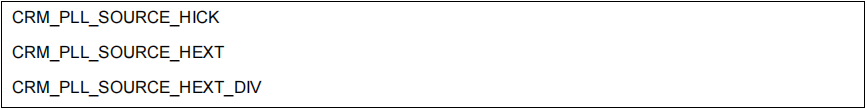

PLL时钟源

PLL时钟源细分有三个来源:1、HICK(4 MHz),2、HEXT,3、HEXT分频时钟,PLL时钟源应在PLL配置使能前开启并等待稳定。以上PLL时钟源在crm_pll_config函数中对应的参数定义如下:

当选择PLL时钟源为CRM_PLL_SOURCE_HEXT_DIV时,HEXT的分频系数可以通过函数crm_hext_clock_div_set进行设置,其默认分频系数为2分频。

PLL倍频系数

倍频系数为2~64倍可选,但应该注意最高主频限制,以此按实际情况来合适选择倍频系数,如8倍频使用参数CRM_PLL_MULT_8。

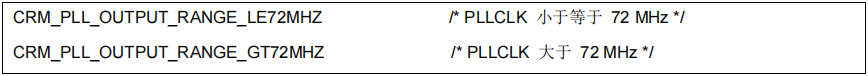

PLL频率范围

频率范围主要以倍频后的PLLCLK频率来做设定,其范围参数以72MHz为界限设定,如下:

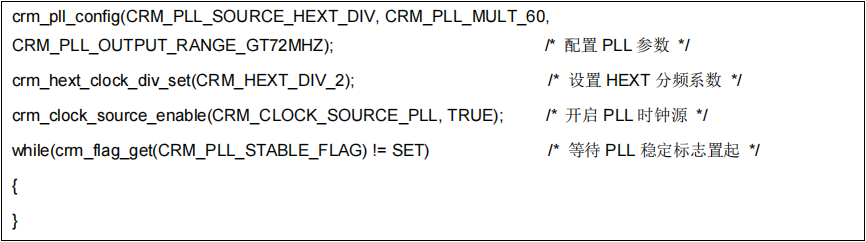

当PLL参数设置完成后,即可开启PLL并等待PLL稳定。示例:外部时钟晶振8MHz,采用HEXT2分频时钟作为PLL时钟源,PLLCLK倍频到240MHz的代码实现如下:

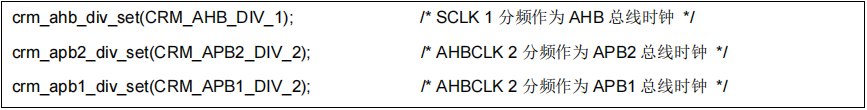

总线分频(Set Bus Frequency Division)

总线分频包含SCLK到AHBCLK分频、AHBCLK到APB1CLK分频、AHBCLK到APB2CLK分频。AHB总线1分频、APB1/APB2总线2分频的代码实现如下:

切换系统时钟(Switch System Clock)

系统时钟来源主要有三个:HICK、HEXT、PLLCLK。在切换系统时钟到如上时钟源时应提前确保对 应时钟源已稳定。

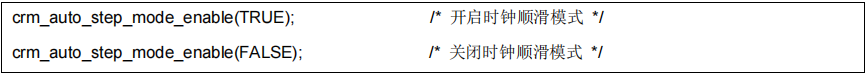

顺滑模式

时钟顺滑模式是为了确保整个系统时钟切换过程的稳定而设计,当即将切换为系统时钟的目标时钟频率大于108MHz时应开启时钟顺滑模式,所以其主要应用对象为PLLCLK用作系统时钟时的场景。通常使用方法是在系统时钟切换前开始,切换成功后关闭。代码实现如下:

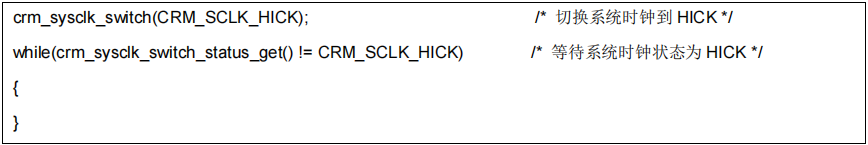

HICK系统时钟

内部高速时钟在系统复位重新运行时默认作为系统时钟,后期代码进行设定时,可有两种频率值来进行设定(8MHz和48MHz)。如图1所述HICK默认情况下用的是8MHz,可配置为48 MHz。HICK 8MHz用作系统时钟的代码实现如下:

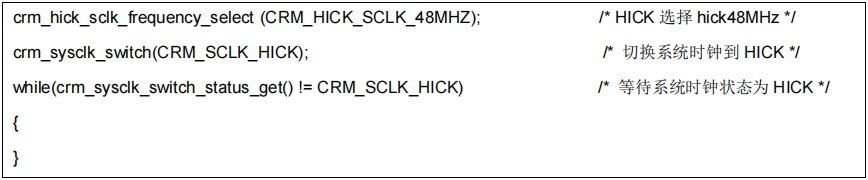

HICK 48 MHz用作系统时钟的代码实现如下:

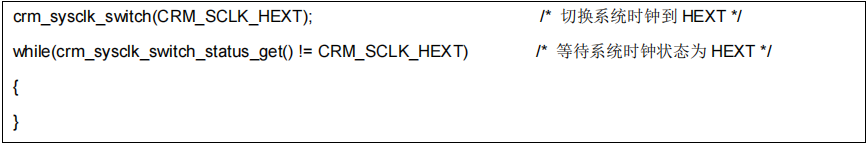

HEXT系统时钟

外部高速时钟用作系统时钟时,其系统时钟频率以实际使用的外部时钟频率为准,范围为4~25MHz。HEXT用作系统时钟的代码实现如下:

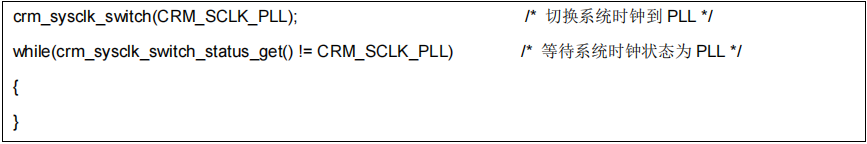

PLLCLK系统时钟

PLLCLK用作系统时钟时,其系统时钟频率以实际的PLL倍频结果为准。其最高频率应满足芯片规格为基础。PLLCLK用作系统时钟的代码实现如下:

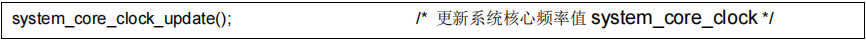

更新核心频率(Update Core Frequency)

提供的BSP中,其代码框架内保留了一个表示系统核心频率的参数值system_core_clock,其保存的是CPU核心的运行频率值,应该在每次系统时钟配置完成后来进行更新。为的是在整个代码框架下,各外设驱动的频率配置能很快获取到当前核心运行频率值并使用。代码实现如下:

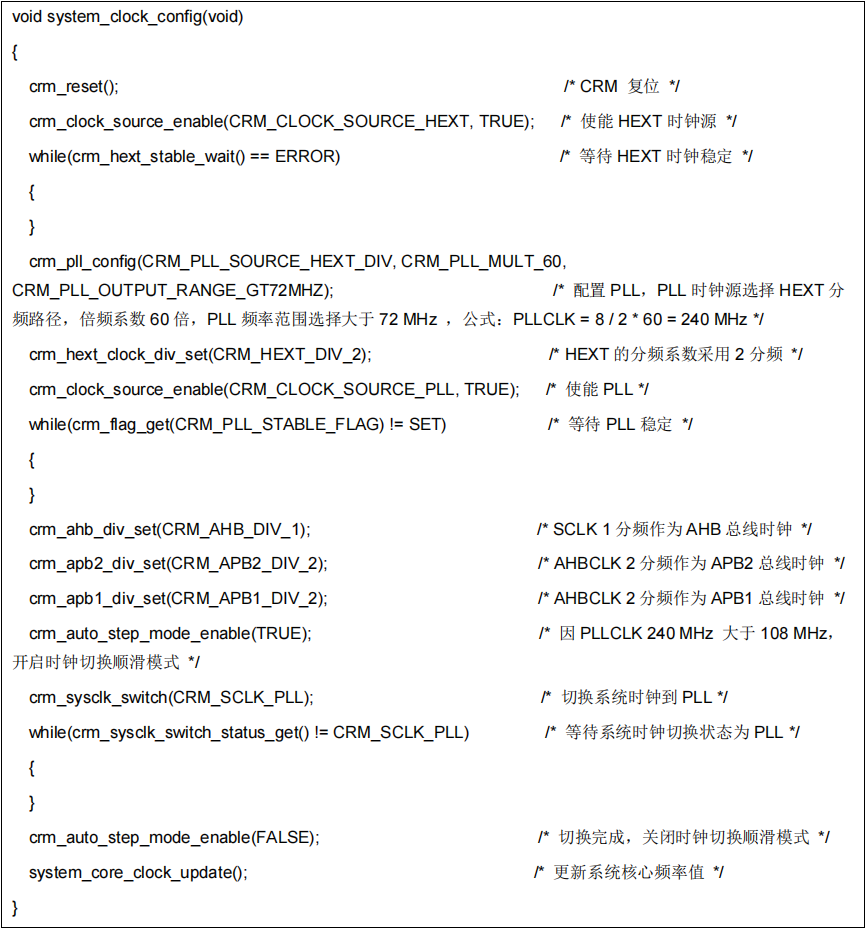

时钟配置示例

以下将以完整的时钟配置流程来进行说明,示例:由8MHz外部时钟晶振作为时钟源,其2分频路径经PLL倍频到240MHz并用做系统时钟,AHB不分频,APB1/APB2采用2分频。函数system_clock_config代码实现如下:

时钟工具

时钟配置工具是雅特力科技为方便对AT32系列MCU进行时钟配置而开发的一个图形化配置工具,其主旨是使用户清晰了解时钟路径和配置出期望的时钟频率并生成源码文件。

环境要求

软件要求

需要Windows7及以上操作系统支持。

安装

软件安装

本软件不需要安装,只需直接运行可执行程序AT32_New_Clock_Configuration.exe。

功能介绍

本章节将介绍此工具的基本操作,其主要的启动界面和配置界面如下所示

图3. 启动界面

图4. 配置界面

菜单栏

菜单栏内容如图所示:

图5. 菜单栏

“项目”(Project)菜单:

新建:新建时钟配置项目 打开:打开已存在的配置项目 保存:保存已打开的配置项目

“语言”(Language)菜单:

English:选择English作为显示语言 简体中文:选择简体中文作为显示语言

“生成代码”(General code)菜单:

当在对应型号的操作配置界面将所期望的时钟路径和时钟频率配置完成之后,可点击“生成代码”菜单来选择源码文件的存储路径并生成相应的源码文件。

“帮助”(Help)菜单:

新版本下载:联网进行新版本下载 版本:查看当前版本

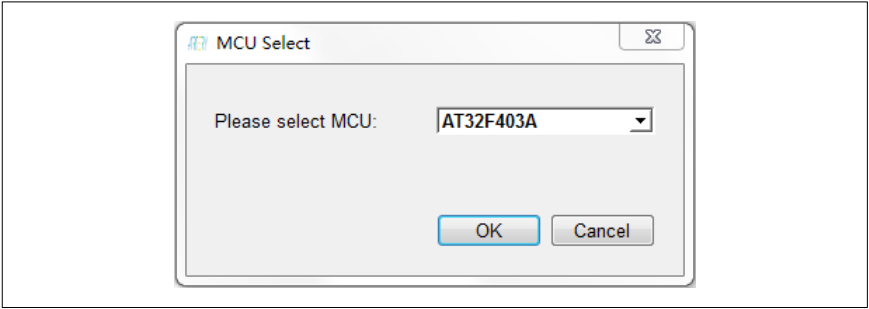

新建配置项目

双击打开时钟配置工具,可看到图示的启动界面,可点击“项目”菜单-->“新建”,进行配置项目的新建,在新建配置项目的过程中需要对芯片的系列所属进行选择,操作方法如下图所示

图6. MCU选择界面

MCU系列的选择,可点击下拉框来进行选择,当选择好MCU后点击“确定”可进入到时钟配置界面。

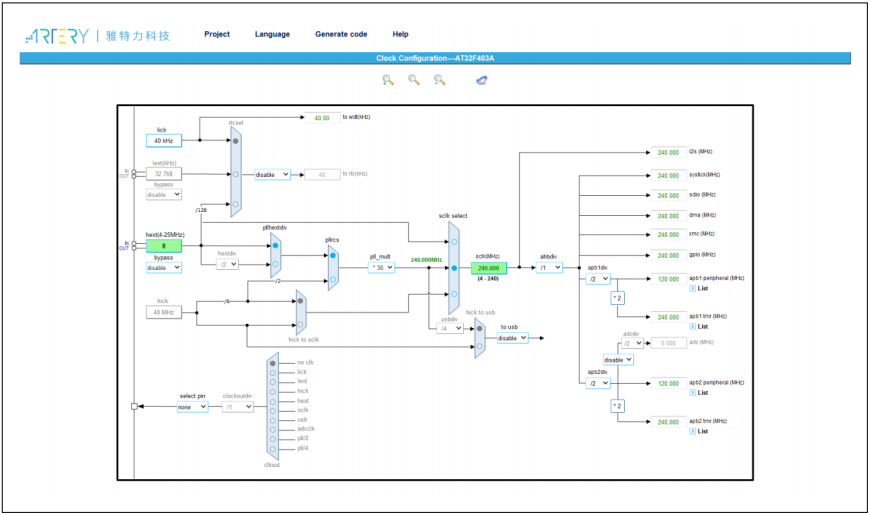

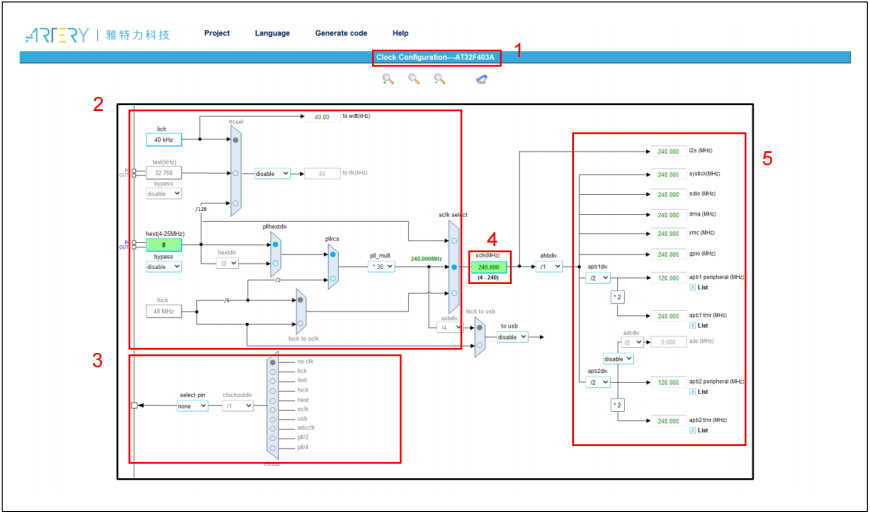

配置界面的使用

配置界面主要用来进行时钟路径及参数的配置,以下的介绍将以 AT32F403A 系列作为示例来展开进行,其余系列的配置方法与此类似。

整个配置界面主要可以分为四个大块,如下图所示

图7. 配置界面框架

1. 标题部分:用于展示当前配置项目所选择的MCU系列。

2. 配置部分:用于对时钟路径和时钟参数进行选择和配置,以达到期望的应用需求。

3. 输出部分:用于时钟输出(CLKOUT)的配置。

4. 在SCLK栏也可在选中PLL为系统时钟时作为输入框,可输入期望的系统时钟频率来反向自动配置出倍频参数。

5. 结果部分:用于显示当前外设所使用的时钟频率及总线上的外设。

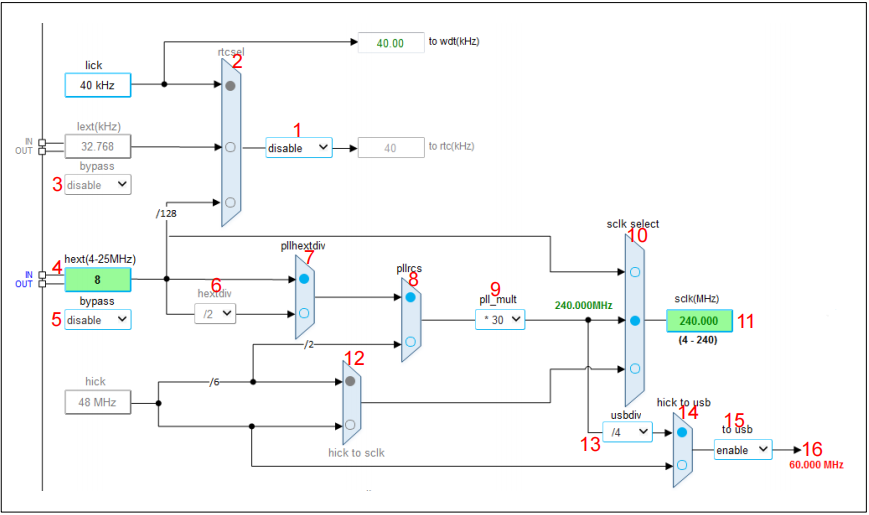

接下来就着重介绍一下配置部分的使用。配置部分的流程界面是对应着MCU时钟树来进行的,各系列MCU的此部分可能存在着差异,但使用方式大同小异。时钟路径的配置可按流程对各开关进行点选来进行选择,配置部分如下图所示,将逐个流程点的功能及其注意事项进行介绍。

图8. 时钟配置框

1. rtc使能:rtc时钟代码配置的使能下拉框。

2. rtcsel:点选框,rtc时钟源选择。当rtc使能开启后,此点选框可配置。

3. lext bypass:外部低速时钟的旁路使能。

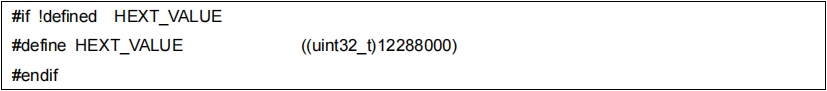

4. hext:此为输入框,8MHz为所采用外部时钟源的默认频率,用户可根据实际使用的外部时钟源频率进行修改。(注:此8MHz被修改为其他频率值时,对应的BSP中demo目录下的inc/at32f403a_407_conf.h文件内的HEXT_VALUE宏定义也应该一致修改,也可以采用工具生成的at32f403a_407_conf.h文件来进行使用)。

5. hext bypass:高速外部时钟的旁路使能。

6. hextdiv:下拉框,当HEXT的分频路径作为PLL时钟源时,可配置输入源HEXT的分频系数。

7. pllhextdiv:点选框,当HEXT作为PLL时钟源时,可配置输入频率为HEXT分频或HEXT不分频。

8. pllrcs:点选框,可配置PLL时钟源为HEXT或HICK。

9. 倍频系数:使用PLL_MULT参数进行倍频,计算公式为:PLLCLK=PLL输入时钟*PLL_MU LT。为了用户的使用方便,在选定PLL输入时钟源后,结果部分的sclk框中输入目标时钟并按下键盘“Enter”键,会自动计算一组倍频参数以满足用户期望或相近的时钟频率。 10. sclk select:点选框,可配置HEXT、PLL或HICK作为系统时钟。

11. sclk频率:当采用正向配置时,此作为系统时钟频率的配置结果显示,当将其用作输入框时,输入期望的频率后点击回车键,会根据此输入值反向计算一组合适的或最接近期望值的PLL配置参数。

12. hick to sclk:点选框,当sclk select选择HICK作为系统时钟时,可配置HICK的8MHz或48MHz到系统时钟(注:当选择48 MHz HICK到系统时钟后,CLKOUT输出HICK时的频率也为48MHz)。

13. usbdiv:下拉框。当PLL时钟被选作为USB的时钟来源时,此处配置PLL时钟到USB时钟的分频系数。

14. hick to usb:点选框,可配置USB时钟由PLL时钟或HICK 48 MHz提供,USB时钟配置代码由下拉框to usb来进行选择控制。因USB时钟需要的是固定48MHz,所以在usbdiv可分频参数为前提下,PLL倍频出来的频率可能不满足USB 48 MHz的时钟需求。

15. USB使能:USB时钟代码配置的使能下拉框。

16. USB时钟频率的显示。此显示栏会实时计算USB时钟的频率并显示,如果配置出来的USB时钟不等于48MHz时,显示出来的USB时钟频率会标注为红色,而实际应用中没有用到USB时选择disable则不会显示。

(注:此部分只针对USB时钟频率的配置,USB外设时钟使能需自行额外打开)

生成代码

当时钟配置完成后,可点击生成代码,然后选择代码生成的路径并确认,最后会在所选目录下生成两个文件夹inc和src,源文件存放在src文件夹下,头文件存放在inc文件夹下。这些文件可结合到BSP_V2.x.x内的工程来进行使用。可以采用新生成的时钟代码文件(at32f4xx_clock.c/at32f4xx_clock.h/ at32f4xx_conf.h)将原BSP demo中的对应文件替换,在main函数中进行system_clock_config函数调用即可。

注意事项

外部时钟源(HEXT)修改

因本文档所示例的demo和配置工具都默认采用的8MHz外部时钟频率,当实际硬件使用的外部时钟源是非8MHz频率时需注意以下几点。

代码修改

1、以实际的外部时钟频率按文中时钟配置流程章节所描述的时钟配置流程及方法来编写相应的代码,配置出期望的时钟配置及时钟路径。

2、修改对应demo工程中at32f4xx_conf.h文件的HEXT_VALUE值,以实际使用的外部时钟源频率值来进行修改。如实际外部高速时钟使用12.288MHz的晶振或时钟源时,at32f4xx_conf.h文件应修改如下:

工具修改

1、在时钟配置工具中的HEXT输入框内填入外部时钟源实际频率值并按“Enter”键确认。

2、配置好所需的时钟路径及时钟频率,生成代码。采用新生成的时钟代码文件(at32f4xx_clock.c/at32f4xx_clock.h/at32f4xx_conf.h)将原BSP demo中的对应文件替换或取其中函数内容进行替换,在main函数中进行system_clock_config函数调用即可。

工具使用

在使用本时钟配置工具时需注意:

1. 此工具生成的时钟配置源码文件需结合雅特力科技提供的BSP_V2.x.x进行使用。

2. 不同系列所生成的时钟配置源码文件不能型号混用,只能在相对应的工程项目中进行调用。 3. 配置工具中各输入框参数修改后,请以“Enter”键结束。

案例 系统时钟

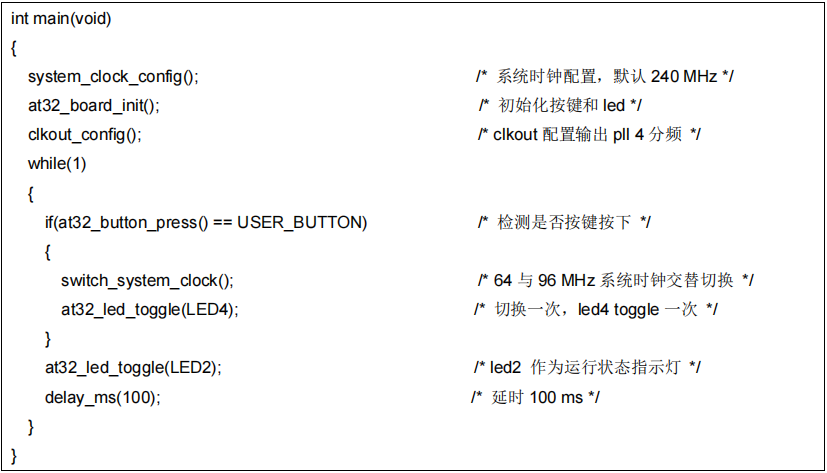

功能简介

在系统运行过程中来进行系统时钟切换。

资源准备

1) 硬件环境 对应产品型号的AT-START BOARD 2) 软件环境 projectat_start_f403aexamplescrmsysclk_switch

软件设计

1) 配置流程

初始化按键。

配置clkout时钟输出pll 4分频。

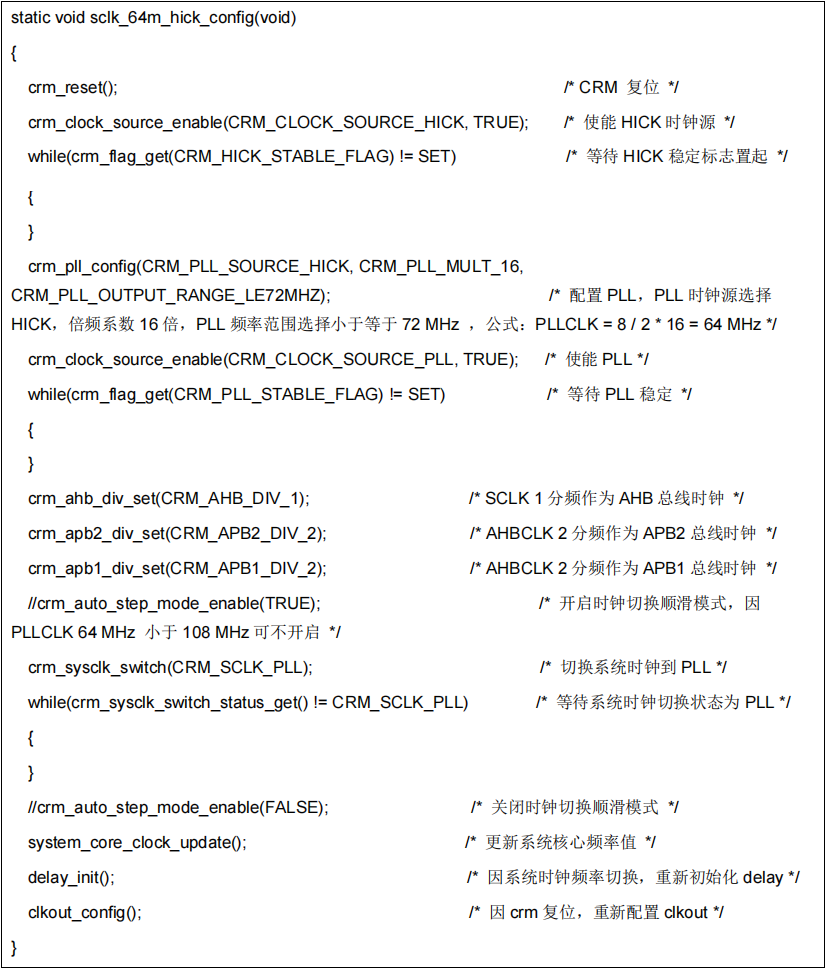

编写从hick经pll倍频64MHz到系统时钟的配置代码。

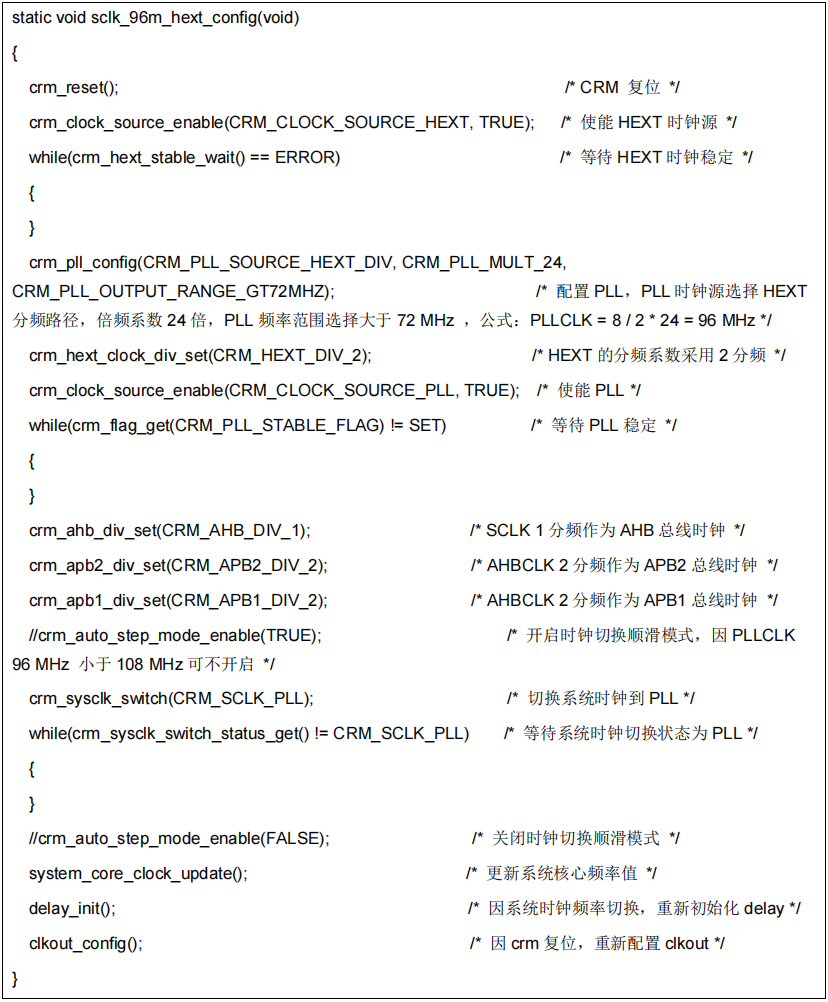

编写从hext 2分频经pll倍频96MHz到系统时钟的配置代码。

2) 代码介绍

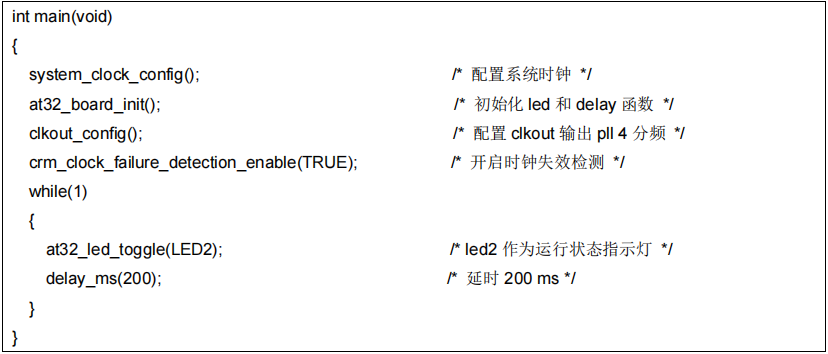

main函数代码描述

hick经pll倍频64MHz到系统时钟的代码描述

hext 2分频经pll倍频96MHz到系统时钟的代码描述

实验效果

上电运行led2以间隔100ms时间进行闪烁,clkout(PA8)输出60MHz。

每次USER按键按下,系统时钟在64MHz与96MHz之间进行交替切换,clkout输出对应的4分频频率,led4 toggle一次。

案例 时钟失效检测

功能简介

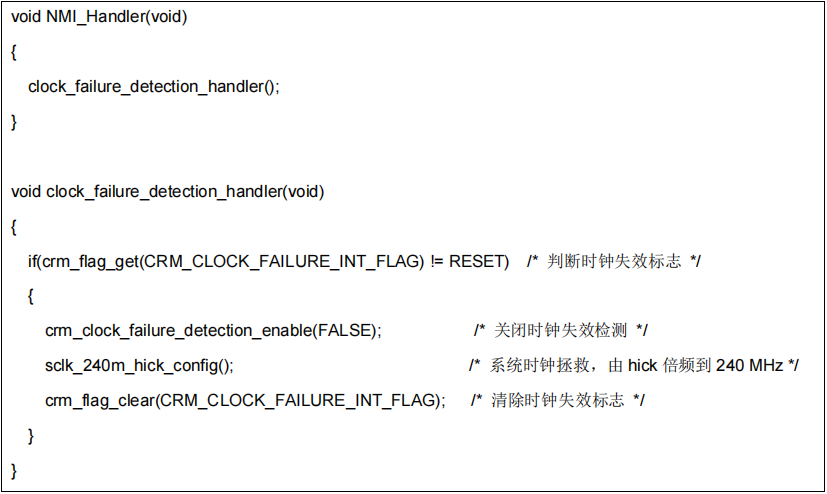

在当HEXT时钟直接或间接作为系统时钟时,当HEXT时钟出现故障,且时钟失效模块侦测到失效后,时钟失效事件将产生NMI中断,在此中断中可完成系统的营救操作。

资源准备

1) 硬件环境 对应产品型号的AT-START BOARD 2) 软件环境 projectat_start_f403aexamplescrmclock_failure_detection

软件设计

1) 配置流程

配置clkout时钟输出pll 4分频。

开启时钟失效检测,并完善void NMI_Handler(void)函数。

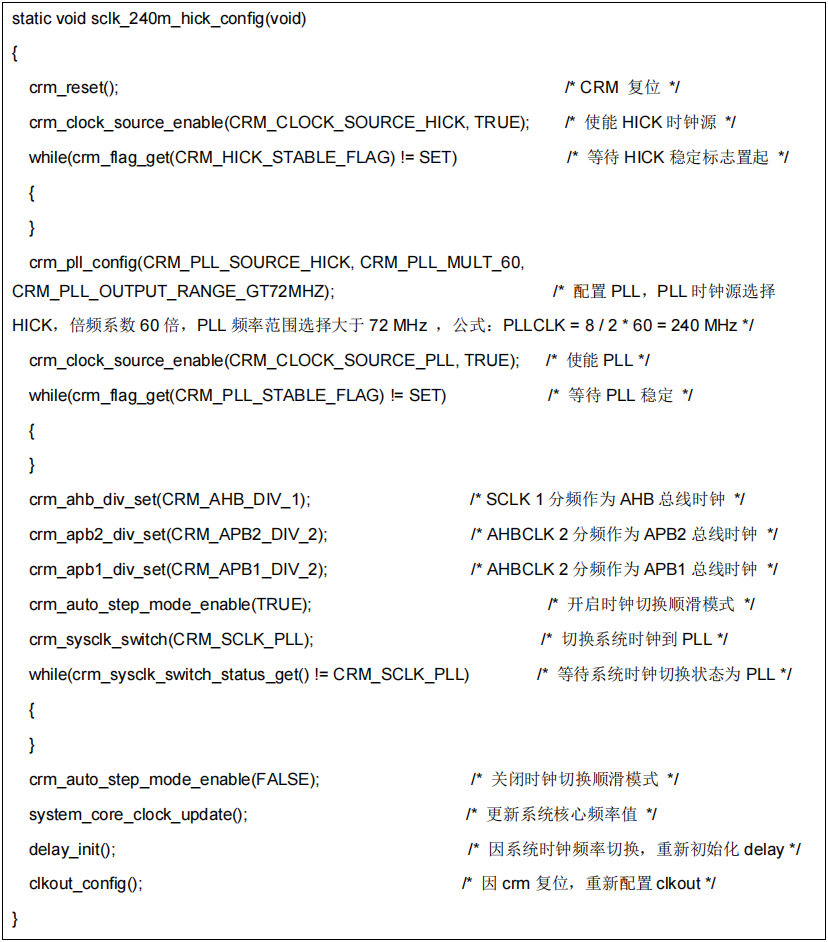

编写从hick经pll倍频240MHz到系统时钟的配置代码。

2) 代码介绍

main函数代码描述

hick经pll倍频240MHz到系统时钟的代码描述

NMI中断实现

实验效果

在运行过程中将晶振拔掉或晶振脚接地,产生时钟失效。通常来说hext比hick更稳定,可观测clkout(PA8)的输出,可发现时钟拯救回来后hick作为源时的频率上存在细微波动。

审核编辑:汤梓红

-

pll

+关注

关注

6文章

774浏览量

135044 -

时钟

+关注

关注

10文章

1720浏览量

131360 -

AT32

+关注

关注

1文章

113浏览量

2072

原文标题:AT32讲堂033 | AT32F403A/407时钟配置指南

文章出处:【微信号:AT32 MCU 雅特力科技,微信公众号:AT32 MCU 雅特力科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AT32F403A如何使用DMA弹性映射?

AT32F403A的相关资料下载

利用AT32F403A驱动复用PSRAM的步骤有哪些呢

怎么把AT32F403A芯片的串口配置成DMA接收呢

AT32F403A/407 ADC 使用指南(附pdf)

AT32F413/AT32F415/AT32F403A/AT32F407引脚复用说明

AT32F403A & AT32F407入门使用指南

AT32F403A/407系列安全库区的应用原理、软件使用方法及范例程序

AT32F403A/407 GPIO应用说明

AT32讲堂033 | AT32F403A/407时钟配置指南

AT32F403A/407时钟配置指南

AT32F403A/407时钟配置指南

评论