前几天,看到一个比喻,说锁相环是一个电路的心脏,没有它,整个电路都工作不了了。

想想也是,没有锁相环,混频器没法变频,ADC没法采样,确实很重要。

实际的PLL电路肯定相当复杂,不过,可以从简单的看起。

一个最最简单的PLL,有三部分组成,VCO,鉴相器(PD)和低通滤波器。

这篇文章呢,就先讲讲鉴相器的原理。

鉴相器(Phase Detector/PD)

鉴相器,英文名为Phase Detector,简称PD。

Phase Detector直译过来为相位检测器,读上去好像比鉴相器通俗一点哦。

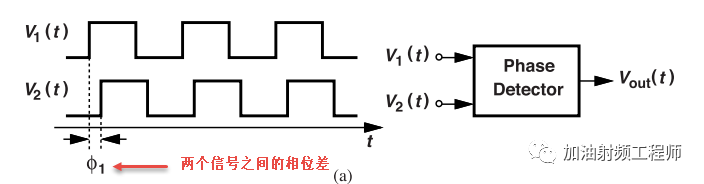

相位检测器,就如其字面意思,就是检测相位用的。不过呢,它是对两个信号的相位差做出反应。也就是说,它不管你相位的绝对值,它是比较两个相位的相对值。相位检测器的输出呢,一般是一个电压,而且这个电压与相位差呈线性关系。如下图所示。

它的主要工作时用来测量两个信号之间的相位差,然后输出一个参量,比如说电压。而这个电压与相位差呈线性关系。

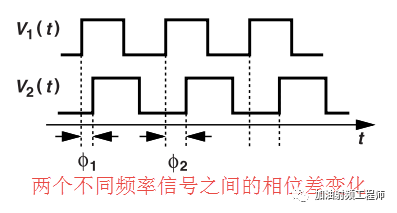

如果V1(t)和V2(t)的频率不相等的话,两者的相位差则会随时间发生变化。如下图所示。

PD怎么实现呢?

那上述的功能怎么用电路实现出来呢?

异或门

或许你想不到,一个简单的异或门(XOR)就可以实现上面的功能。当然,实际电路可能比这个复杂,这个等我了解到了,再谈。

目前,先从原理层面上看看。

异或门的真值表如下:

换成文字描述就是:当两个输入相同时,输出为0;当两个输入不同时,输出为1.

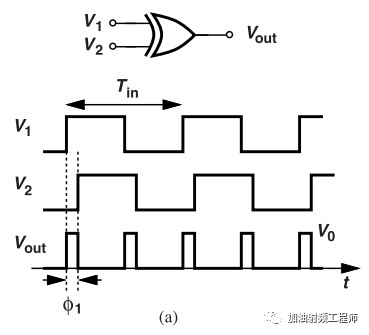

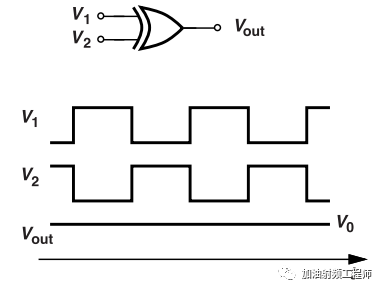

异或门当做PD来使用时,其工作原理如下图所示。

如上图所示,两个方波信号V1和V2,而V2的相位比V1滞后,即V2的变化沿要比V1的来的晚一点。

在一个周期内,V1和V2会有一段时间,电平不一致。

当V1和V2经过异或门时,两者电平不同时,异或门输出高;当两者电平相同时,异或门输出低。这样,异或门就将V1和V2的相位差,与电压输出连接起来了。

输出Vout是一系列的脉冲信号,因为上升沿处要高一次,下降沿处要高一次,所以该脉冲信号的频率是输入信号的2倍。

脉冲宽度与信号之间相位差的大小成正比关系,也就是说,相位差大,脉冲宽;相位差小,脉冲窄。

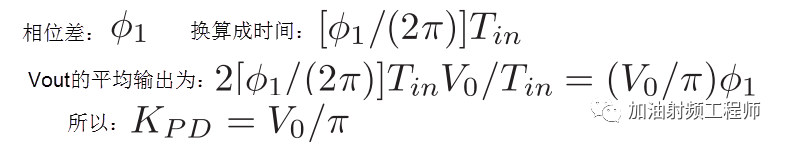

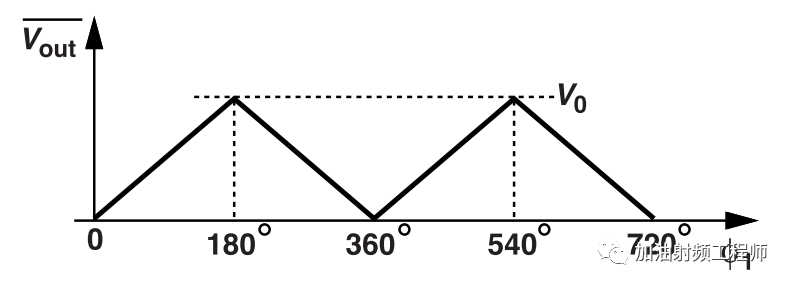

脉冲信号的平均值如下图所示,与相位差线性相关。

当V1和V2相差180度时,这时Vout的输出恒定为1, 此时Vout的平均值最大。

当V1和V2的相位差超过180度时,Vout的平均值开始线性下降。

因此,当XOR作为PD时,其输入输出的特性曲线如下图所示。

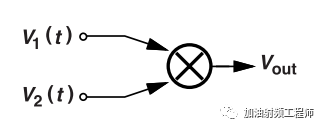

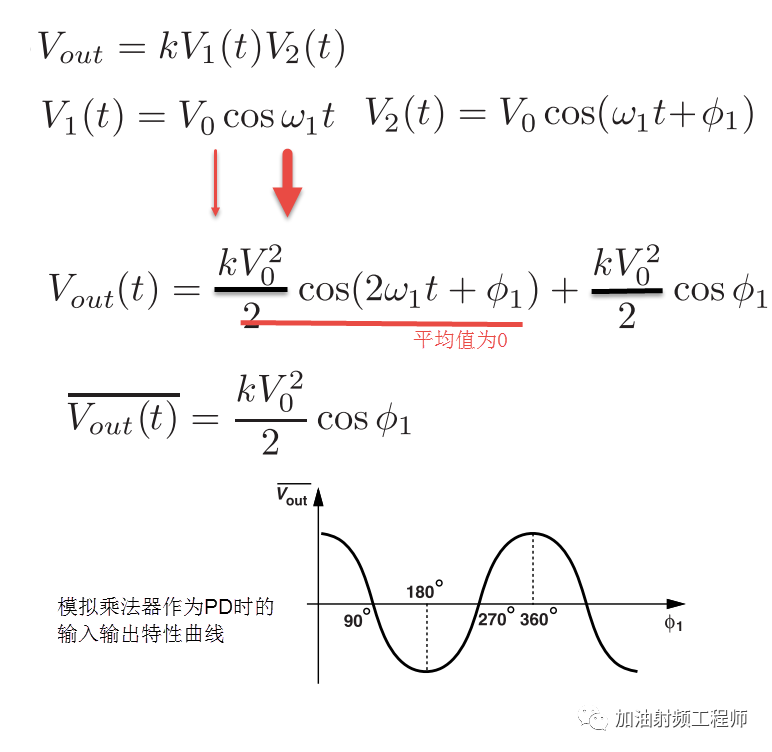

另外,模拟乘法器(或者混频器),也可当成PD来使用。想不到吧?

其输入输出特性曲线如下图所示。

审核编辑:汤梓红

-

锁相环

+关注

关注

36文章

637浏览量

91318 -

adc

+关注

关注

100文章

7950浏览量

557040 -

鉴相器

+关注

关注

1文章

63浏览量

23928

原文标题:锁相环中的鉴相器了解不?

文章出处:【微信号:加油射频工程师,微信公众号:加油射频工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

MAX9382在锁相环中的应用

锁相环中的鉴相器了解不?

锁相环中的鉴相器了解不?

评论