注意示波器的探头和示波器本身的带宽能够满足测试要求。

测试点的选择要注意选到尽量靠近信号的接受端。由于 DDR 信令比较复杂,因此为了能快速测试、调试和解决信号上的问题,我们希望能简单地分离读/写比特。

此时,最常用的是通过眼图分析来帮助检查 DDR 信号是否满足电压、定时和抖动方面的要求。触发模式的设置有几种,首先可以利用前导宽度触发器分离读/写信号。

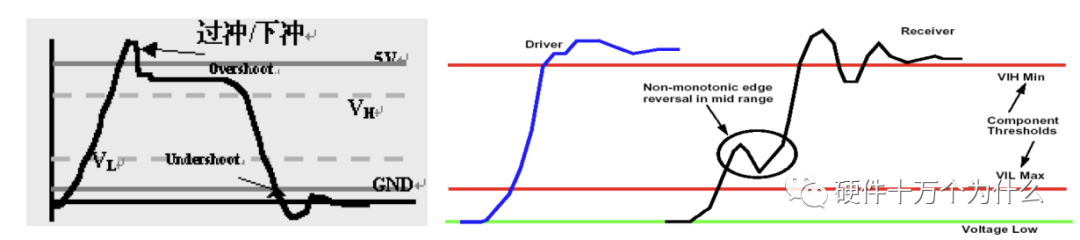

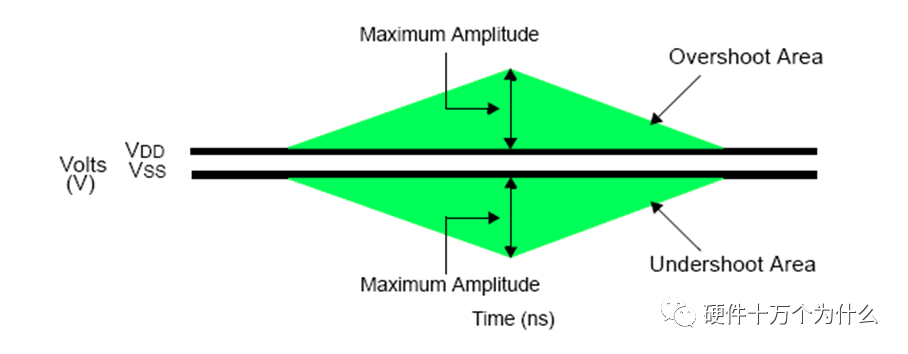

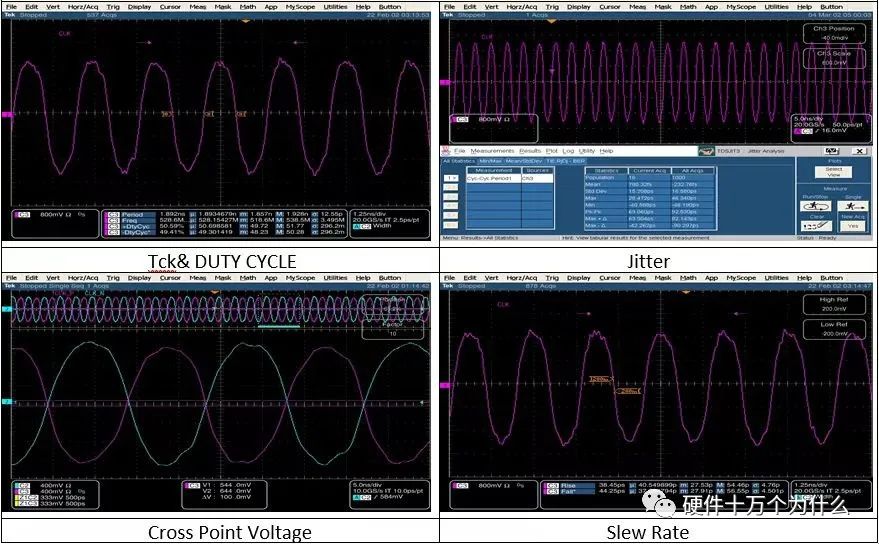

根据 JEDEC 规范,读前导的宽度为 0.9 到 1.1 个时钟周期,而写前导的宽度规定为大于 0.35 个时钟周期,没有上限。第二种触发方式是利用更大的信号幅度触发方法分离读/写信号。通常,读/写信号的信号幅度是不同的,因此我们可以通过在更大的信号幅度上触发示波器来实现两者的分离。测试中要注意信号的幅度,时钟的频率,差分时钟的交叉点,上升沿是否单调,过冲等。

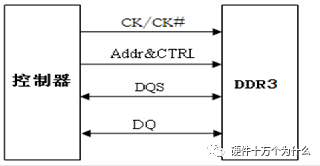

2、DDR3中的几种采样关系

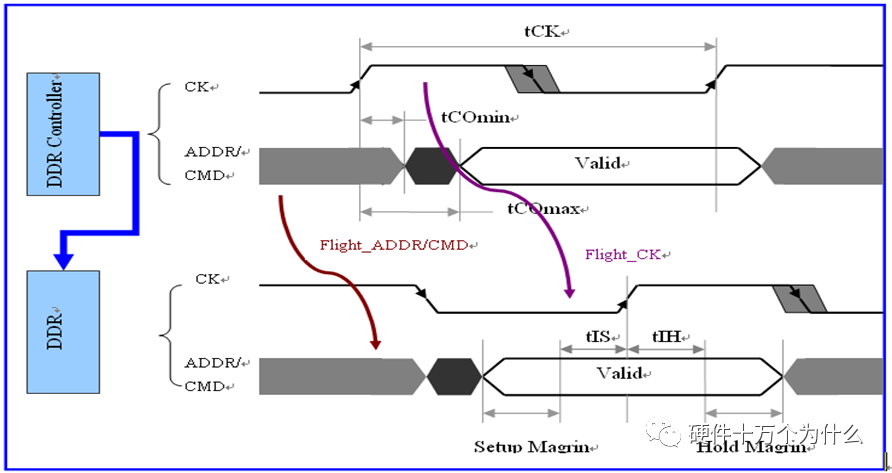

地址控制信号ADDR/CMD与系统时钟CK的时序关系

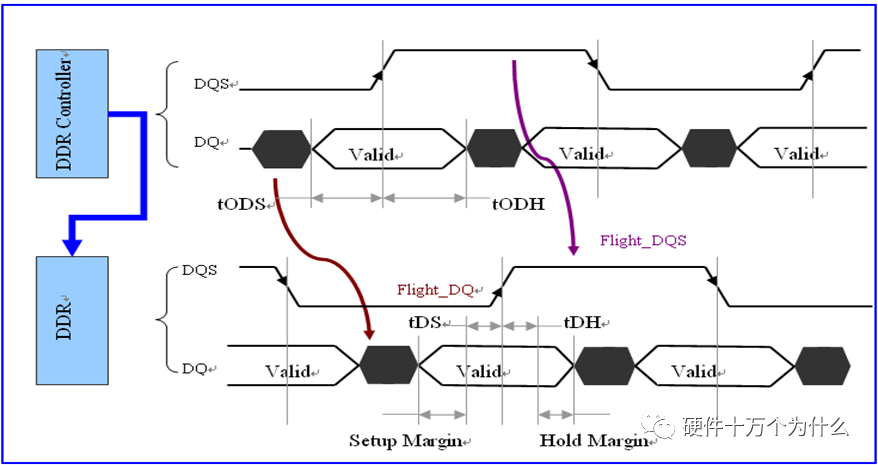

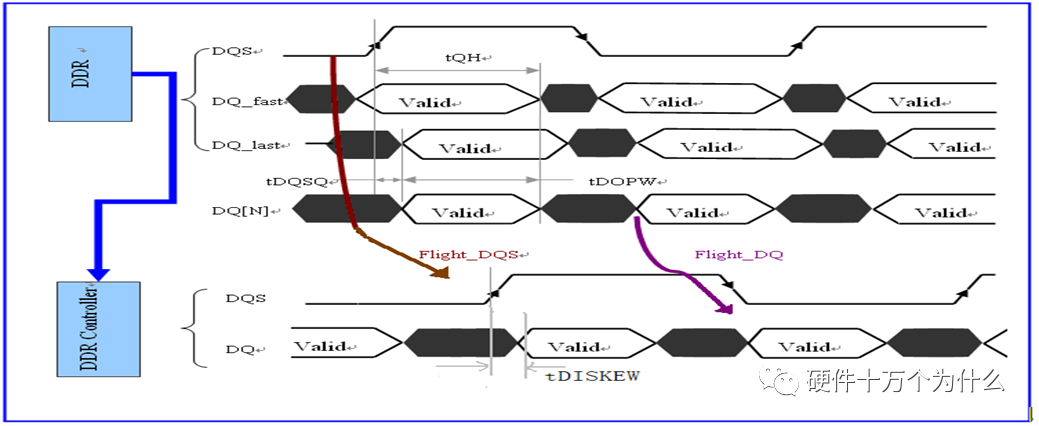

数据信号DQ/DM与数据选通信号DQS的时序关系

写周期

读周期

几种时序关系,后续会做详解

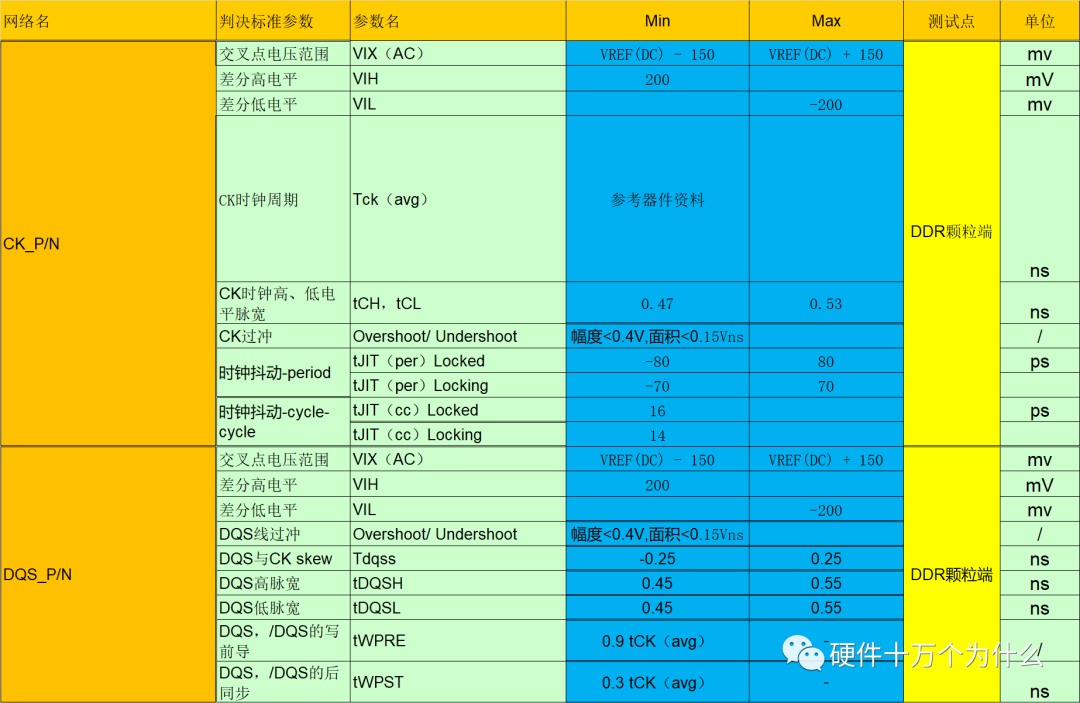

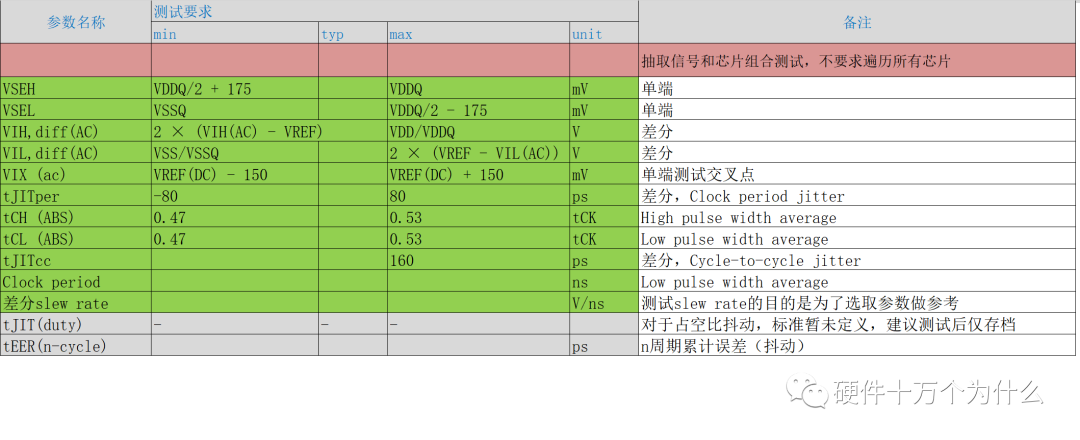

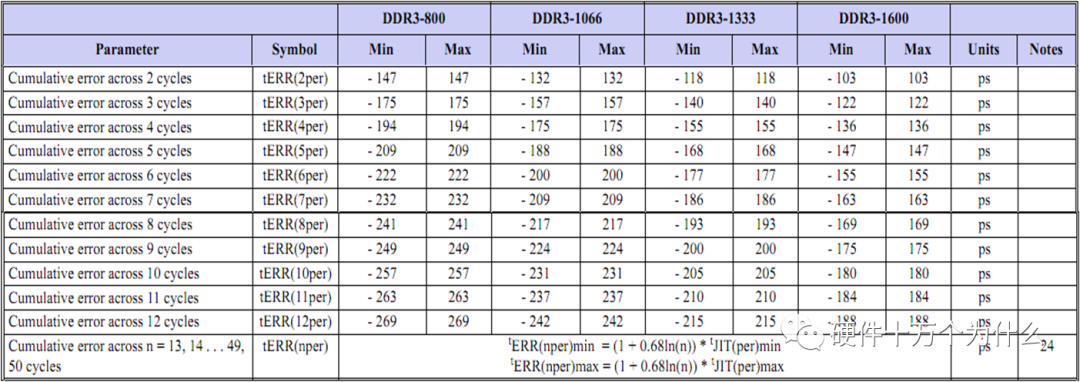

3、DDR时钟信号(CK、DQS)测试:

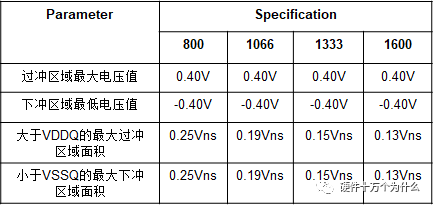

时钟信号过冲要求

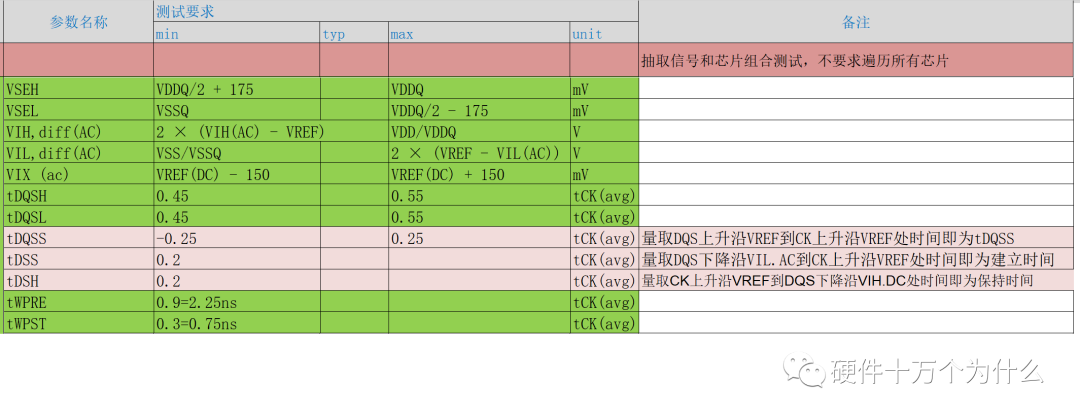

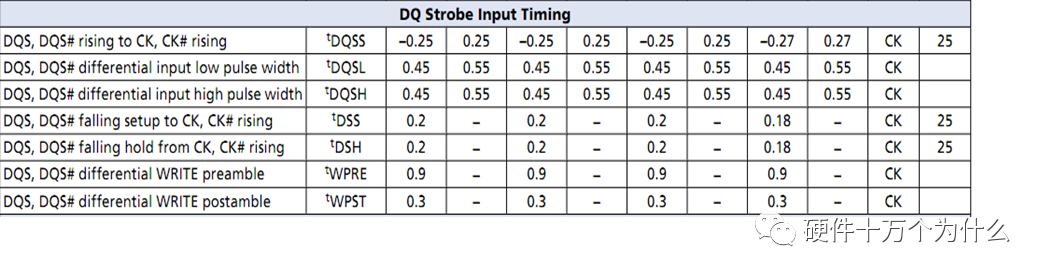

写方向

CK

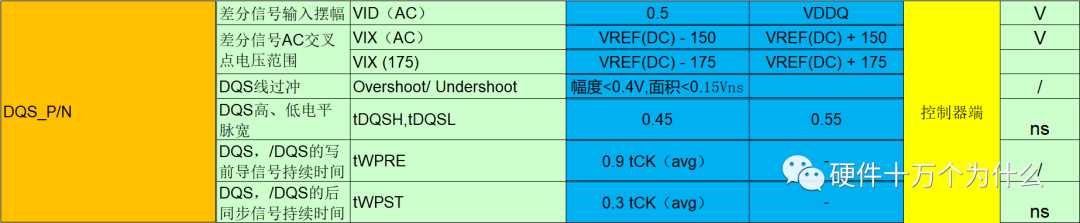

DQS

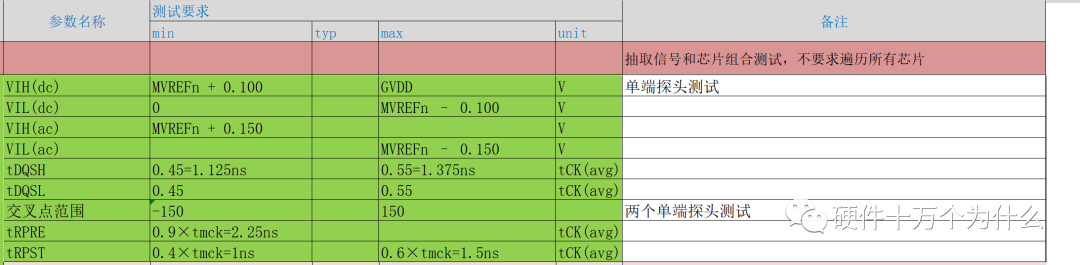

读方向

审核编辑:汤梓红

-

示波器

+关注

关注

113文章

6265浏览量

185303 -

SDRAM

+关注

关注

7文章

428浏览量

55262 -

DDR

+关注

关注

11文章

712浏览量

65394

原文标题:【硬件的单元测试_6】DDR3信号测试1

文章出处:【微信号:Hardware_10W,微信公众号:硬件十万个为什么】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

5V 输入、10A负载DDR3/DDR4通用电源解决方案

泰克公司推出市面上性能最高的DDR3协议测试解决方案

ddr4和ddr3内存的区别,可以通用吗

模拟DDR3的地址信号与时钟信号资料下载

关于Virtex7上DDR3的测试例程详解

Virtex7上DDR3的测试例程

完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表

完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 电源解决方案同步降压控制器数据表

完整DDR,DDR2,DDR3 和LPDDR3 存储器电源解决方案同步降压控制器数据表

DDR3信号测试解决方案

DDR3信号测试解决方案

评论