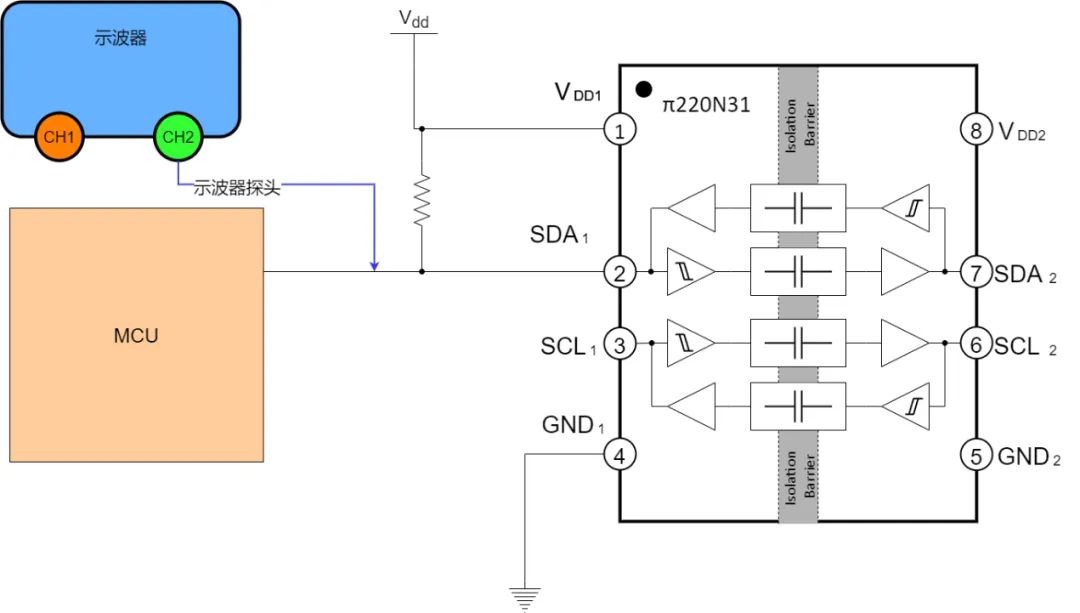

工程师在调试IIC通讯总线时,一般会将示波器探头加挂到IIC隔离器逻辑侧端口上,去观察通信过程中波形是否有误码,如下图所示:

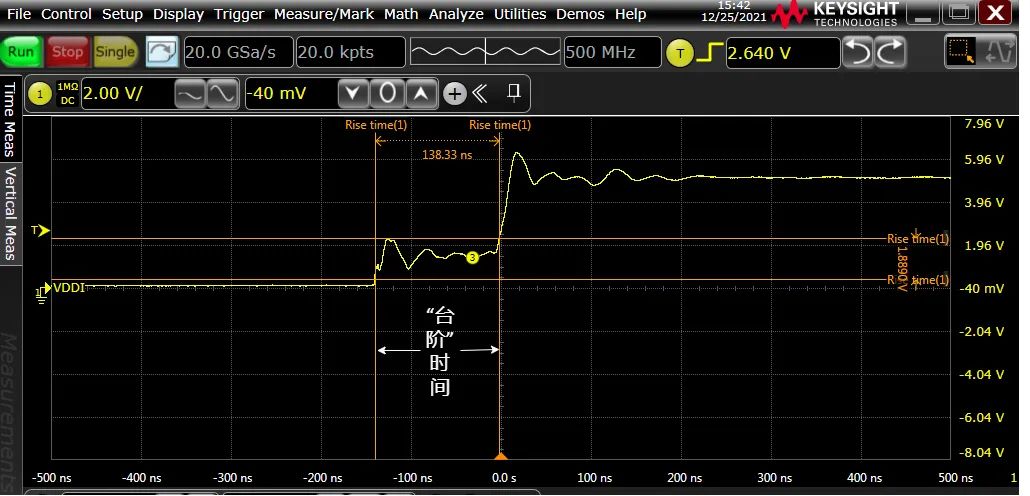

若在MCU向220N31/220N61的SDA1或SCL1端口发送信号的同时观察波形,工程师们会发现波形上升过程中会出现一个明显的“台阶”,通过调整外部电路无法消除;如果断开IIC隔离器和MCU之间的连接之后直接观察MCU输出的信号,会看不到这个“台阶”。这个“台阶”并非由电路设计不当或者器件故障导致的,而是所有双向信号通道的IIC隔离器必然会出现的正常现象,无需担心。

这个“台阶”持续的时间被称为为IIC隔离器的环路延时,是IIC隔离器件的关键性能参数之一。IIC隔离器自身的时序性能和隔离器总线侧外围参数都会影响环路延时的大小。

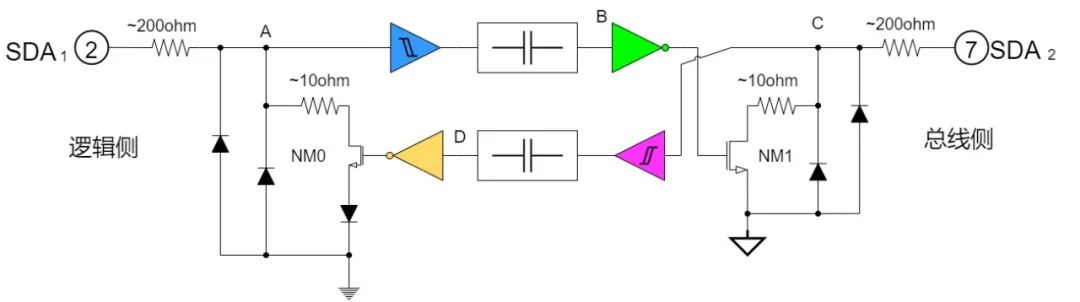

荣湃IIC隔离器双向信号通道的内部示意结构如图所示,以SDA通道为例。可以看到,每个端口既可以作为输出,也可以作为输入,是复用的。逻辑侧下拉NMOS下面的二极管提供了一个对地的电压差,可以防止整个电路被锁死在低电平。

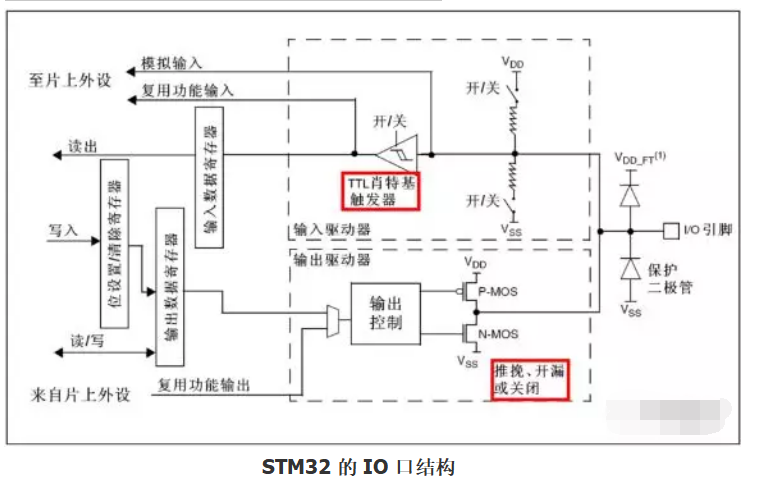

当MCU输出给IIC隔离器的信号从低电平上升到高电平的时候,A点电压会超过逻辑侧输入阈值即600mv,蓝色的输入模块会向绿色的输出模块发送高电平信号。此时,D点依然为低电平信号状态、通过反向器输出高电压使NM0导通,所以外部的电压无法上拉到VDD,波形出现台阶。经过一个传播延时之后,B点从低电平变为高电平,总线侧NM1关断,C点电压通过外部上拉电阻开始上升。当C点的电压达到0.7x VDD时,紫色的输入模块识别到高电平,向黄色的输出模块发送高电平。再经过一个传播延时之后,D点变为高电平,逻辑侧NM0关断,A点电压从“台阶”电平升高到VDD1电压。

过程时序图如下:

以上就是IIC隔离器逻辑侧端口波形出现“台阶”的原因。可以看到,“台阶”的持续时间由逻辑侧至总线侧传播延时、总线侧端口外部上升时间和总线侧至逻辑侧传播延时共同构成。荣湃pai220N31、Pai220N61的传播延时低至45ns,配合总线侧端口外部100欧姆上拉,整体环路延时可控制在120ns以内,能够支持高速的IIC通信。

审核编辑:汤梓红

-

示波器

+关注

关注

113文章

6333浏览量

186487 -

IIC

+关注

关注

11文章

303浏览量

38688 -

隔离器

+关注

关注

4文章

779浏览量

38589

原文标题:技术课堂之十八 | IIC逻辑侧波形出现“台阶”原因的探讨

文章出处:【微信号:gh_fb935efbb3e1,微信公众号:荣湃半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ADP2443 SW侧无法输出正常PWM波形的原因是什么?

采用AD62P29进行模数转换,对正弦信号的转换后的波形不连续,会出现台阶?为什么?

为什么IIC数据出现锯齿波形

CAN总线冷知识-边沿台阶是怎么来的?

IIC的通信原理及分析IIC的真实波形

STM32F334 ADC输入时会产生一个脉冲台阶是什么原因导致的,怎么解决

从IIC实测波形入手,搞懂IIC通信

[转]从IIC实测波形入手,搞懂IIC通信

![[转]从<b class='flag-5'>IIC</b>实测<b class='flag-5'>波形</b>入手,搞懂<b class='flag-5'>IIC</b>通信](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

IIC逻辑侧波形出现“台阶”原因的探讨

IIC逻辑侧波形出现“台阶”原因的探讨

评论