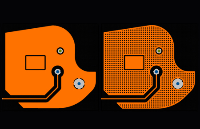

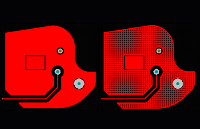

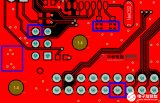

在PCB设计中,框选加铜,会在线与线之间出现死铜(孤岛)。

死铜存在的问题

对于死铜一般都是建议直接处理,因为:

●会造成EMI问题

●增强抗干扰能力

●死铜没什么用

具体来说就是这个孤岛在这里形成一个天线的效应,如果周围的走线辐射强度大,会增强周围的辐射强度;并且会形成天线的接受效应,会对周围走线引入电磁干扰。

把孤岛通过地孔与GND良好连接形成屏蔽等方式,都在一定程度上能解决死铜的问题,但是都存在一定的风险。

最好的办法就是直接删除死铜!

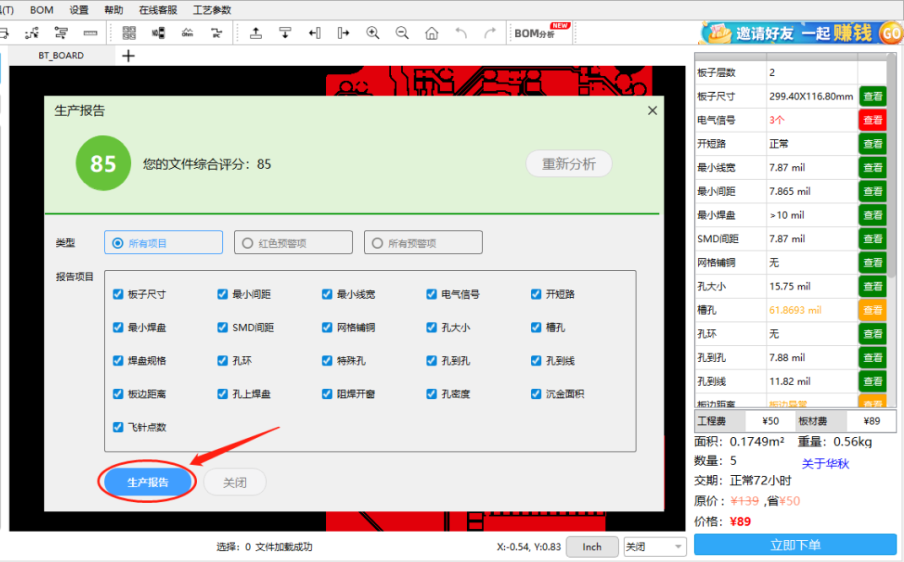

如果PCB已经完成设计了,该怎么检查是否存在死铜呢?类似的一些小问题或者PCB设计的细节处理检查,推荐大家一款国产的免费软件!

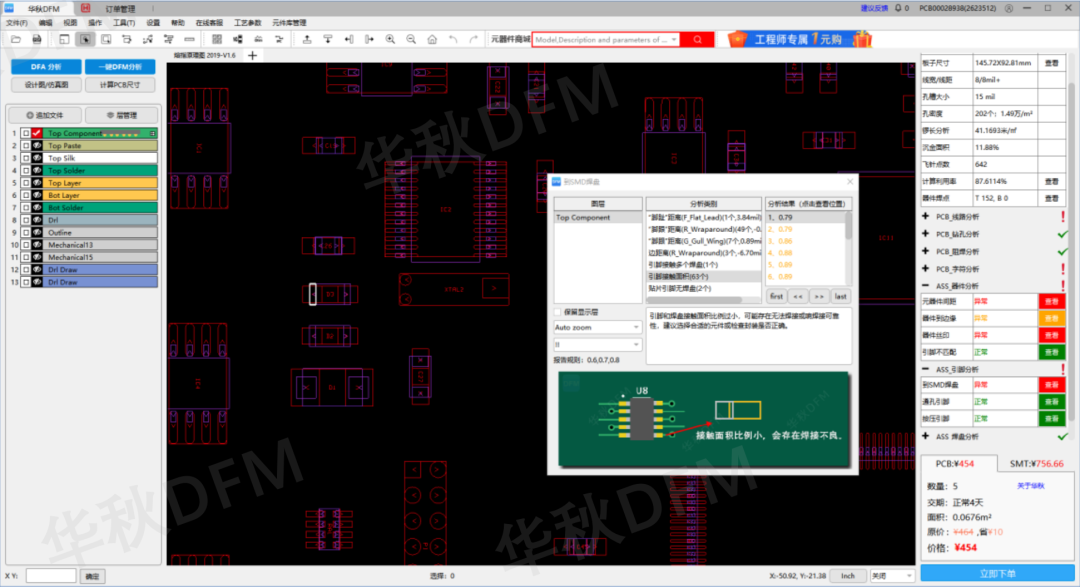

这款软件是为电子工程师量身定做的PCB可制造性设计分析软件,可以一键分析Gerber文件和PCB文件中的设计隐患,并给出合理的优化建议。

它能够直接导入PCB文件,支持解析 Allegro、Altium、Protel、PADS、ODB、Gerber等格式。

打开PCB文件后,点击左上角的“一键DFM分析”,右边就有潜在隐患的提示。

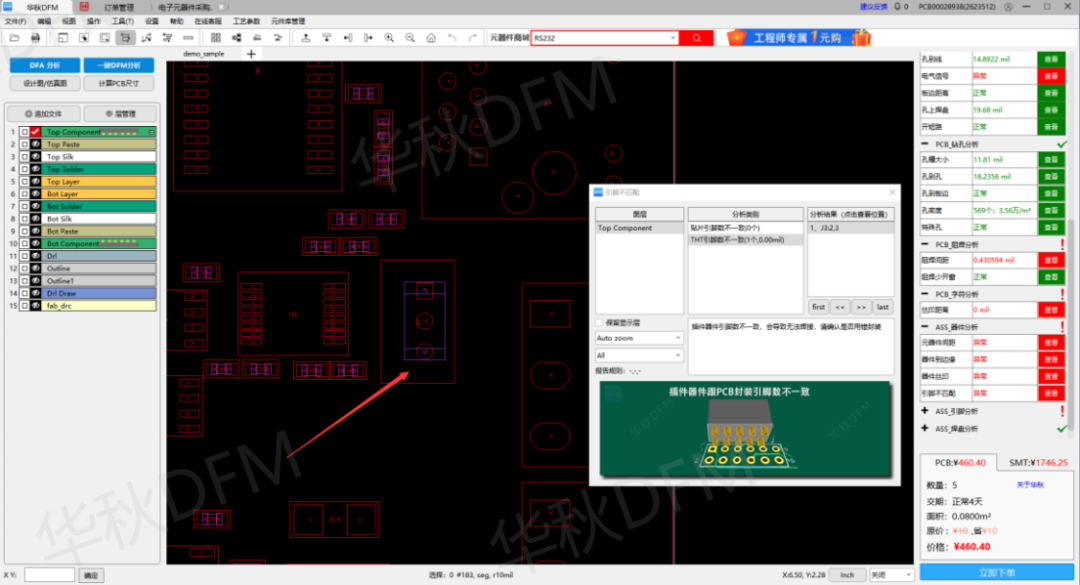

在9月份上线的最新版本中,软件还集成了DFA的功能,工程师准备好生产文件、坐标文件以及BOM表即可完成全面的检查分析。

包括:

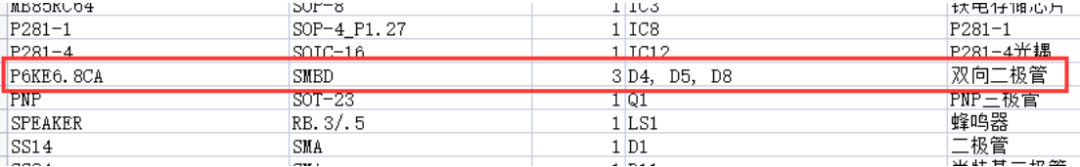

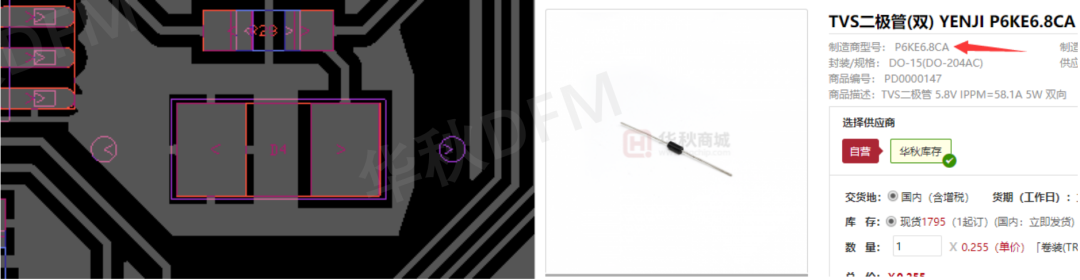

1、检测BOM与封装是否匹配

比如:用户的BOM表里面的型号是P6KE6.8CA,位号D4、D5、D8设计的PCB封装是DFN1610贴片二极管封装,BOM表里面的型号P6KE6.8CA实际是插件双向二极管封装,因此设计的封装无法使用采购的元器件。

2、检测器件与引脚是否匹配

在BOM表的型号与设计的PCB器件封装不一致时,采购的元器件与板子上面的器件引脚不匹配,导致采购的元器件无法使用。

3、检测焊盘大小是否合理

在PCB中画元器件封装时,经常遇到焊盘的大小尺寸不好把握的问题,因为元器件规格书是本身的大小,如引脚宽度,间距等,但是在PCB板上相应的焊盘大小应该比引脚的尺寸要稍大,否则焊接的可靠性将不能保证。

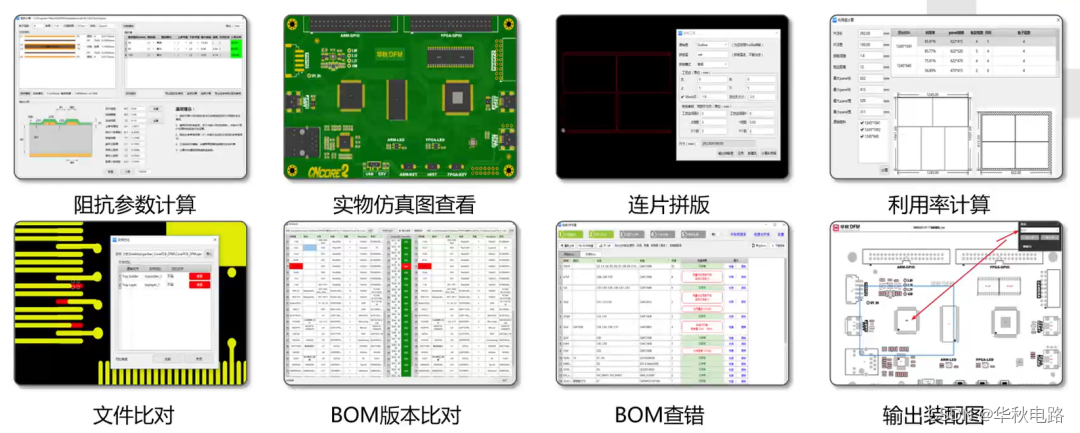

本次更新的内容,加上软件原本的DFM检测功能及多种工具,囊括了工程师常用的多个场景:

华秋DFM目前一共可以实现10大类,共234细项的检查!PCB完成设计后,导入相关文件,通过软件一键检测,即可在最大程度上保证PCB设计的可靠性!

https://dfm.elecfans.com/uploads/software/promoter/hqdfm_dzfsy_hdzwz.zip

审核编辑:汤梓红

-

PCB

+关注

关注

1文章

1813浏览量

13204 -

华秋

+关注

关注

21文章

558浏览量

12345

发布评论请先 登录

相关推荐

必看!PCB几层板设计的决定要素全解析

在绘制PCB时,LMH7322的底部的散热焊盘一定要接地吗?

PCB盲孔填铜,提升电路性能的关键一步

4G模组无法正常联网?一定要记得考虑SIM卡的问题!

【必看】PCB上的死铜为什么一定要去掉?

【必看】PCB上的死铜为什么一定要去掉?

评论