思考:1、在经典的 DynamIQ架构 中,数据是什么时候存在L1 cache,什么时候存进L2 cache,什么时候又存进L3 cache,以及他们的替换策略是怎样的?比如什么时候数据只在L1?什么时候数据只在L2?什么时候数据只在L3?还有一些组合,比如什么时候数组同时在L1和L3,而L2没有?这一切的规则是怎样定义的?

2、本文不讨论什么MESI协议,也不讨论cache基本原理,本文讨论的是多级cache之间的替换策略。

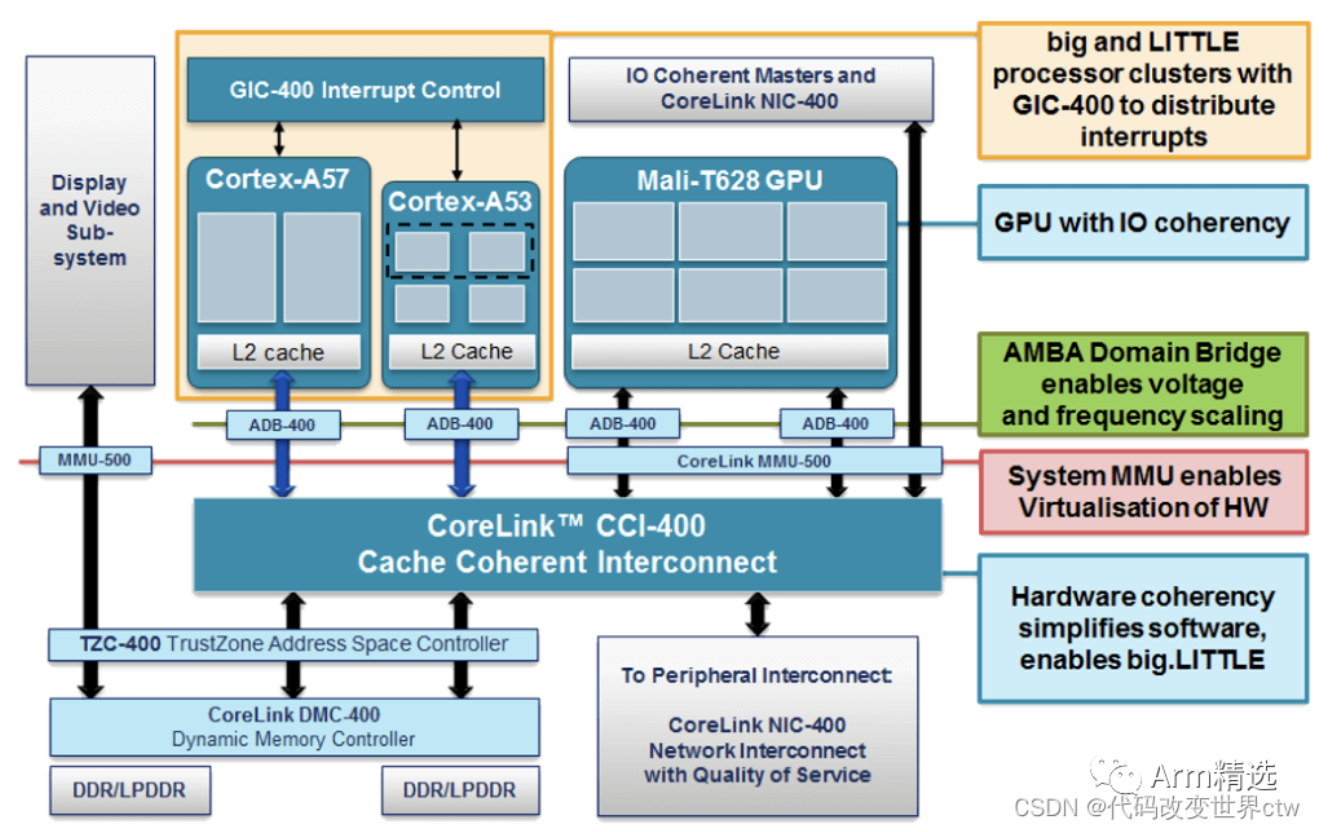

说明:本文讨论经典的DynamIQ的cache架构,忽略 big.LITTLE的cache架构

1、L1 / L2 cache直接的替换策略

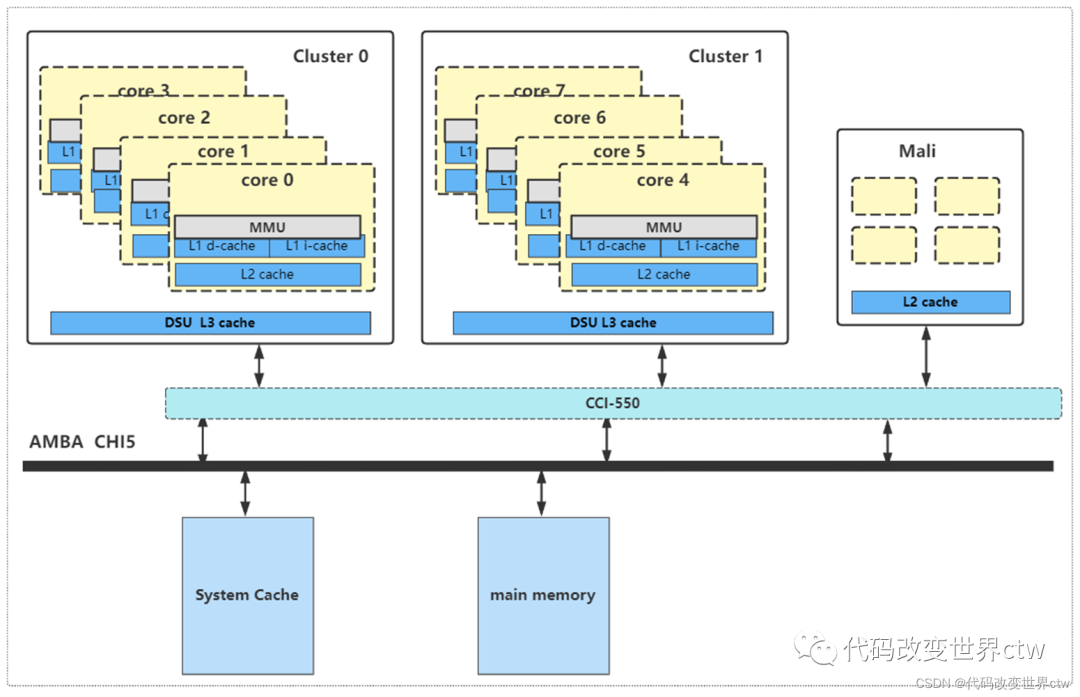

我们先看一下DynamIQ架构中的cache中新增的几个概念:

(1)Strictly inclusive: 所有存在L1 cache中的数据,必然也存在L2 cache中

(2)Weakly inclusive: 当miss的时候,数据会被同时缓存到L1和L2,但在之后,L2中的数据可能会被替换

(3)Fully exclusive: 当miss的时候,数据只会缓存到L1

综上总结:inclusive/exclusive 描述的仅仅是 L1和L2之间的替换策略

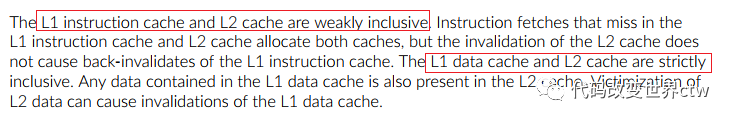

我们再去查阅 ARMV9 cortex-A710 trm手册,查看该core的cache类型,得知:

L1 I-cache和L2之间是 weakly inclusive的

L1 D-cache和L2之间是 strictly inclusive的

也就是说:

当发生D-cache发生miss时,数据缓存到L1 D-cache的时候,也会被缓存到L2 Cache中,当L2 Cache被替换时,L1 D-cache也会跟着被替换

当发生I-cache发生miss时,数据缓存到L1 I-cache的时候,也会被缓存到L2 Cache中,当L2 Cache被替换时,L1 I- cache不会被替换

再次总结 :L1 和 L2之间的cache的替换策略,I-cache和D-cache可以是不同的策略,每一个core都有每一个core的做法,请查阅你使用core的手册。

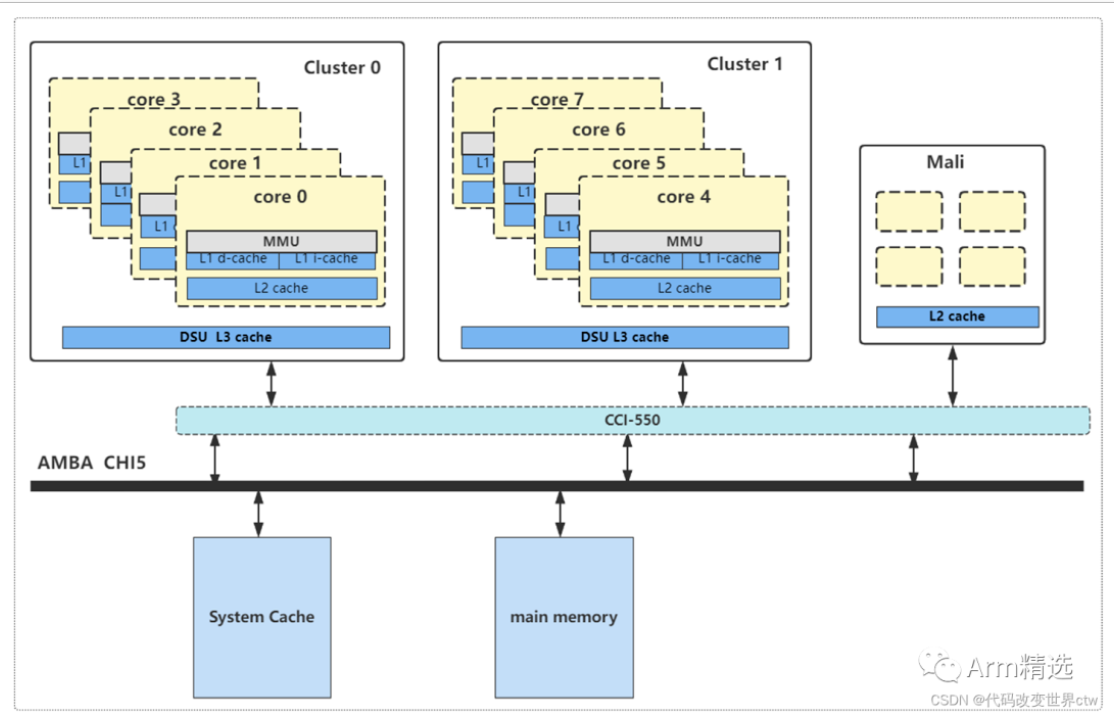

2、core cache / DSU cache / memory 之间的替换策略

说实话, core cache/DSU cache/ 这个名字可能不好,感觉叫 privatecache和share cache更好,我也不知道官方一般使用哪个,反正我们能理解其意思即可吧。

那么他们之间的替换策略是怎样的呢?

我们知道MMU的页表中的表项中,管理者每一块内存的属性,其实就是cache属性,也就是缓存策略。其中就有cacheable和shareable、Inner和Outer的概念。如下是针对 DynamIQ 架构做出的总结,注意哦,仅仅是针对 DynamIQ 架构的cache。

如果将block的内存属性配置成Non-cacheable,那么数据就不会被缓存到cache,那么所有observer看到的内存是一致的,也就说此时也相当于Outer Shareable。其实官方文档,也有这一句的描述:在B2.7.2章节 “Data accesses to memory locations are coherent for all observers in the system, and correspondingly are treated as being Outer Shareable”

如果将block的内存属性配置成write-through cacheable 或 write-back cacheable,那么数据会被缓存cache中。write-through和write-back是缓存策略。

如果将block的内存属性配置成 non-shareable, 那么core0访问该内存时,数据缓存的到Core0的L1 D-cache / L2 cache (将L1/L2看做一个整体,直接说数据会缓存到core0的private cache更好),不会缓存到其它cache中。

如果将block的内存属性配置成 inner-shareable, 那么core0访问该内存时,数据只会缓存到core 0的L1 D-cache / L2 cache和 DSU L3 cache,不会缓存到System Cache中(当然如果有system cache的话 ) ,(注意这里MESI协议其作用了)此时core0的cache TAG中的MESI状态是E, 接着如果这个时候core1也去读该数据,那么数据也会被缓存core1的L1 D-cache / L2 cache, 此时core0和core1的MESI状态都是S

如果将block的内存属性配置成 outer-shareable, 那么core0访问该内存时,数据会缓存到core 0的L1 D-cache / L2 cache 、cluster0的DSU L3 cache 、 System Cache中, core0的MESI状态为E。如果core1再去读的话,则也会缓存到core1的L1 D-cache / L2 cache,此时core0和core1的MESI都是S。这个时候,如果core7也去读的话,数据还会被缓存到cluster1的DSU L3 cache. 至于DSU0和DSU1之间的一致性,非MESI维护,具体怎么维护的请看DSU手册,本文不展开讨论。

| Non-cacheable |

write-through cacheable |

write-back cacheable |

|

|---|---|---|---|

| non-shareable |

数据不会缓存到cache (对于观察则而言,又相当于outer-shareable) |

core0访问该内存时,数据缓存的到Core0的L1 D-cache / L2 cache (将L1/L2看做一个整体,直接说数据会缓存到core0的private cache更好),不会缓存到其它cache中 | 同左侧 |

| inner-shareable |

数据不会缓存到cache (对于观察则而言,又相当于outer-shareable) |

core0访问该内存时,数据只会缓存到core 0的L1 D-cache / L2 cache和 DSU L3 cache,不会缓存到System Cache中(当然如果有system cache的话 ) , (注意这里MESI协议其作用了)此时core0的cache TAG中的MESI状态是E, 接着如果这个时候core1也去读该数据,那么数据也会被缓存core1的L1 D-cache / L2 cache, 此时core0和core1的MESI状态都是S | 同左侧 |

| outer-shareable |

数据不会缓存到cache (对于观察则而言,又相当于outer-shareable) |

core0访问该内存时,数据会缓存到core 0的L1 D-cache / L2 cache 、cluster0的DSU L3 cache 、 System Cache中, core0的MESI状态为E。如果core1再去读的话,则也会缓存到core1的L1 D-cache / L2 cache,此时core0和core1的MESI都是S 思考:那么此时core7去读取会怎样? |

同左侧 |

审核编辑:刘清

-

数据缓存

+关注

关注

0文章

23浏览量

7055 -

MMU

+关注

关注

0文章

91浏览量

18283

原文标题:深度解读DynamIQ架构cache的替换策略

文章出处:【微信号:LinuxDev,微信公众号:Linux阅码场】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

紫光展锐推出全球首款基于DYNAMIQ架构的4核LTE平台--虎贲T310

ARM全新DynamIQ架构奠定未来10年发展基础

浅析Cache多核之间的一致性MESI协议

DynamIQ世界中的big.LITTLE是什么样的?

浅析ARM处理器的power架构

Arm DynamIQ共享单元技术参考手册

ARM Dynamiq共享单元-120型技术参考手册

ARM Dynamiq™共享单元-110型技术参考手册

DynamIQ世界中的big.LITTLE

讨论经典的DynamIQ的cache架构

讨论经典的DynamIQ的cache架构

评论