正如我们所知,“bit”是无符号的,而“byte”是有符号的。那么,你认为下面两个声明是等价的吗?

bit [7:0] aBit; // Note ‘bit’ is 2-state, unsigned byte bByte; // Note ‘byte’ is 2-state, 8-bit signed integer

答案是不等价,因为:

bit [7:0] aBit; // = 0 to 255 byte bByte; // = -128 to 127

所以,你需要小心混合bit和字byte数据类型的计算。

同样,你认为以下两种说法等价吗?

byte MEM_BYTES [256]; bit signed [7:0] MY_MEM_BYTES [256];

答案是等价。我们可以简单理解为

bit signed [7:0] 等价为 byte。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Verilog

+关注

关注

28文章

1351浏览量

110085

原文标题:System Verilog当中的Bits vs Bytes

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Modelsim XE是否支持System Verilog

information:-1.Does itsupport System verilog forverification?2. Code coverage support.3.Assertion support.Whichversionof Modelsim XE su

发表于 11-27 14:20

System Verilog常见问题及语言参考手册规范

本文讨论了一些System Verilog问题以及相关的SystemVerilog 语言参考手册规范。正确理解这些规格将有助于System Verilog用户避免意外的模拟结果。

发表于 12-11 07:19

System Verilog问题和语言参考手册规范

本文讨论了一些System Verilog问题以及相关的SystemVerilog 语言参考手册规范。正确理解这些规格将有助于System Verilog用户避免意外的模拟结果。

发表于 12-24 07:07

浅析System Verilog当中的Bits vs Bytes

to 255byte bByte; // = -128 to 127所以,你需要小心混合bit和字byte数据类型的计算。同样,你认为以下两种说法等价吗?byte MEM_BYTES [256];bit signed

发表于 10-12 14:28

SpinalHDL中Bundle与普通数据类型之间的连接赋值转换

。》Bundle—>Bits在SpinalHDL中,无论是哪种数据类型都是可以转换成Bits类型,我们扩展Bundle类型定义的复杂数据类型也不例外,可以通过asBits函数将自

发表于 10-18 14:22

UART0想使用64 Bytes FIFO该如何设定?

官方TRM中提到NUC230/240的UART0有提供到64 Bytes的接收缓冲区,UART1及UART2只提供了16Bytes的接收缓冲区,但uart.h文件中RFITL设定仅供到14

发表于 08-21 07:24

Verilog Digital System Design

This book is on the IEEE Standard Hardware Description Languagebased on the Verilog® Hardware

发表于 07-23 08:59

•0次下载

VHDL,Verilog,System verilog比较

本文简单讨论并总结了VHDL、Verilog,System verilog 这三中语言的各自特点和区别 As the number of enhancements

发表于 01-17 11:32

•0次下载

学会这些System Verilog方法,芯片验证入门没问题

一个掌握Verilog语言的工程师初次看SystemVerilog都会有这样的感受,这就是Verilog啊,很容易啊,So easy啊。没错,确实是这样,System Verilog的

谈谈Verilog/System Verilog和C的几种交互模式

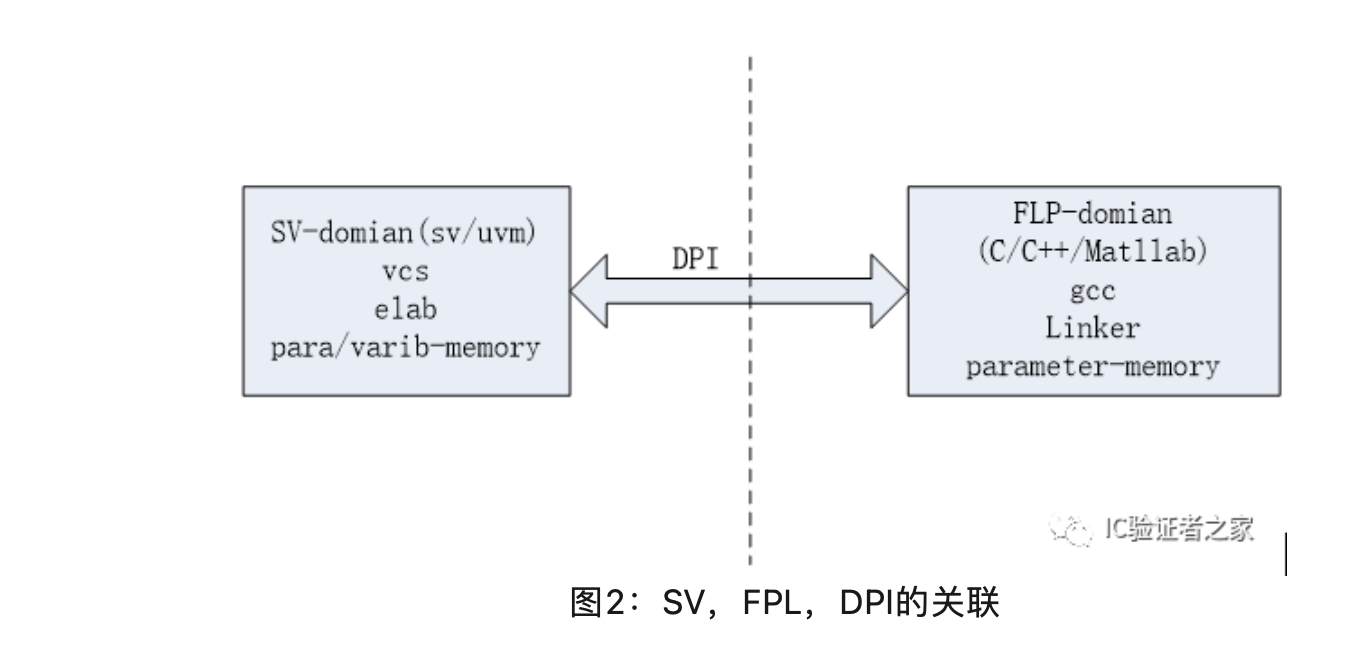

PLI全称 Program Language Interface,程序员可以通过PLI在verilog中调用C函数,这种访问是双向的。

System Verilog的概念以及与Verilog的对比

的端口定义完成后,我们也很难改变端口的配置。 另外,一个设计中的许多模块往往具有相同的端口定义,在Verilog中,我们必须在每个模块中进行相同的定义,这为我们增加了无谓的工作量。

System Verilog中的Bits与Bytes是等价的吗

System Verilog中的Bits与Bytes是等价的吗

评论