注:CH9102F 和 CH9102X 的底板是 0#引脚 GND,是可选但建议的连接;其它 GND 是必要连接。

CH9102X 的 VIO 引脚与 V3 引脚已在内部短接。

CH9102 的 USB 收发器按 USB2.0 全内置设计,UD+和 UD-引脚不能串接电阻,否则影响信号质量。

关于电源与功耗

CH9102 芯片有 3 个电源端,内置了产生 3.3V 的电源调节器。VDD5 是电源调节器的输入端,V3是电源调节器的输出端和 USB 收发器及内核电源输入,VIO 是I/O引脚电源。

CH9102 芯片支持 5V 或者 3.3V 电源电压,V3 引脚应该外接容量为 0.1uF 左右的电源退耦电容。

当使用 5V 工作电压(大于 3.8V)时,VDD5 引脚输入外部 5V 电源(例如 USB 总线电源),由内部电源调节器于 V3 引脚产生 3.3V 电源,用于 USB 收发器。当使用 3.3V 或更低工作电压(小于 3.6V)时,V3 引脚应该与 VDD5 引脚相连接,同时输入外部的 3.3V 电源,V3 引脚仍需外接电源退耦电容。

CH9102 芯片的 VIO 引脚用于为串口 I/O 和 RST 引脚提供 I/O 电源,支持 1.8V~5V 电源电压,VIO应该与 MCU 等外设使用同一电源。UD+和 UD-及 VBUS 引脚使用 V3 电源,不使用 VIO 电源。

CH9102 芯片自动支持 USB 设备挂起以节约功耗。在 USB 挂起状态下,如果 I/O 输出引脚没有外部负载,I/O 输入引脚处于悬空(内部上拉)或者高电平状态,那么 VIO 电源将不消耗电流。另外,当 V3 和 VDD5 失去供电处于 0V 电压时,VIO 消耗电流情况同上,VIO 不会向 VDD5 或者 V3 倒灌电流。VBUS 引脚应该连接到 USB 总线的电源,当检测到失去 USB 电源时,CH9102 芯片将关闭 USB 并睡眠(挂起)。VBUS 引脚内置的下拉电阻可以由计算机端软件通过设置串口 MCR 寄存器中的 OUT1 信号

控制(SERIAL_IOC_MCR_OUT1),OUT1 无效时开启下拉电阻(默认状态),OUT1 有效时关闭下拉电阻。

当 VBUS 引脚串接电阻后用于通过 PMOS 控制 VIO 电源时,CH9102 提供了 VIO 低压保护机制。在关闭 VBUS 下拉电阻期间,如果检测到 VIO 电压低于约 1.4V,那么 CH9102 将自动在 VBUS 引脚吸收约300uA 放电电流,直到 VIO 电压升高后结束该放电电流,并自动开启下拉电阻。

推荐双供电方案,仅 VIO 与 MCU 共用电源,消耗电流极小,USB 挂起/睡眠时 VIO 电流仅 2uA。

CH9102X 的 VIO 引脚与 V3 引脚已在内部短接,VIO 使用内部电源调节器 LDO 输出的 3.3V 电源,支持 3.3V 串口信号

审核编辑 黄昊宇

-

芯片

+关注

关注

459文章

51659浏览量

430411

发布评论请先 登录

相关推荐

国产沁恒微芯片怎么样?

国产芯片解析:无线充电管理芯片CH246跟CH247对比详细

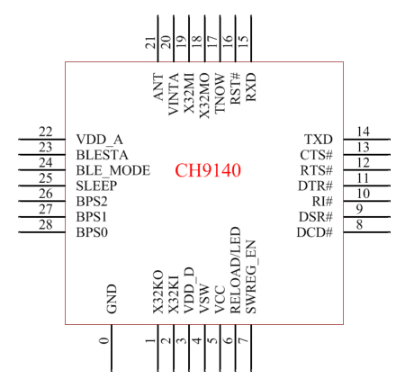

沁恒微蓝牙转接芯片系列解析:CH9140/CH9141/CH9142/CH9143

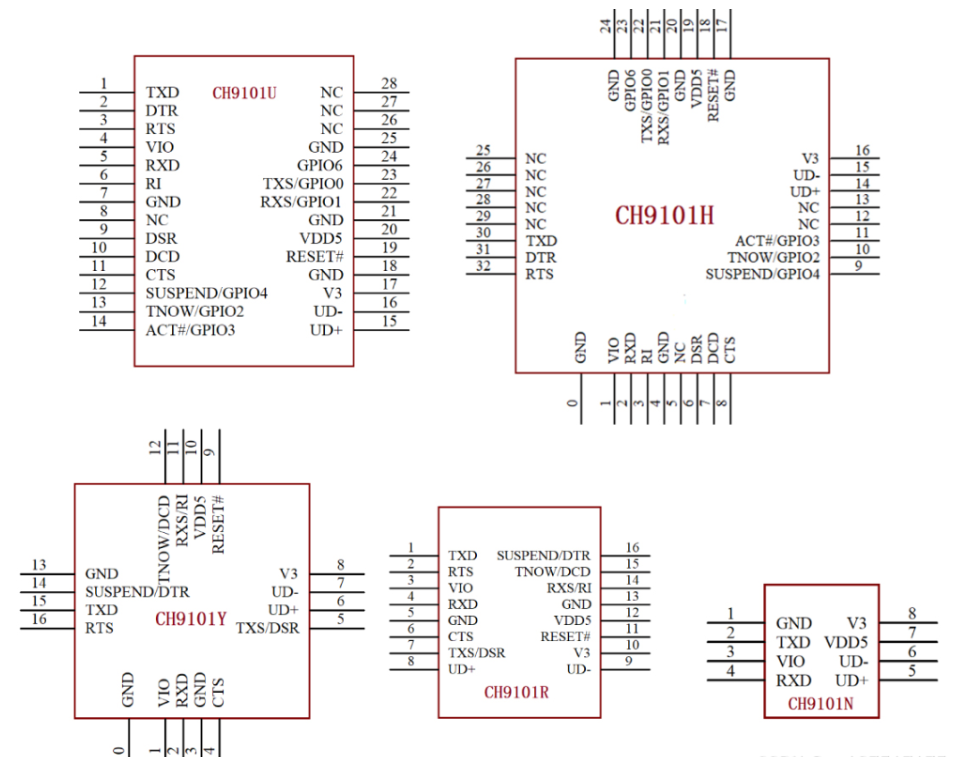

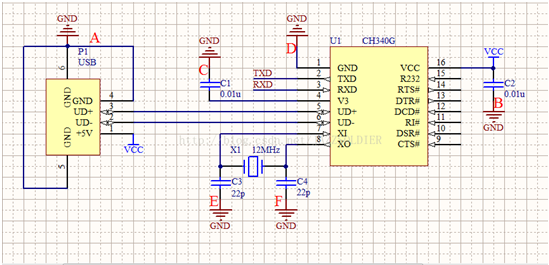

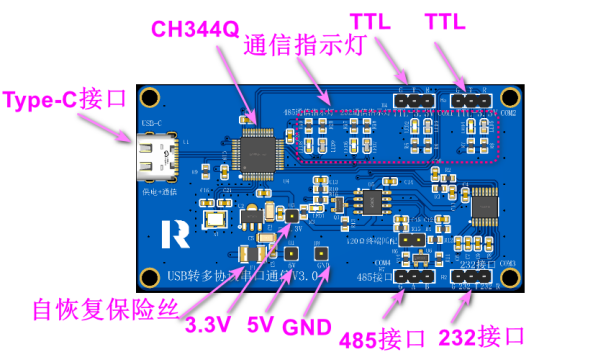

国产USB 转串口芯片 CH9102 兼容替换CP2102 相关资料

国产USB 转串口芯片 CH9102 兼容替换CP2102 相关资料

评论