鉴于对高级快速原型设计和在无人机平台上部署ISR应用程序的需求不断增加,系统工程师将明智地检查与工作资格相匹配的可重构架构和灵活的软件工具。

可重构计算系统是为无人机 (UAV) 上的情报、监视和侦察 (ISR) 应用提供异构数字信号处理 (DSP) 计算解决方案的绝佳且越来越受欢迎的选择。与其他类型的系统相比,可以为ISR无人机身应用创建具有更小尺寸,重量和功率(SWaP)和更高计算密度的可重构系统。

此外,现在可以使用ANSI标准C或FORTRAN进行编程环境,并使程序员能够从硬件中提取所有可能的计算性能。使用标准编程语言大大缩短了学习曲线,与使用专有非标准语言或纯硬件语言的编程环境相比,可以更快地部署应用程序。因此,无人机ISR系统开发人员应该考虑在其设计中必须重新配置的计算架构和灵活的软件工具。

无人机有效载荷的可重构计算

在考虑快速部署无人机有效载荷时,可重新配置的硬件是关键。可重构系统的核心是FPGA集成电路。该器件可以显式编程以执行特定于应用的算法,并且相对于通用设备(如CPU或通用图形处理器单元(GPGPU))产生非常高的计算效率。反过来,这种计算效率为在可重构系统上执行的应用程序产生高性能的每瓦特,从而能够为基于无人机的ISR应用创建计算密集/低SWaP设计。

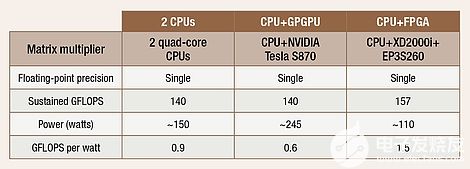

表 1 比较了在仅 CPU 系统、与 GPGPU 配对的 CPU 和与 FPGA 配对的 CPU 上执行单精度矩阵乘法基准测试的情况。可重构系统的每瓦性能比仅支持 CPU 的系统高出 1.7 倍,比 CPU/GPGPU 系统高出 2.5 倍。请注意,CPU/FPGA 组合的总功耗是最低的功耗。

表 1:矩阵乘法性能/功率比。资料来源:Altera公司,“FPGA协处理演进:持续性能接近峰值性能”,WP-01031-1.1,2009年6月版本1.1。

(单击图形可缩放 1.9 倍)

快速无人机有效载荷部署的一个主要因素是标准编程工具的可用性,这些工具与可重新配置的计算机硬件密切相关。集成来自不同供应商的编译器、软件工具、FPGA 板和 CPU 板的零碎方法会减慢部署速度。如果工具和硬件具有不同的供应商,则必须创建一个系统运行时环境来统一系统,然后才能开始有意义的应用程序工作。

一旦真正的应用程序开发最终开始,一个供应商的编译器宏库(假设它们确实有库)将不会针对另一个供应商的FPGA板进行优化,因此应用程序开发必须经历性能规格的降低或时间表扩展。无人机有效载荷开发的零碎方法中的这些和其他固有困难共同将“快速”一词与“部署”分离,通常以意想不到的方式,并且总是在应用程序开发期间。因此,来自一个供应商的完整,集成良好的软件和硬件包通常是快速部署无人机有效载荷的最佳途径。

可扩展的系统和并行编程

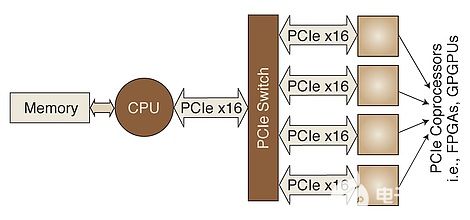

模块化、可扩展的系统非常适合代码重用,这也加速了无人机有效载荷的部署。软件设计的模块化允许经过验证的代码在多个ISR应用程序中重复使用,而硬件模块化则支持根据任务参数和无人机机身的SWaP要求轻松扩展ISR应用程序。如今,大多数异构系统都使用一种或另一种形式的 PCIe,使协处理器能够通过 CPU 访问系统内存。但是,PCIe 的有效可扩展性受到其阻塞的“多对一”架构的限制(图 1)。PCIe 协处理器仅通过 CPU 另一端的系统内存访问数据并相互通信。虽然 PCIe 确实通过 PCIe 交换机提供点对点连接,但一个点始终是 CPU 内存,另一个点始终是 PCIe 设备。真正可用的扩展需要分布式内存和交换网络,该网络具有与交换机上任何模块之间的无阻塞、“多对多”连接。

图 1:典型的基于 PCIe 的协处理器架构,由于其阻塞“多对一”点对点架构,可扩展性有限

一个能够很好地扩展的模块化硬件系统只是一个良好的开端。软件工具必须为程序员提供对可重构系统中密集计算效率的直观或自动访问。如果程序员必须深入到系统的体系结构中以查找和开发满足应用程序性能要求的解决方案,则无人机有效载荷的开发和部署会受到影响。有标准的计算机语言可用于在可重构系统中对CPU和FPGA进行编程,但仅使用C或FORTRAN并不能实现ISR应用的性能要求。C 和 FORTRAN 是传统上用于 CPU 的串行编程语言,其中指令按顺序执行,一次一条指令。可重构系统的性能是通过并行编程实现的:多个程序指令流同时作用于多个数据流。

幸运的是,科学超级计算社区已经为C和FORTRAN开发了并行化技术,其中许多技术已被一些可重新配置的系统编译器采用。以编程方式指定并行性的一种方法是 OpenMP 并行部分杂注语句。在传统的大型微处理器集群上,并行部分杂注所包含的代码块可以在CPU上并行执行。在可重配置的系统上,OpenMP 样式编译指示指定的代码块在 FPGA 中实例化,以便这些“硬件代码块”并行执行。另一种方法是数据流,其中一系列计算在时间上重叠;例如,计算块可以在收到前一个块的第一个结果时开始执行,而不是在开始之前等待前一个计算块的所有结果生成。

除了从科学超级计算中借用的并行化技术外,大多数可重新配置的系统编译器还执行自动循环流水线以提高执行性能。此外,可重新配置的系统编译器在FPGA硬件中自动创建程序循环中的所有算术运算,所有这些运算都是并行执行的。与此形成鲜明对比的是微处理器编译器,微处理器编译器受 CPU 设计中可用算术计算元素数量的限制。这里真正的问题是给定系统的特定软件工具集的有效性。但是,软件工具确实存在,可以为计算密集型ISR应用程序的程序员提供可重新配置硬件中的潜在性能。

可重配置性有助于快速部署、SWaP

如今,可重新配置的系统和工具可用于快速开发和部署 ISR 应用程序。可重构系统的密集计算特性使其成为尺寸、重量和功耗至关重要的解决方案的理想选择。软件工具与硬件紧密耦合,使软件程序员能够在低SWaP处理器有效载荷中快速实现高性能。

因此,SRC计算机提供模块化,可扩展,可重新配置的低SWaP系统,带有软件工具和库,使用ANSI标准语言快速部署无人机的计算密集型ISR应用程序。SRC Computers开发了一种高带宽,低延迟的网络交换机,除了用于模块间通信的数据流构造,用于代码块并行化的OpenMP样式编译指示以及用于指令级并行化的自动循环流水线外,还提供了必要的非阻塞“多对多”模块。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19276浏览量

229765 -

dsp

+关注

关注

553文章

7998浏览量

348857 -

无人机

+关注

关注

230文章

10432浏览量

180326

发布评论请先 登录

相关推荐

为无人机快速部署可扩展、密集的ISR有效负载

为无人机快速部署可扩展、密集的ISR有效负载

评论