作者:JASON WADE,RANDALL MILLAR

军方依靠视频图像进行态势感知,但图像质量通常很差,以至于操作员可能会错过重要细节。为显示控制器配备实时运行图像增强算法的FPGA,为观看者提供更好的图像。

现代国防能力、情报、监视和侦察 (ISR) 的支柱依赖于由集成传感器、飞机和人力组成的强大而多样化的网络。该网络的价值最终取决于人类能够清楚地看到传感器图像,识别重要细节并采取果断行动。在现场,我们很少或根本无法控制从传感器获取图像的照明和环境条件。但是,可以通过允许查看实时传感器图像的人实时微调视频图像以提取更多信息来为他们提供更多控制。

实时增强视频需要巨大的计算吞吐量。它需要将复杂的图像处理算法应用于传入的视频流,而不会引入延迟。高性能现场可编程门阵列(FPGA)提供了一个理想的平台,允许使用并行计算技术实现软件算法。当嵌入到智能显示控制器中时,这些算法使操作员能够最大程度地控制图像质量,并显著提高图像清晰度。

清晰度在旁观者的眼中

全动态视频 (FMV) 是军事态势感知的首选工具。几乎所有军用车辆都有自动视频录制功能,包括战斗机、卡车和坦克等载人船只,以及无人驾驶飞机系统(UAS)。在移动平台上生成高质量图像会带来许多挑战。除了与摄像机运动和由此产生的图像透视相关的问题外,视频图像的质量还可能因恶劣的环境条件、数据链路降级和带宽限制而受到影响。大气因素(如黎明、黄昏或夜间照明不佳)以及恶劣天气(包括沙尘暴和多变的云层)可能会遮挡重要细节。

然而,传感器图像质量并不是唯一的问题。观看视频的条件差异很大,因此带来了另一组挑战。例如,视频流可以在明亮的阳光下、水下或屏幕上有前照灯的黑暗洞穴中观看。因此,在显示器本身内提供图像增强功能具有明显的优势,而不是在传感器或网络上的其他地方。

确保良好图像质量的唯一方法是让观看者能够根据自己的需要调整图片。实现这一目标的最佳方法是为战术边缘带来实时视频增强。FPGA 提供 将 这种 功能 直接 构建 到 显示 控制器 中 所需 的 性能、 设计 灵活 性 和 弹性。

具有实时图像增强功能的视频控制器

所有显示控制器都执行基本图像处理,这意味着它们以特定分辨率接收视频并以显示器的原始分辨率显示。例如,如果它是 1,920 x 1,080 的显示器,则它需要为每一帧接收 1,920 x 1,080 像素。但是,不能保证用户将插入与此匹配的栅格。事实上,他很可能不会。相反,传入的视频流的格式可能为 1,024 x 768 或类似格式。视频处理是缩放行为,即将传入的视频信号从一种大小或分辨率转换为另一种大小或分辨率,以便与显示面板配合使用。这就是通常所说的“视频处理”,与视频增强相比,这是一项小壮举。

视频增强从视频处理结束的地方开始。专为实时视频增强而设计的视频控制器可能从现成的视频处理芯片或专门构建的ASIC开始,该芯片可以预先进行缩放和基本图像处理。一旦该操作完成,视频流将被传递到特殊用途的处理器,如FPGA以进行增强。

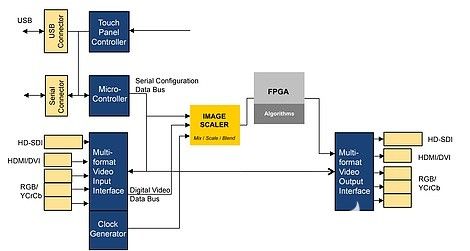

当然,可以选择将视频处理和视频增强功能组合在一个ASIC中。事实上,这是消费类电视制造商经常做的事情。但是,这种实现最适合基本的视频增强,例如边缘锐化,并且几乎没有为复杂的图像增强算法留下多少空间。通过内置于实时视频增强的FPGA,可以超越传统的显示功能并提供高级增强功能(图1)。

图 1:具有内置实时视频增强功能的显示控制器:视频处理芯片对传入的视频流进行格式化,以满足显示要求。FPGA运行图像增强算法,以实现显著更好的图像清晰度。

惊人的算法是计算密集型的

任何熟悉照片编辑程序(如 Adobe Photoshop)的人都可以欣赏软件算法在增强静止图像方面的强大功能。使用复杂的软件算法将数学函数应用于图像矩阵,可以在不丢失细节的情况下揭示隐藏的视觉信息层。这是一种纯粹的数学方法,利用所有可用的图像信息,包括人眼通常不可见的部分。

在过去的几十年中,使用直方图操作、卷积、形态学、过采样和欠采样、量化和光谱处理(包括傅里叶变换和离散余弦变换 (DCT))等技术开发了大量的图像处理算法。这些算法往往是计算密集型的。传统的处理器技术无法提供满足 FMV 所需的性能,速度高达 60 帧/秒 (fps),或每 16.67 毫秒 1 帧。处理标清 (SD) 视频流需要大约 150 到 200 千万亿次浮点运算,而 1,080p 流需要大约 1.2 万亿次浮点运算。这就是 FPGA 发挥作用的地方。

卷积核过滤在工作

当使用并行处理技术重写图像增强算法并移植到FPGA时,可以实时显著增强ISR视频。在多种类型的图像增强算法中,空间卷积核滤波产生的结果最显著。

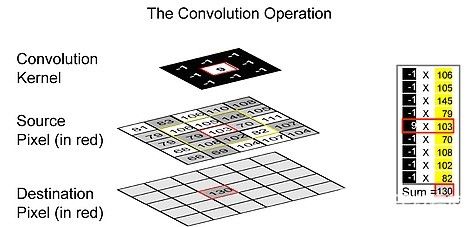

虽然卷积滤波的基础数学很复杂,但执行图像卷积运算非常简单。卷积核根据感兴趣的像素值与其周围像素的值之间的关系生成新的像素值。在卷积中,两个函数相互叠加和相乘。其中一个函数是视频帧图像,另一个是卷积核。帧图像由一大数组表示,这些数字是 x 轴和 y 轴中的像素值。卷积核是一个较小的数组,或一个掩码,其中的值是根据所需的过滤函数(例如,模糊、锐化和边缘检测)分配的。此数组的大小(称为内核大小)确定将使用多少个相邻像素来生成新像素。在卷积中,内核对图像进行操作,以便在每次应用掩模时创建一个新像素,因此必须对图像中的每个像素重复该操作(图 2)。

图 2:卷积核掩码操作:源像素被自身及其相邻像素的加权平均值替换。

大果仁产生更好的结果

卷积是计算密集型的,因此大多数实现仅使用小内核(3 x 3,9 x 9,16 x 16)。但是,使用独特的非传统编程技术,可以实现非常大的卷积核,从而产生更好的结果。非常大的内核产生更好结果的原因与给定区域(称为空间频率)上亮度的范围和变化有关。

在处理时,通过考虑以每个像素为中心的大型邻域中的数据,大内核包含更大的空间频率范围。传统的小核处理只能增强最高空间频率下的细节,这些频率通常只包含图像的光谱内容(全色范围),并且是噪声普遍存在的地方。因此,小型内核处理器必须采用高增益才能对图像产生明显的影响。高增益往往会产生清晰的轮廓伪像,并增加可见的噪点。大的内核处理(在图像的更多“肉”上操作)可以产生显着的结果,增益要低得多,并具有大面积着色的额外好处,产生更自然的图像,增加局部对比度,增加维度,并改善细微细节和特征的可见性。

一种大型内核卷积算法,旨在通过消除雾霾和增强图像细节来澄清图像,使用 400 x 400 内核。该澄清器算法的工作原理是求解一个数学方程,该方程将“完美图像”的模型与传感器相机捕获的测量的不完美图像相关联。该技术反向工作,去除损坏的噪声和图像模糊,同时调整每个像素的强度,直到出现适合实时数据的最简单的图像。这个概念是,因为已知环境因素会扭曲图像,如果知道扭曲是如何产生的,那么它可以被撤消。其他技术使用的方法可以去除失真并接近真实图像,但仅此而已。相比之下,这种方法更进一步,继续将算法应用于图像,直到它尽可能接近完美图像。因此,它能够去除所有不属于真实图像的不必要的数据。一旦消除了环境失真,并且随着更多真实图像的显现,就会实现非凡的清晰度。

追求完美的形象

FPGA 打开了通往大量复杂算法的大门,这些算法可用于实时增强 ISR 视频。FPGA是计算主力,非常适合军用视频显示控制器应用。它们可以承受恶劣的环境,并满足严格的军事要求,包括坚固性、温度耐受性、可靠性和保证较长的产品寿命。由于 FPGA 可 重新 编 程, 因此 可 实现 设计 灵活 性, 因此 显示 控制器 可以 轻松 适应 变化 的 视频 标准 或 特殊 任务 要求。此外,一旦部署,基于FPGA的显示控制器可以现场升级,以添加附加功能和新的图像增强算法。

审核编辑:郭婷

-

传感器

+关注

关注

2548文章

50642浏览量

751731 -

FPGA

+关注

关注

1625文章

21663浏览量

601670 -

控制器

+关注

关注

112文章

16185浏览量

177336

发布评论请先 登录

相关推荐

断电控制器是控制供电开关的装置对吗

ASP4644在FPGA SERDES供电中的应用

基于AG32的激光控制器

EtherCAT主站控制器系统实时性测试

开放式高实时高性能PLC控制器解决方案-基于米尔电子STM32MP135

Led显示屏控制系统怎么使用 led显示屏控制器怎么设置

FPGA供电的显示控制器可实时增强ISR视频

FPGA供电的显示控制器可实时增强ISR视频

评论