简介

IC互联总线(PC总线)的应用正越来越广泛地扩展到包括消费电子、通信设备和工业设备中。在实际应用所有情况下,3.3V IPC总线接口都使用低电压光电耦合器来隔离电流信号。在最少元件配置中,使用三个高速光电耦合器隔离CLK,SDA_in和SDA_out线路信号。

本文讨论了对要求隔离I2C总线接口的应用与光电耦合器传播延迟时间有关的参数怎样影响数据完整性和系统可靠性,包括IEEE 802.3af标准兼容的以太网在线供电交换机和模数转换器到微控制器的接口。我们在实例中使用安捷伦HCPL-063L双通道和HCPL-06OL单通道15 MBd 3.3V光电耦合器。

PC总线基础知识

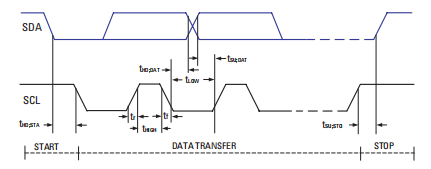

12C总线是飞利浦半导体开发的一种串行数字信号通信协议。它在接口端口中只要求两条导线和极少的硬件,互连的设备通过软件寻址。主设备和从设备之间的数据速率范围为标准模式下的100 kbps到快速模式下的400 kbps到高速模式下的3.4 Mbps。两条导线分别承载SDA数据和SCL时钟,SDA的每个数据位在每个SCL时钟的高电平时上读取。在此期间,数据必须保持稳定。只有在SCL线路上的时钟信号为低时,数据线才能实行高到低或低到高状态转换(图1)。

图1 IC总线时序图

PC总线中的光电耦合器传播延迟

应用环境要求在IC总线接口进行电流隔离,以保证无差错传送数据和安全隔离高压设备。适当的光电耦合器可以提供这种隔离能力。

高速光电耦合器的速率范围从100千波特(kBd)到50兆波特(MBd),可以用于数字数据接口隔离。IC总线接口的相应光电耦合器主要取决于应用的速度和传播延迟要求。

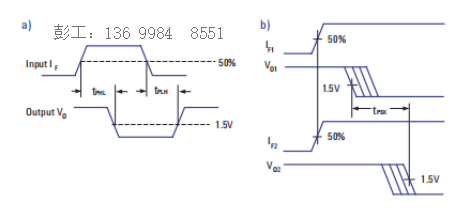

首先,光电耦合器的最大高到低和低到高传播延迟(TPHL,和tPHL)将决定器件的最大数据传输速率(图2a)。最大传播延迟 tP(MAX)以tPHL或tPLH中的高者为准。传输NRZ(非归零)数据的光电耦合器要求数据位周期至少要高于(tp(MAX)≥TP(MAx)

因此,最大数据速率是: FNRz (MAx)=1/t≤1/tP(MAx)

时钟信号被认为是RZ(归零)数据,如IC总线SCL;时钟周期同时包括高电平时间和低电平时间: t=tHIGH+tLow

对一般50%占空比的RZ时钟信号,判断RZ据速率的安全规则是: fRz(MAx)≤1/2(tp(Mx)

图2光电耦合器传播延迟和偏差

但是,在PC总线时钟周期中,允许高电平时间短于低电平时间。要使光电耦合器传送占空比小于50%的信号,光电耦合器的最大传播延迟t(MAX)应小于高电平时间: tHIGH≥tP(MAX)

例如,在考虑隔离400 kHz快速模式时钟频率和50%占空比的IC总线时(相当于数据速率为800 kBd),光电耦合器的最大传播延迟不能超过1.25 us。由于I2C总线规范允许快速模式时钟高电平时间最短为0.6 us,因此光电耦合器的最大传播延迟tp(MAx) 必须短于0.6 us,而不是1.25us。

在高速光电耦合器中,脉宽失真(PWD)参数是tPHL和 tPLH之差。一般来说,PWD值在最小数据脉宽的20%-30%之间是容许的。

在并行数据信号同时传输多通线路时,光电耦合器的传播延迟偏差tpsx是一个重要系数,它决定着最大并行数据传输速率。如果并行数据通过两个单独的光电耦合器或通过一个多通道光电耦合器传送,那么通道之间的传播延迟差异将导致数据以不同的时间到达光电耦合器的输出。如果这种传播延迟差足够大,那么它将限制可以通过光电耦合器传输并行数据的最大速率。

如图2b所示,传播延迟偏差定义为在相同条件下(即相同驱动电流、供电电压、输出负荷和工作温度)对任何光电耦合器通道组,tpLH和/或tPHL最小和最大传播延迟之差。光电耦合器的tpsx将在数据线路和信号线路中导致不确定性。一般来说,可以传输通过并行光电耦合器的绝对最小数据脉宽是t.s的两倍。保守设计应使用略长的脉宽,保证电路中其它地方引起的任何额外不确定性不会导致问题。l2C总线时钟信号高电平时间是最短的脉冲,因此两倍的光电耦合器传播延迟偏差不应超过I2℃时钟的高电平时间。

PC总线协议对SCL和SDA信号电平敏感:SDA应在SCL高电平时间中稳定在高电平或低电平。l2C总线器件必须在内部提供一个数据保持时间 tHD:oAT,以过渡在SCL信号下降沿时的高电平和低电平的不确定期。由于光电耦合器将在SDA信号和SCL信号中产生不确定性,数据保持时间t;DAT应设置成大于tsx。SDA 数据建立时间tsupAr中也应考虑tpsx的值。

PC总线协议还要求连接到总线上的发送器件的输出电路必须是漏电极-开路或集电极-开路,以执行连线逻辑与功能。安捷伦HCPL-O63L光电耦合器拥有一个集电极–开路输出。根据其技术参数, t-MAx)是90 ns,这表明了其传输高速数据的能力最大传播延迟偏差tsK最低是40 ns,它将提供足够的时间允许PC总线设置数据保持时间/建立时间。

隔离以太网供电中的热插拔控制器

新兴行业标准IEEE 802.3af可以通过以太网电缆传输电力。这一网络的结构承接IEEE 802.3以太网络,但在电缆中通过一对备用线或信号线对来传载-48 VDc电力,为IP电话、网络像机和无线局域网接入点等被供电设备(PDs)供电。供电设备(PSE)用来在以太网交换机或集线器上提供-48 VDC电源。

从以太网链接路段看,802.3af标准PSE可以连接在两个位置。中间方式连接在现有以太网交换机外部实现PSE技术,终端方式(或终点/DTE PSE)则连接在交换机内部实现PSE。到目前为止,大部分厂商选择了中间方式PSE,但也有一些厂商在交换机中集成了终端方式PSE。

PSE不仅把电力分配到以太网络中,它还提供了功率管理功能。功率管理功能搜索链路段,看是否存在PD,对PD的额定功率分类,然后在检测到PD时为链路供电,监测链路段上的电流,在PD断开连接或不再要求电源时从链路段中去掉电力。

在PSE和PD设备中802.3af规范要求电气隔离,这与10/10OBASE-T以太网的物理层(PHY)要求相一致。如前所述,PSE热插拔控制器采用县-48V电源,这个电源连接到LAN数据电缆的备用线对或信号线对上。热插拔控制器与主控制电路之间要求电气隔离。

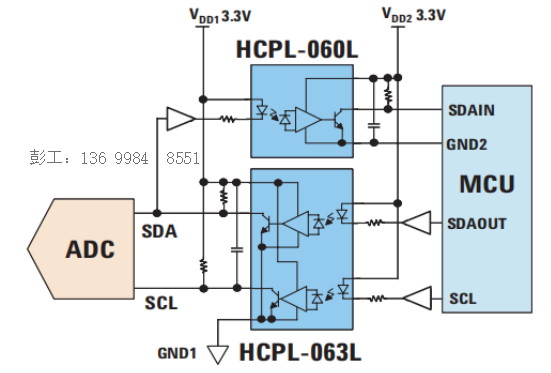

如图3所示,PSE热插拔控制器或电源管理芯片利用PC总线协议来与主机微控制器通信。在本例中,两个HCPL-063L双通道3.3V光电耦合器隔离热插拔控制器芯片和主机微控制器之间的IPC总线接口。其中一个HCPL-O63L的两条通道把时钟和SDA_IN数据从主控制器╱主器件传送到热控制器/从器件,另一个HCPL-063L的一条通道把SDA_OUT数据从从器件反向传送到主器件。第二条通道可以接口额外的功能,如端口请求/中断信号。LED输入电阻器采用保守设计,要求提供的输入电流大于5 mA阈值电流。我们推荐采用小于200的电阻器,把LED驱动电流限制在大于7.5 mA。在主控制器和热插拔控制器之间两个3.3 V电源必须相互隔离。

图3: POE交换机800 PSE中光电耦合器隔离的12c总线

安捷伦HCPL-O63L隔离电压达到3750 Vrmg/1分钟(根据UL1577测试),使得以太网供电交换机能够满足电信设备安全标准,如lEC 60950。HCPL-O63L的15kV/us抗共模瞬变能力将防止来自电源热插拔电路的瞬时电压噪声扰乱主控制器一侧的电路。

图4模数转换中光电耦合器隔离的PC总线

模数转换器РC接口(图4)

工业和医疗仪器可能要求在混合信号和数字电路之间实现光学隔离。如果医疗仪器传感器/探头接触到高电压,那么在模拟传感器和微控制器/数字信号处理器之间需要安全电气绝缘。大多数电气隔离的目的是断开数字电路和模拟电路之间的任何接地环路,因为未隔离的接地可能会在系统中导致很高的背景噪声,影响模数转换精度。

I2C总线在模数转换器芯片和微控制器之间提供了一个方便的接口。市场上已经能找到内部包含FC接口的模数转换器。

一个双通道光电耦合器(如HCPL-063L)可以隔离从MCU/主器件到ADC/从器件的时钟和SDAout传输,一个单通道光电耦合器(如HCPL-O6OL)把 SDAin、从ADC/从器件传输到MCU/主器件上。隔离的DC/DC转换器可以从数字系统中导出电源,为模数转换器和两个光电耦合器另一侧的Vdd1-GND1供电。

总之,在设计光学隔离I2C总线并行的时钟和数据信号时,要求考虑到光电耦合器传播延迟和偏差性能。具有开路–集电极输出的光电耦合器可以简便地直接连接到IP℃总线线路上。光电耦合器本身固有的光学耦合和电气隔离区间可以实现的极高的抗电磁干扰能力,帮助保证设备可靠性及能够满足EMI标准。

审核编辑:汤梓红

-

控制器

+关注

关注

114文章

17877浏览量

195095 -

PC总线

+关注

关注

0文章

8浏览量

9117 -

IC总线

+关注

关注

0文章

8浏览量

7414

发布评论请先 登录

设计新知:低成本隔离式3.3V到5V DC/DC转换器的分立设计

确保光学隔离的3.3V IC总线中的数据完整性

确保光学隔离的3.3V IC总线中的数据完整性

评论