S分段C覆盖并行加法器

第一章:设计

经过学习,行波进位加法器RCA和超前进位加法器CLA后。

自己动手设计一个八位二进制加法器。

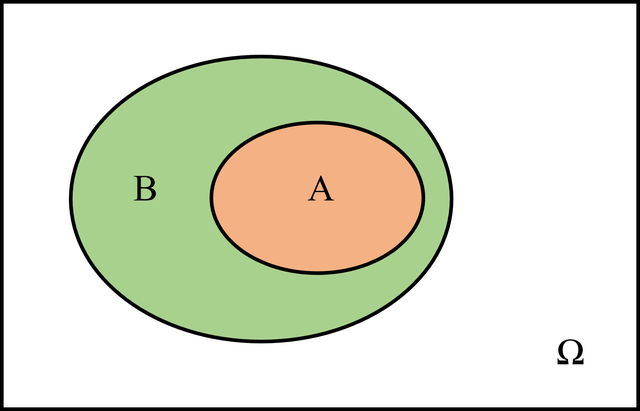

经过分析,二进制加法,可以分成三种情况。

A:最特殊情况,两个八位二进制数的相同位,不同时为1,这样就不会产生进位。

B:特殊情况,两个数相加,产生进位C,但是更高一位的S是0。

Ω:普通情况,产生进位后,需要继续进位的情况。

对于A:8个半加器就可以输出正确答案。

对于B:8个半加器输出S和C,用Cn和Sn+1异或,就可以输出正确答案。

对于Ω:就需要发现规律。

当低位C向高位S进位时,有两种情况。

S=0,则直接进位。

S=1,则本位异或为0,进位C向更高位,继续进位,直到遇见S=0。

所以需要一种灵活的电路,当S=1时,能够把低位C搬运到高位去。

把S组成的0111结构称为段,C=0时,异或出结果0111。C=1时,异或出结果1000。进位将是向段进位的。

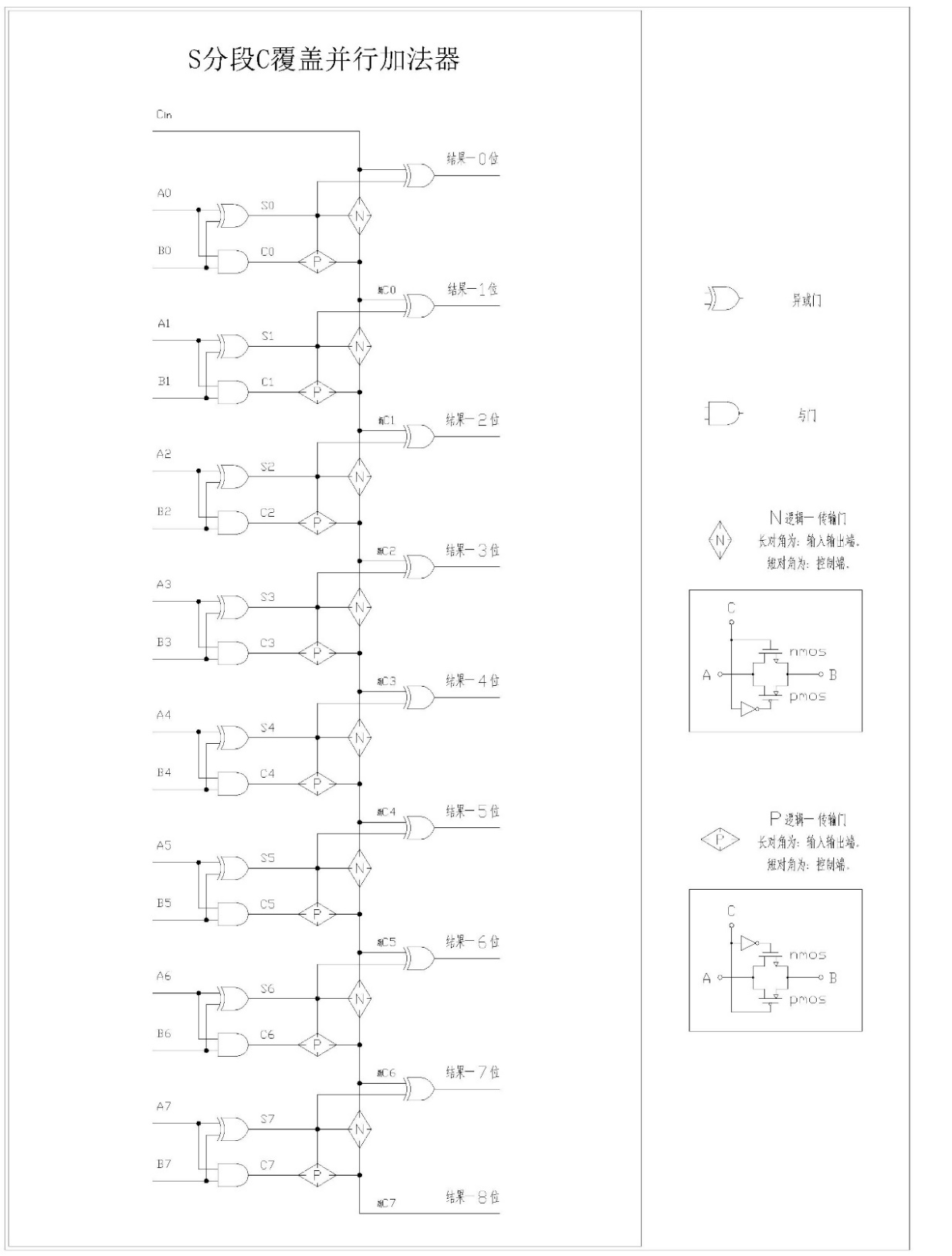

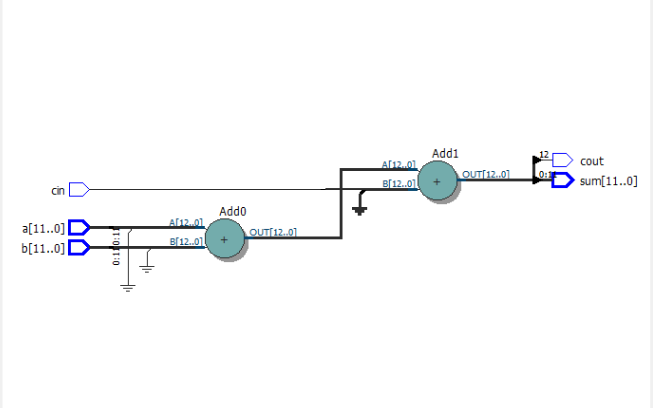

下图就是最终电路设计。使用八个串联的传输门,由各位的S控制通断,灵活分配进位C。

由于低位C为1,向高位进位,S为0时,N逻辑传输门截止,P逻辑传输门导通,本位C可以通过P逻辑传输门进入到下级异或门参与运算得到运算结果;当S为1时,N逻辑传输门导通,P逻辑传输门截止,此时本位C无法参与下级异或门运算,低位C则可以通过N逻辑传输门进入下级异或门参与运算,直到遇到S=0时停止。低位C和段内S异或运算,得到计算结果。依次从低位到高位看S的值,从S为1开始到S为0,称之为一段,此段内的所有C都会被低位C(本级S为1的上一级C)“覆盖”,结果为新C。当S出现极端情况0111...0结构的段时,最低位的C覆盖所有高位C参与运算。

计算机是如何计算的(视频有利于理解设计)

1探索篇

2设计篇

3优化篇

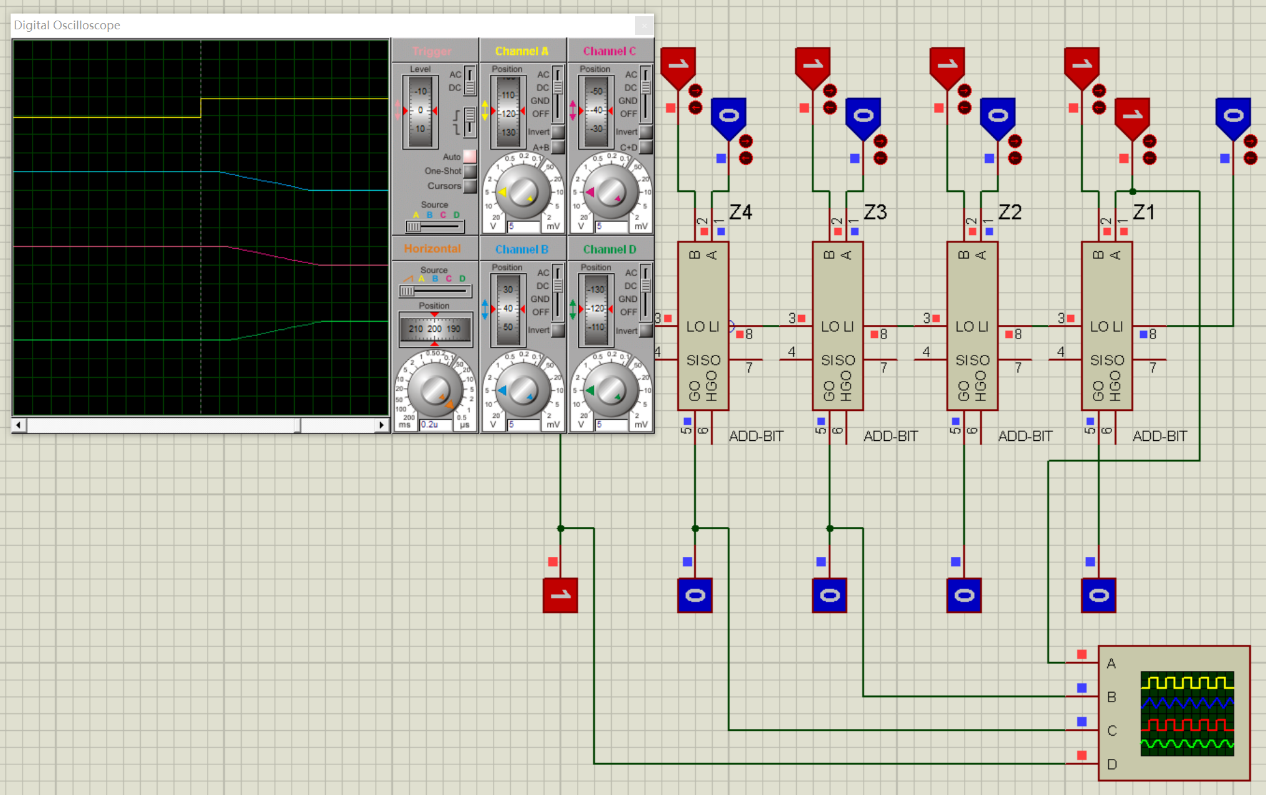

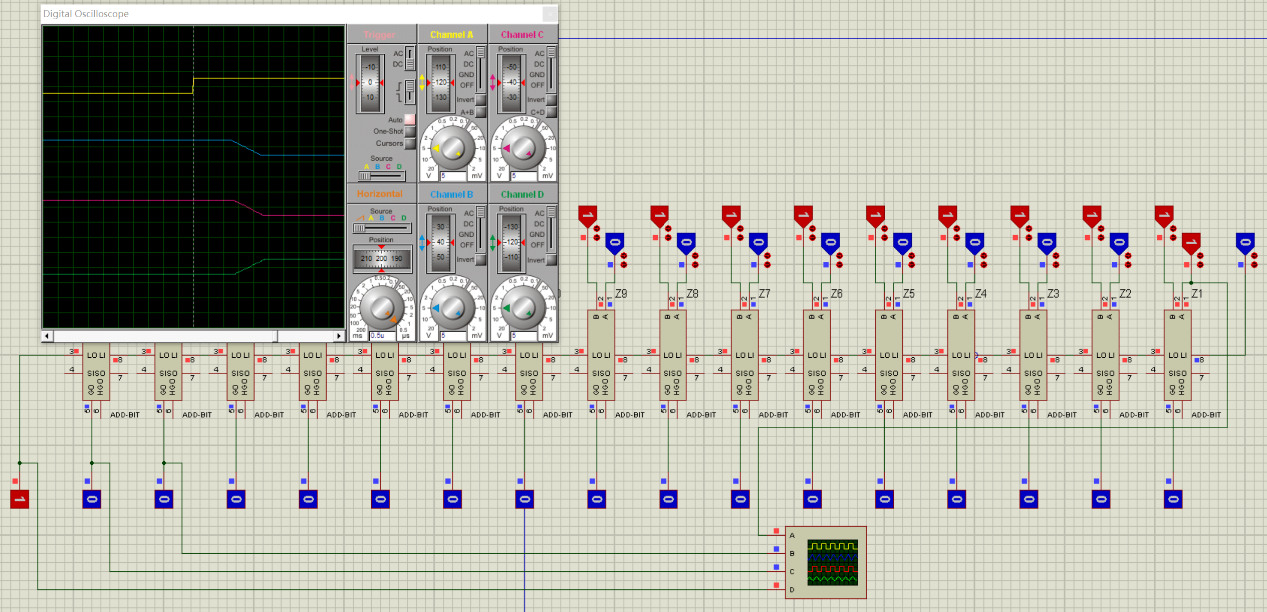

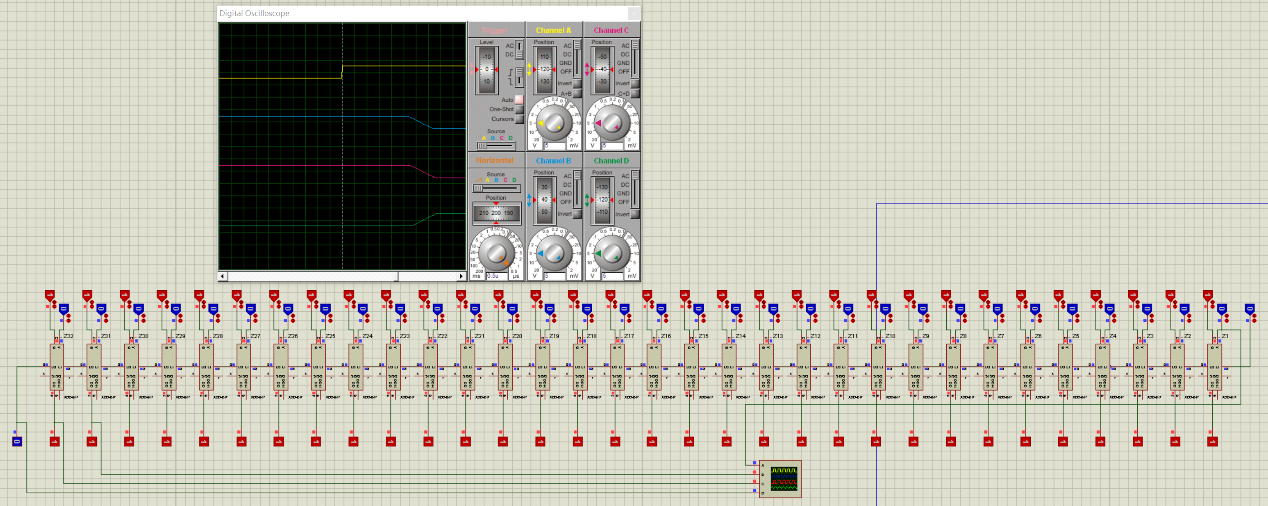

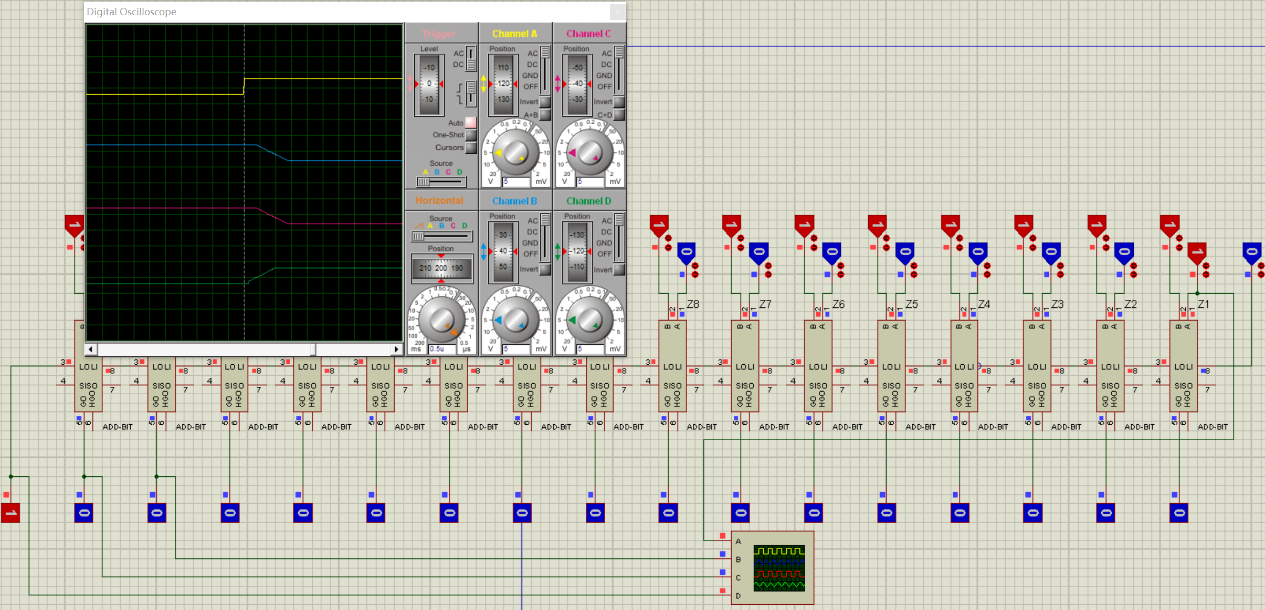

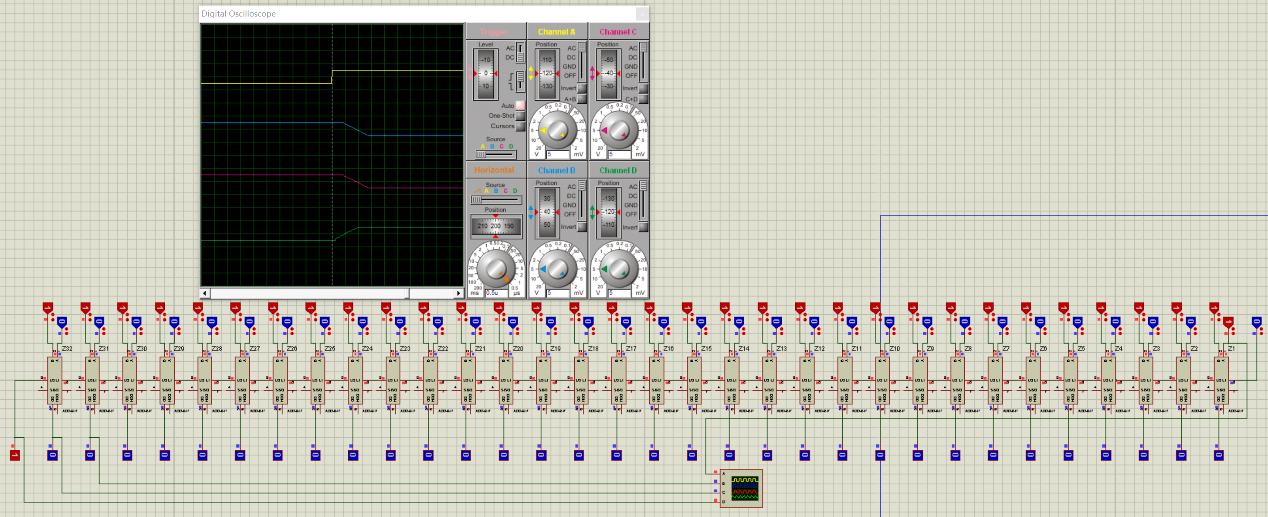

经过Proteus 7.8的验证,设计的加法器,能够计算出正确结果。

使用虚拟示波器测出RCA和SCA(本设计)的延迟时间:

| 加法器延迟 | 4位 | 8位 | 16位 | 32位 |

| RCA | 1.3微秒 | 1.64微秒 | 2.4微秒 | 3.8微秒 |

| SCA | 1.4微秒 | 1.4微秒 | 1.4微秒 | 1.4微秒 |

RCA:

SCA:

以上是,Proteus7.8的测试结果

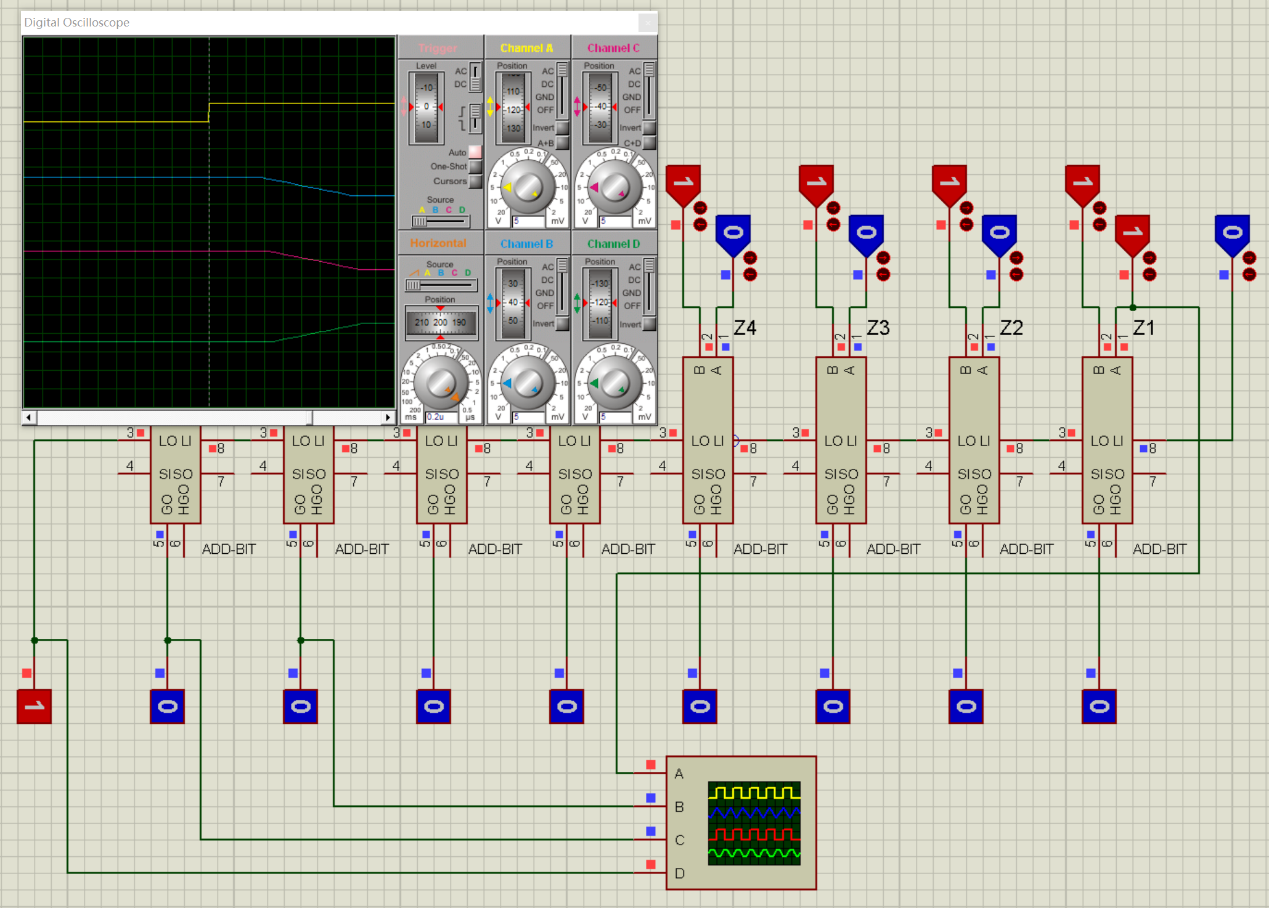

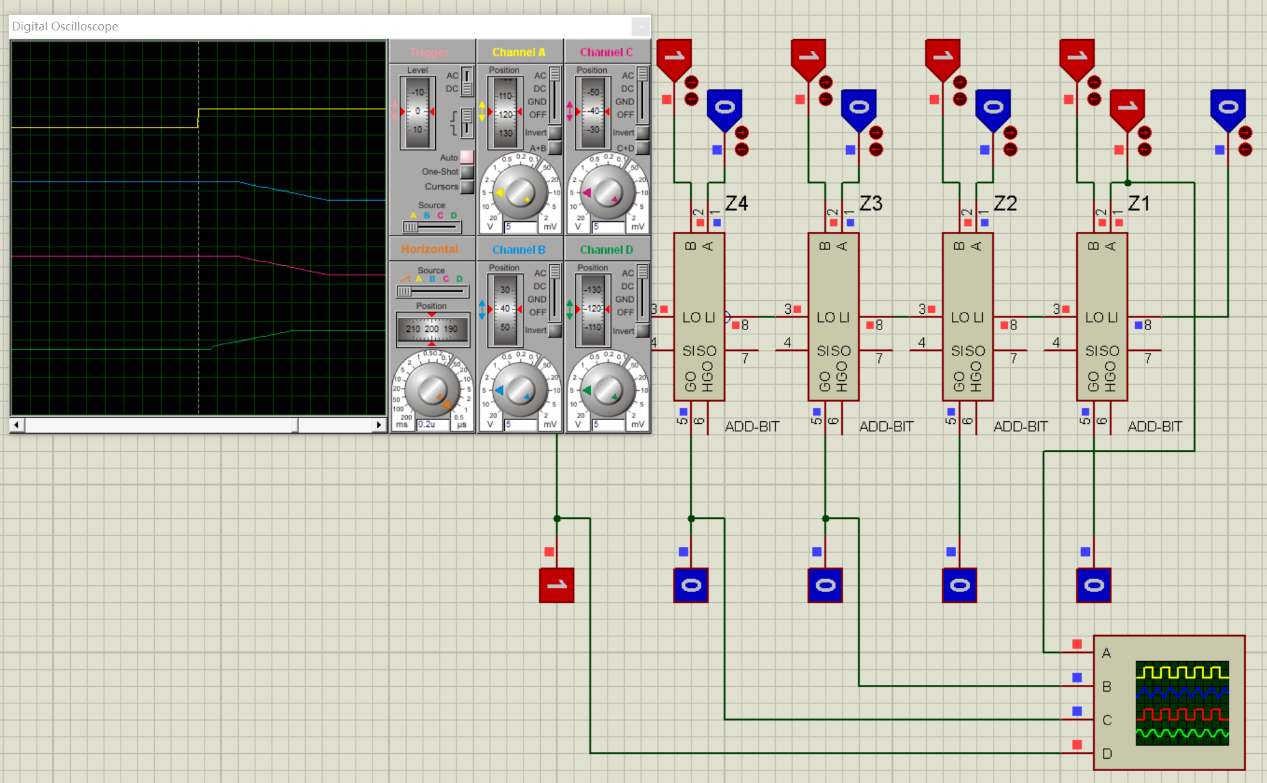

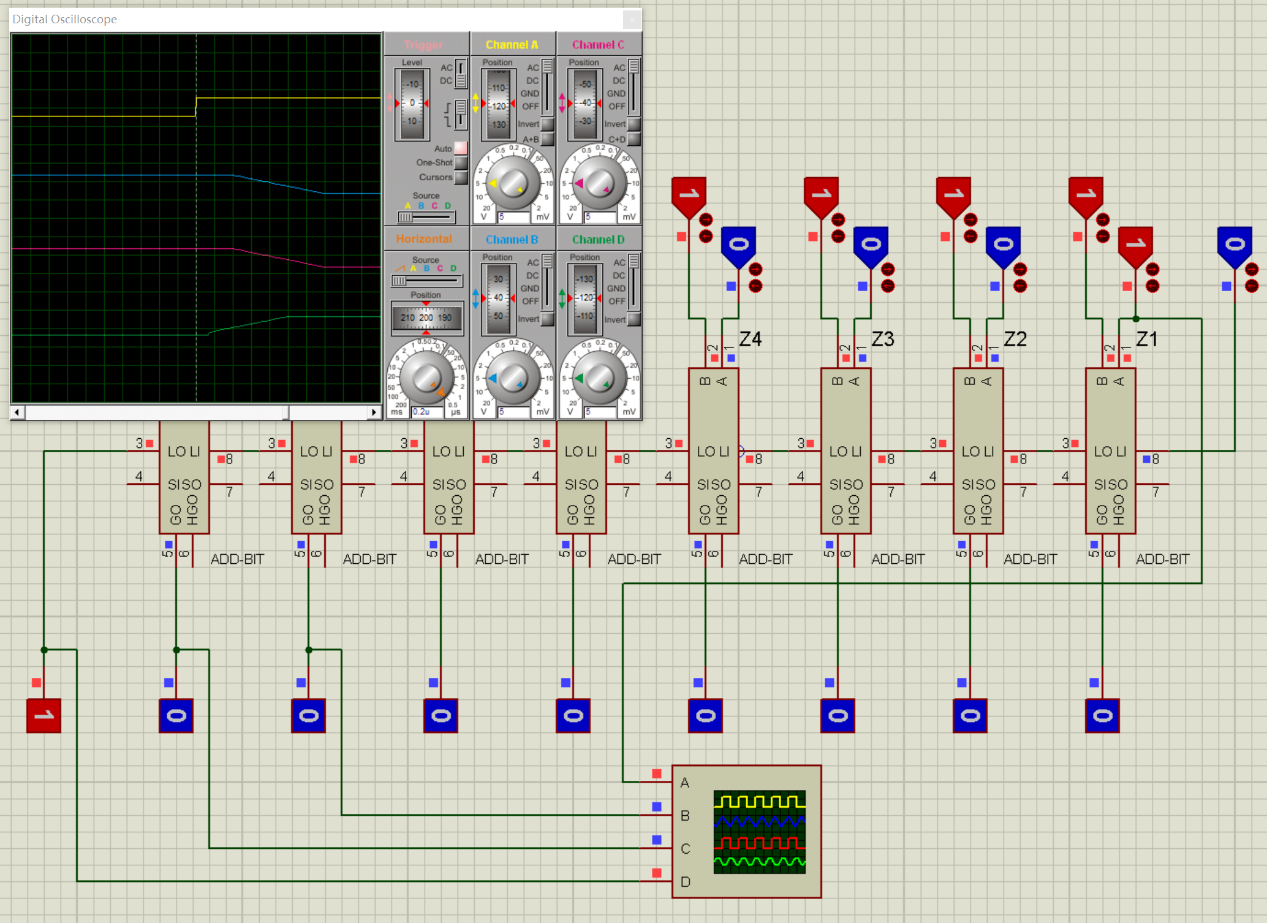

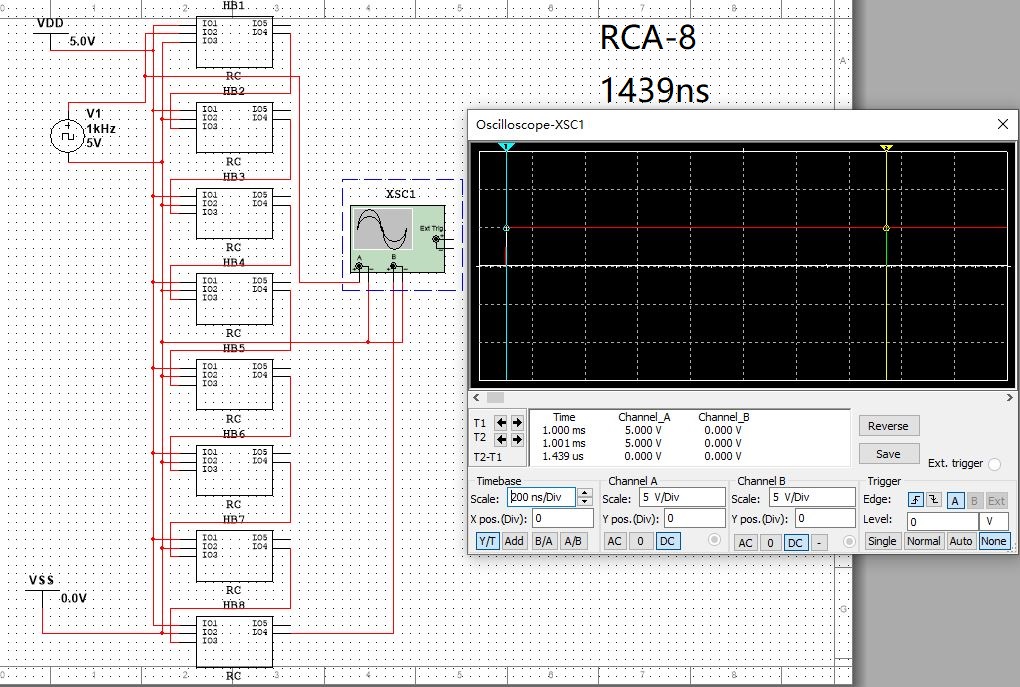

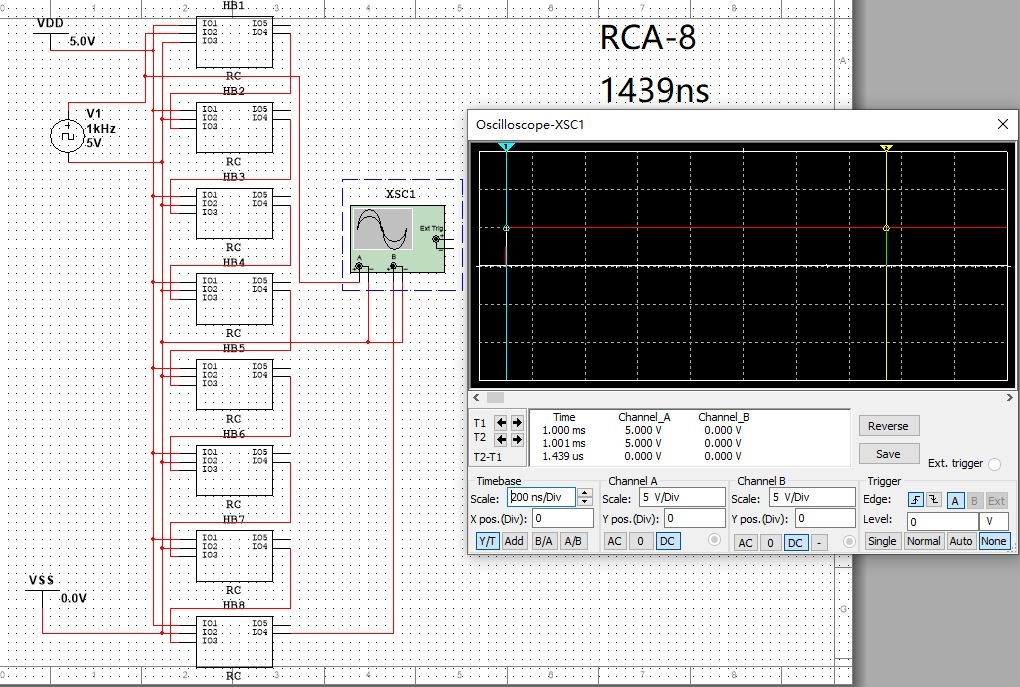

第三章:multisim验证。示波器测延迟

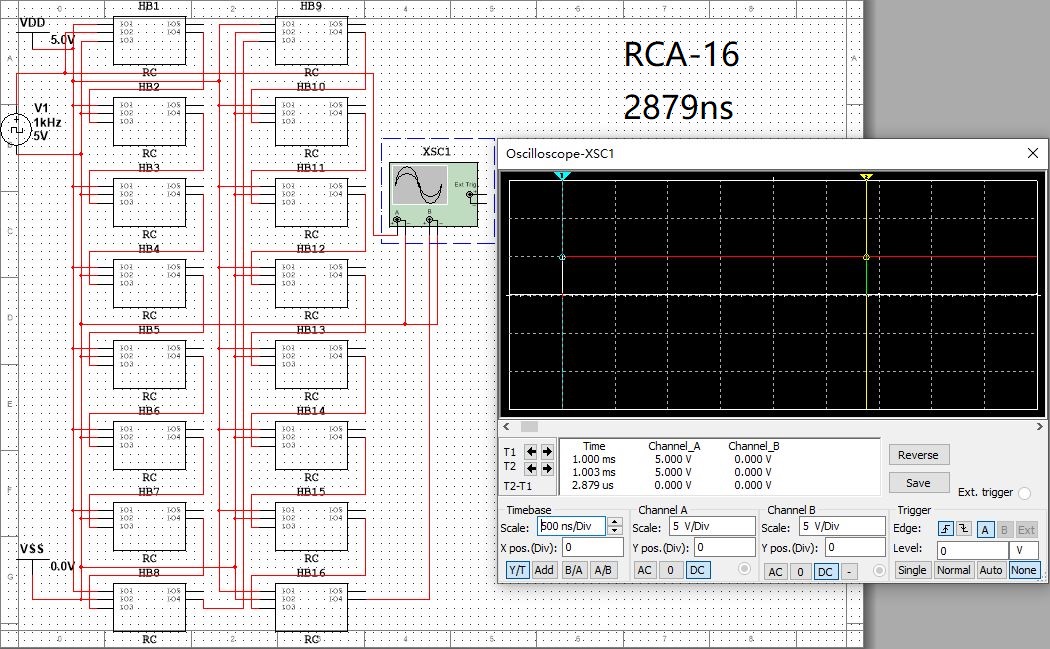

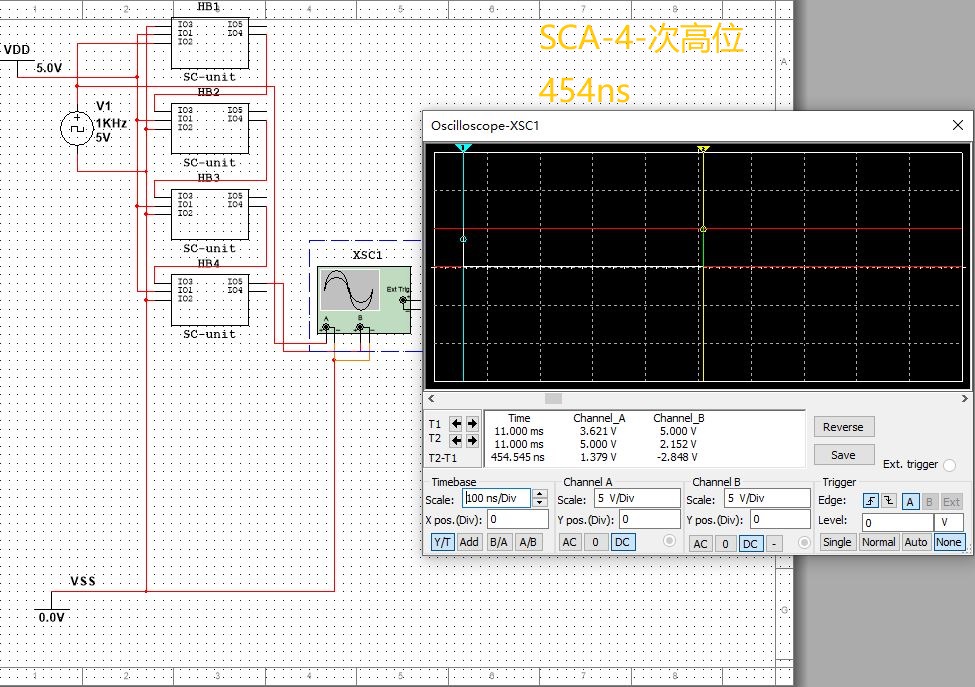

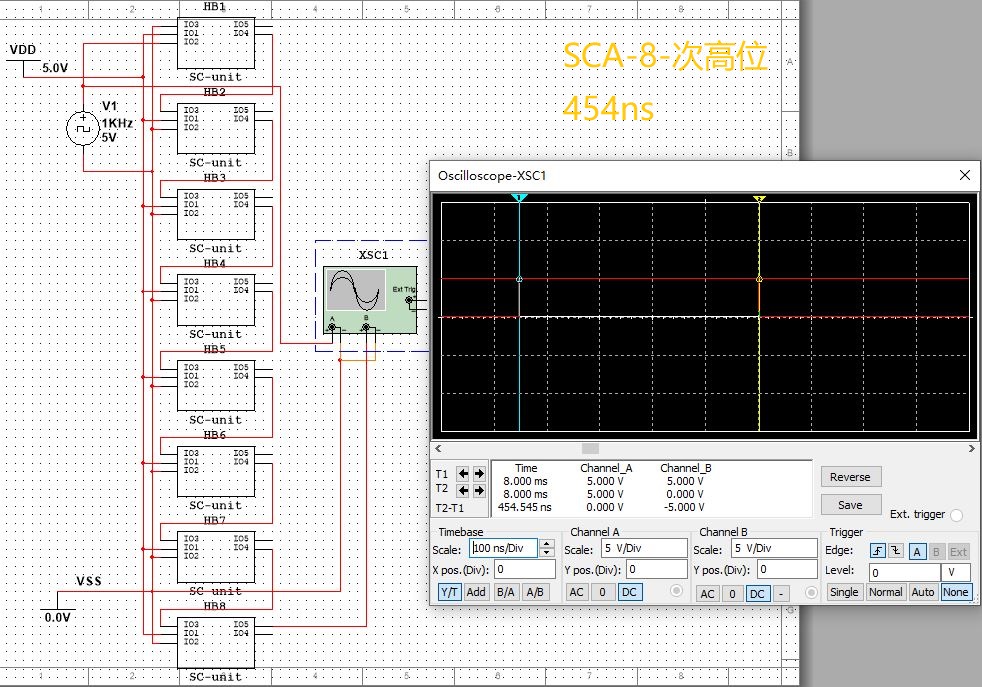

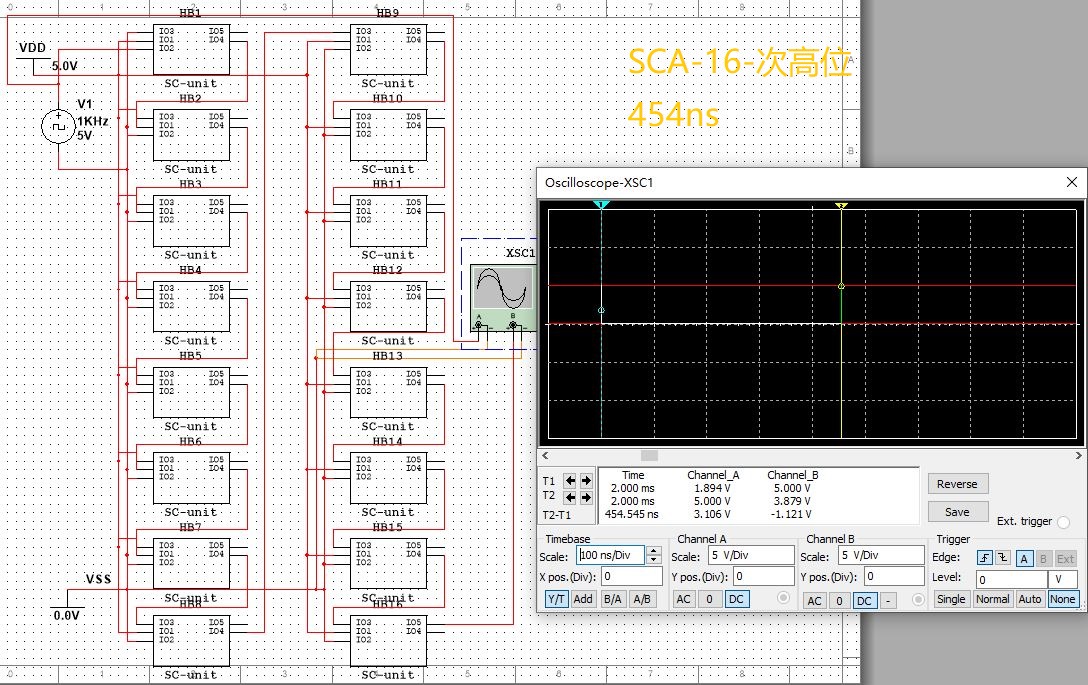

使用multisim 14的虚拟示波器测出RCA和SCA(本设计)的延迟时间:

| 加法器延迟 | 4位 | 8位 | 16位 |

| RCA | 723纳秒 | 1439纳秒 | 2879纳秒 |

| SCA | 454纳秒 | 454纳秒 | 454纳秒 |

RCA:

SCA:

以上是,multisim 14的测试结果

第四章:PCB实物验证延迟

由于模拟软件的延迟测试,仅仅只能参考。

计划利用74HC系列芯片,制作出RCA和SCA(本设计)的PCB电路板。使用示波器对两种加法器进行对比。

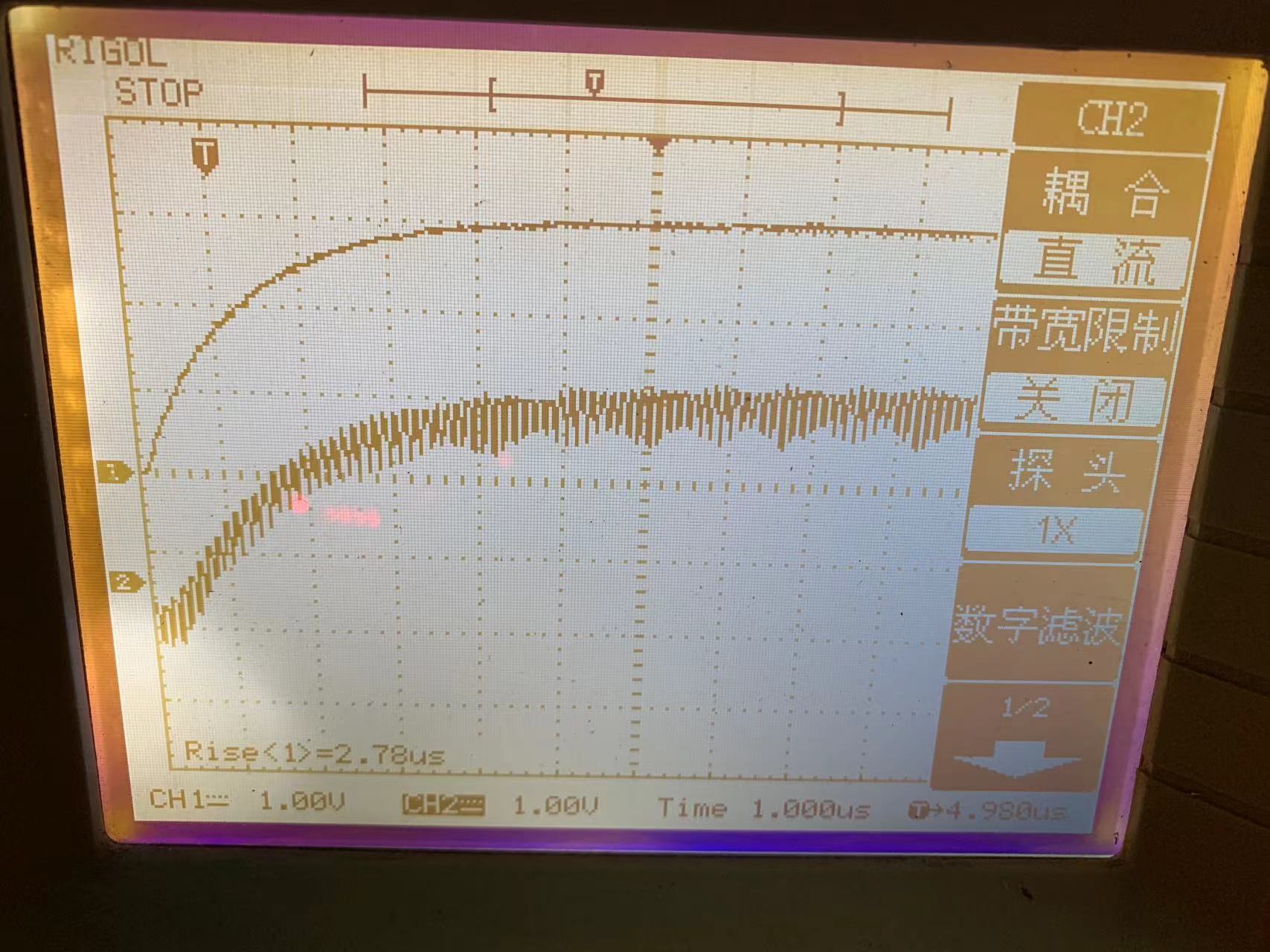

SCA-4示波器测延迟:

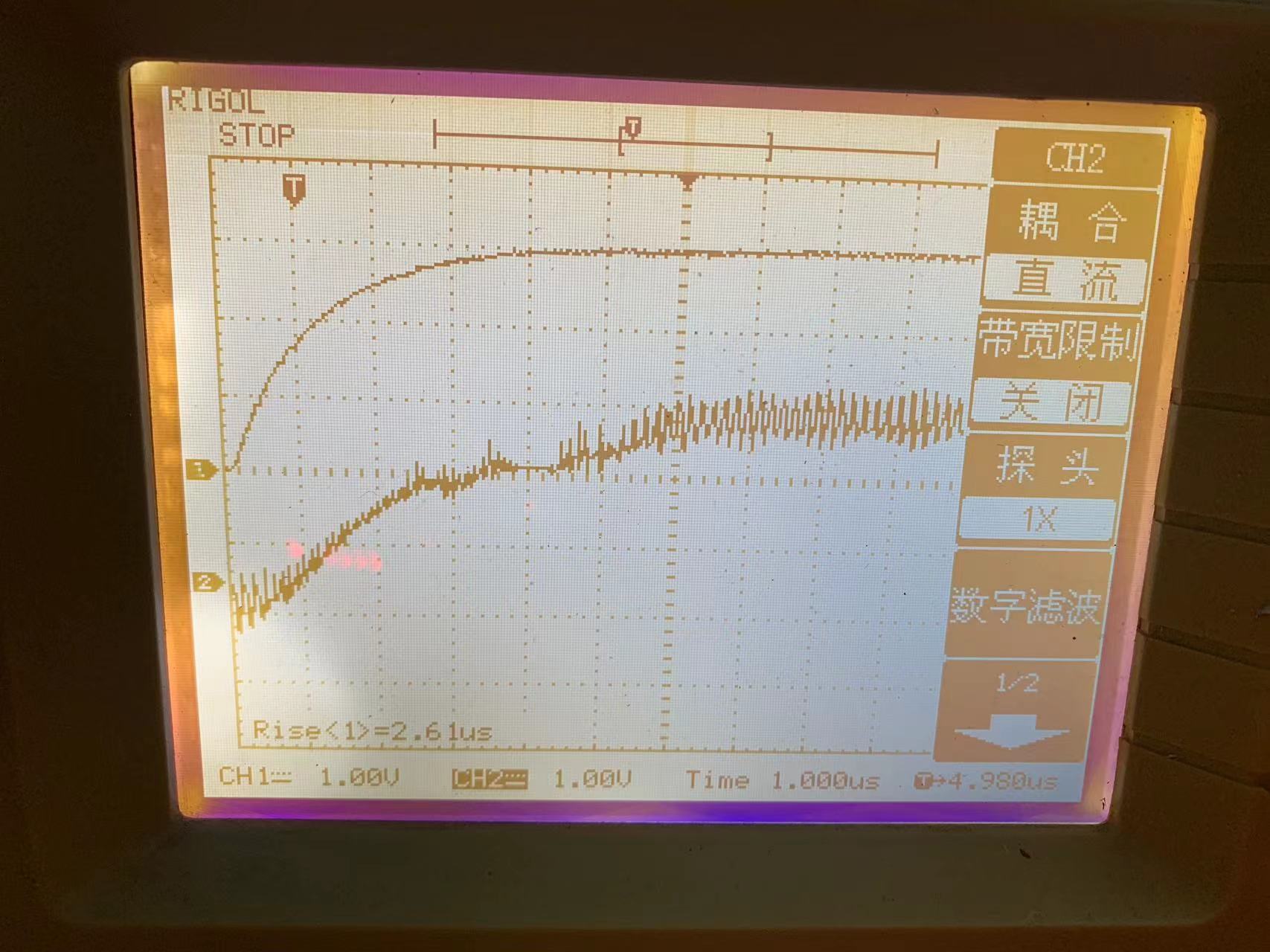

RCA-4示波器测延迟:

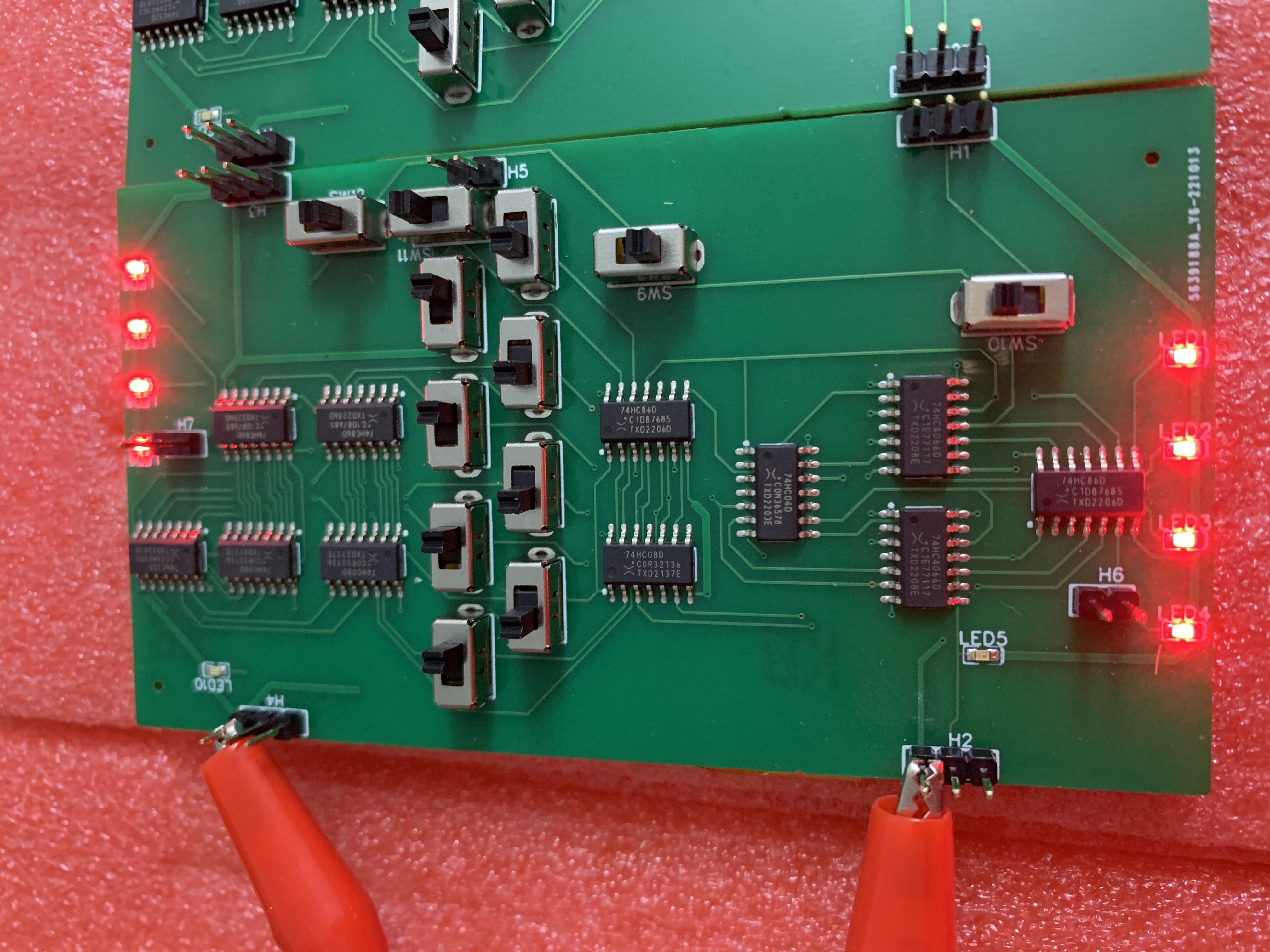

实物图:

中间两行是输入开关,为A1-4,B1-4D的输入,SW9为Cin。

上半部分的5颗芯片,组成RCA-4,

下半部分的6颗芯片,组成SCA-4。LED输出结果。

开关向右波动为3V,开关向左波动为0V。

图中A为1111,B为0000。输出LED显示1111。

结果正确。

已经试过所有的4位加法,全部正确。

审核编辑:汤梓红

-

电路设计

+关注

关注

6676文章

2454浏览量

204520 -

Proteus

+关注

关注

79文章

1692浏览量

106637 -

加法器

+关注

关注

6文章

183浏览量

30141

发布评论请先 登录

相关推荐

十进制加法器,十进制加法器工作原理是什么?

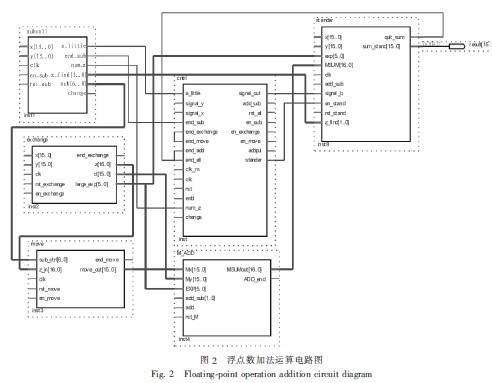

FPU加法器的设计与实现

同相加法器电路原理与同相加法器计算

怎么设计一个32位超前进位加法器?

怎样测量加法器的速度?器件延迟的时间长度!

怎样测量加法器的速度?器件延迟的时间长度!

评论