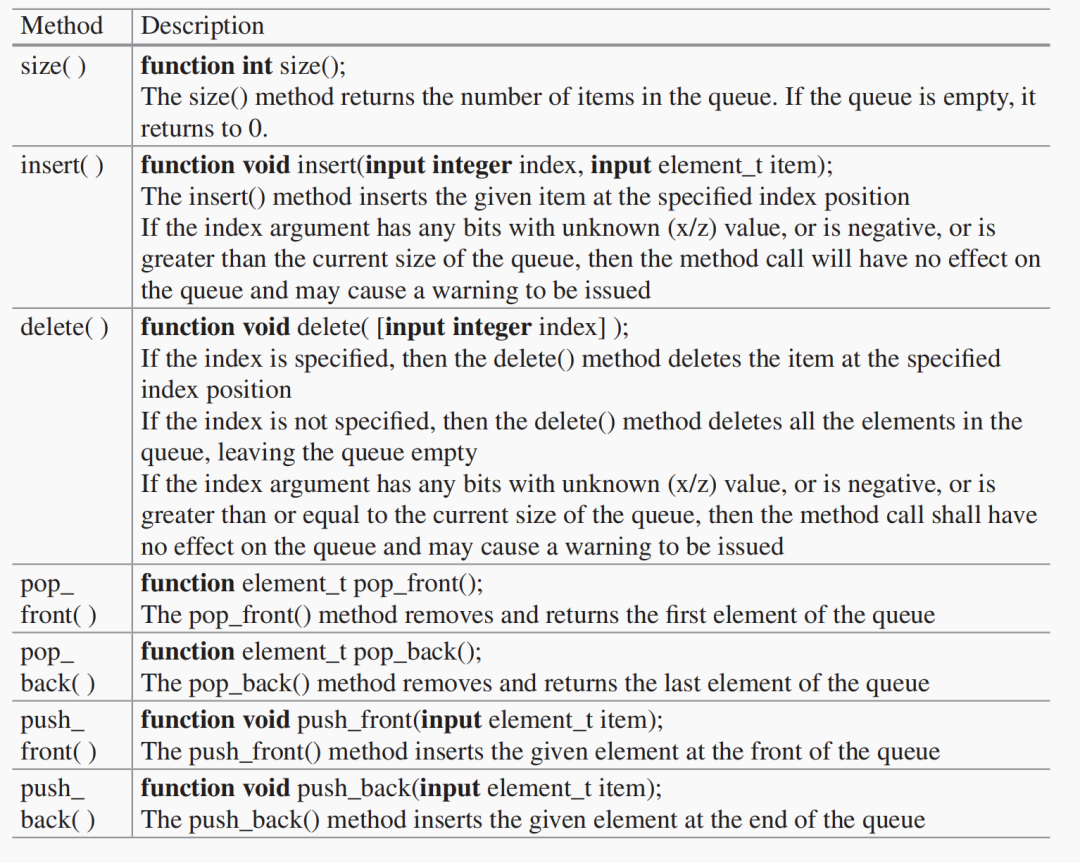

队列提供了许多内置方法。如下表所示:

module dq;

bit[7:0] dq1[$]; // A unbounded queue of unsigned 8-bit

int q3[$:5] = {0,1,2,3,4,5}; //bounded queue

int a;

initial begin

a = dq1.size( ); //empty queue

$display ($stime,,, "empty dq1 size = %0d",a);

dq1[0] = 0; dq1[1] = 1; dq1[2] = 2;

$display ($stime,,, "dq1 SIZE = %0d",dq1.size( ));

$display ($stime,,, "dq1=",dq1);

dq1.insert (3,3); //index, value

$display($stime,,, "After Insert dq1 SIZE = %0d",dq1.size( ));

$display ($stime,,, "dq1=",dq1);

dq1.delete (3); //index

$display ($stime,,, "After delete dq1 SIZE = %0d",dq1.size( ));

$display ($stime,,, "dq1=",dq1);

a = dq1.pop_front( ); //pop frst entry of the queue

$display ($stime,,, "dq1 pop front = %0d ",a);

$display ($stime,,, "dq1=",dq1);

a = dq1.pop_back( ); //pop last entry of the queue

$display ($stime,,, "dq1 pop back = %0d ",a);

$display ($stime,,, "dq1=",dq1);

//push the frst entry of the queue with '4'

dq1.push_front(4);

$display ($stime,,, "push front dq1=",dq1);

//push the last entry of the queue with '5'

dq1.push_back(5);

$display ($stime,,, "push back dq1=",dq1);

q3_size = q3.size + 5; //size > q3 size

//underfow : pop from index 6,7,8,9,10 – run time Warning

for (int i = 0; i < q3_size; i++)

$display($stime,,,"q3[%0d] = %0d", i, q3.pop_front( ) );

end

//Solution for underfow - check for size before pop

while (q3.size( ) > 0)

$display($stime,,,"q3 = %0d", q3.pop_front ( ));

//overfow : push over the bound limit – run time Warning

for (int i = 0; i < q3_size; i++) begin

q3.push_front( i );

$display($stime,,,"q3[%0d] :: q3 = %p", i , q3);

end

endmodule

仿真log:

0 empty dq1 size = 0 //empty queue size

0 dq1 SIZE = 3 //size after providing values to frst three elements

0 dq1='{'h0, 'h1, 'h2} //assigned frst three elements

0 After Insert dq1 SIZE = 4 //Insert value 3 at index 3.

0 dq1='{'h0, 'h1, 'h2, 'h3} //shows inserted value

0 After delete dq1 SIZE = 3 //delete value at index 3

0 dq1='{'h0, 'h1, 'h2} //shows dq1 after deletion

0 dq1 pop front = 0 //pop the front index of the queue

0 dq1='{'h1, 'h2} //dq1 after element at index 0 is gone (popped)

0 dq1 pop back = 2 //pop the back (last) index of the queue

0 dq1='{'h1} //the last index/value is gone

0 push front dq1='{'h4, 'h1} //push at the front of the queue (value 4)

0 push back dq1='{'h4, 'h1, 'h5} //push at the end of the queue (value 5)

上面我们通过队列dq1展示了push和pop的行为。然后我们声明了有界队列q3,最大的index限制是5,所以这个队列最大的size是6.

将队列q3初始化为{0,1,2,3,4,5},然后pop超过6次。

q3_size = q3.size + 5; //size > q3 size //underfow : pop from index 6,7,8,9,10 – run time Warning //Queue 'q3' is empty after index 5. for (int i = 0; i < q3_size; i++) $display($stime,,,"q3[%0d] = %0d", i, q3.pop_front( ) ); end

这个时候仿真器会上报warnnin:

# RUNTIME: Warning: RUNTIME_0219 testbench.sv (54): Cannot pop from an empty queue.

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

仿真器

+关注

关注

14文章

1053浏览量

88208 -

Verilog

+关注

关注

31文章

1374浏览量

114730 -

System

+关注

关注

0文章

166浏览量

38838

原文标题:SystemVerilog中的Queue Methods

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

SystemVerilog中的“const”类属性

SystemVerilog中可以将类属性声明为常量,即“只读”。目的就是希望,别人可以读但是不能修改它的值。

发表于 11-29 10:25

•2589次阅读

Some Programming Methods for I

Some Programming Methods for Increasing the Operating Speed of PLC Program

Absbad With Mitsubishi

发表于 01-19 12:42

•15次下载

SystemVerilog的断言手册

SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

发表于 07-22 14:12

•20次下载

ThreadX(九)------消息队列Queue

消息队列QueueAPItx_queue_createtx_queue_deletex_queue_flushtx_queue_front_sendtx_queue_receivetx_queue_send_notifyAPItx_queue_createtx_queue_deletetx_queue_flushtx_qu

发表于 12-28 19:35

•2次下载

SystemVerilog中$cast的应用

SystemVerilog casting意味着将一种数据类型转换为另一种数据类型。在将一个变量赋值给另一个变量时,SystemVerilog要求这两个变量具有相同的数据类型。

SystemVerilog中的Semaphores

SystemVerilog中Semaphore(旗语)是一个多个进程之间同步的机制之一,这里需要同步的原因是这多个进程共享某些资源。

Systemverilog中的Driving Strength讲解

在systemverilog中,net用于对电路中连线进行建模,driving strength(驱动强度)可以让net变量值的建模更加精确。

SystemVerilog中的Queue Methods

SystemVerilog中的Queue Methods

评论