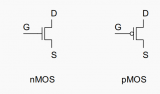

1、MOS的基本性质

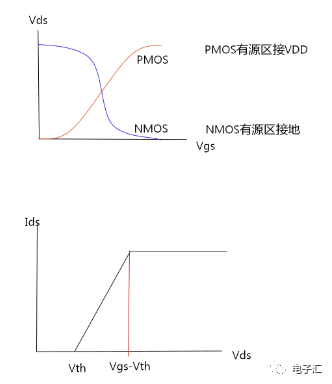

MOS,即场效应管,四端器件,S、D、G、B四个端口可以实现开和关的逻辑状态,进而实现基本的逻辑门。NMOS和PMOS具有明显的对偶特性:NMOS高电平打开(默认为增强型,使用的是硅栅自对准工艺,耗尽型器件这里不涉及),PMOS低电平打开。在忽略方向的情况下,采用共S极接法,有如下特性:

第一张图是Vds随Vgs变化的情况,用于描述开关特性。后面的逻辑分析一般基于这个原理。

第二张图是Ids随Vds变化的情况的简图,用于描述MOS的静态特性。

MOS的静态特性由两个区域决定:线性区和饱和区。

前者一般是动态功耗的主要原因,后者是静态电压摆幅的决定因素。

线性区有:Id=μCoxW/L[(Vgs-Vth)Vds-1/2Vds^2]

饱和区有:Id=1/2μCoxW/L(Vgs-Vth)^2

后面的MOS器件一般基于这两个区域的电学特性来分析总体的电学特性。电压摆幅、面积、噪声容限、功耗、延时基本上都是源自这个区域的原理。

2、CMOS电路及其改进

(1)最基本的CMOS电路--反相器

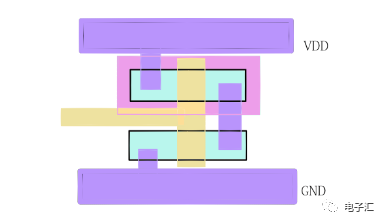

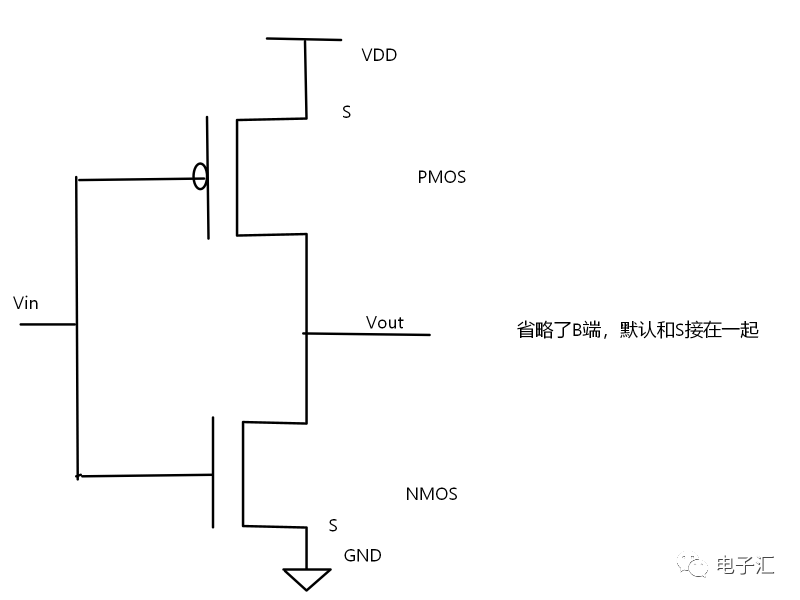

这里是反相器的版图草图及电路草图,用于描述反相器的版图位置和逻辑关系。

反相器的功能很简单,就是将Vout输出为Vin的反向。

从功耗上看:PMOS和NMOS静态不存在同时导通,即无静态功耗。由于NMOS和PMOS关断的延时,存在动态功耗。

从电压摆幅上看:NMOS可以将Vout拉到L0(逻辑0),PMOS可以将Vout拉到L1,可以保证全电压摆幅。

从面积上看:PMOS和NMOS各一个,标准的CMOS面积,其他电路的面积以其为参考。

从噪声容限上看:CMOS的标准噪声容限,以其为参考对比其他电路。

从延时看:取决于MOS管的工艺,也是其他电路延时的参考。

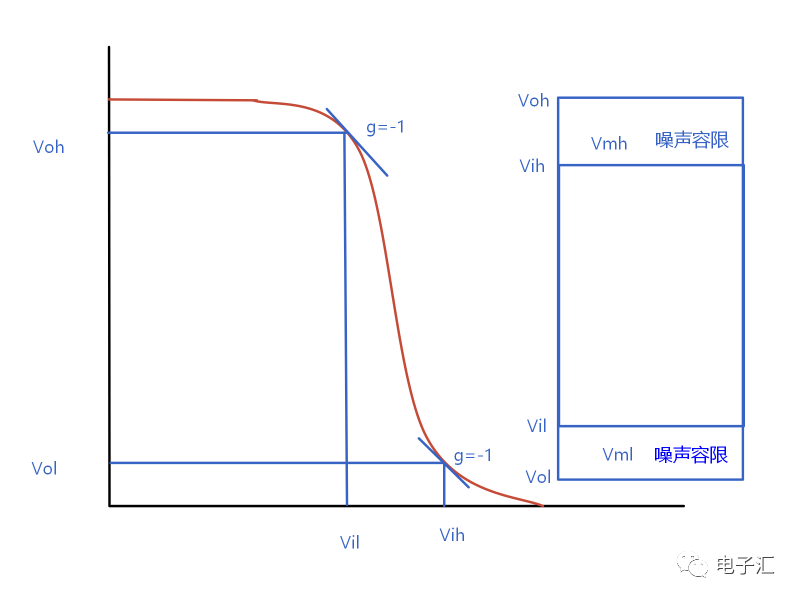

小知识:噪声容限的定义

图中g代表斜率,两个噪声容限在对称情况下一般相等,有些特殊的设计需要不对称的噪声容限。可以看到,噪声容限越大,反相器变化越快,响应速度越快。

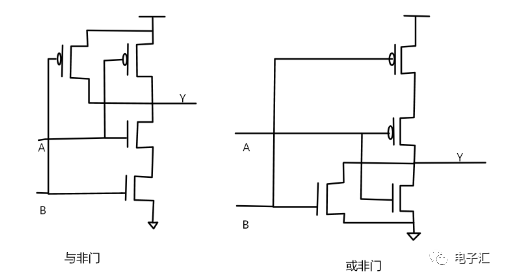

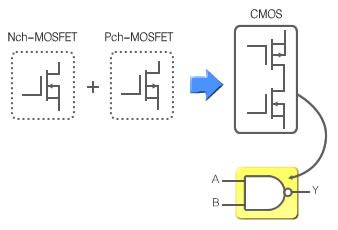

(2)与门和或门的CMOS实现

使用CMOS实现逻辑,需要的理解上拉网络和下拉网络:

上拉网络:标准CMOS中采用PMOS组成上拉网络,负责实现L1的电压。

下拉网络:标准CMOS中采用NMOS组成下拉网络,负责实现L0的电压。

CMOS中,通过上拉网络和下拉网络的互斥来保证静态下无直通电流,即上拉网络和下拉网络的导通状态总是相反。这意味着上拉网络和下拉网络存在对偶关系---串联对并联。

再关注一个网络的导通关系:

串联的NMOS需要两个输入均为L1,输出才能完成下拉L0,即Y=AB,不完全与逻辑。

并联的PMOS需要两个输入均为L0,输出才能不完成下拉L0,即Y=A+B,不完全或逻辑。

所以,CMOS的与逻辑和或逻辑如下:

由于以NMOS为串并联参考,所以构建的逻辑需要取非。

这个相对于反相器而言,主要是拓展了N网络和P网络,这是后面改进及CMOS与其他电路组合的基础。

由于篇幅问题,这里不再详细描述该电路的特性,只是补充一下扇入和延时之间的关系。

以与非门为例:

A连的MOS(暂称MA)的有源区S不是接地,即Vs被抬高(在Vb=0)。Vth将会随之变高,导致导通所需时间增加,增加延时。这就是扇入为2的状态。一般来说,扇入不宜超过4,否则延时会快速增加。

(3)CMOS改进

CMOS的改进方针就是减少或去除PMOS,主要的思路如下:

使用电阻(或者类似电阻功能的器件如恒通MOS管)替代PMOS。问题:下拉时为有比电路,需要设计管子尺寸以保证达到L0的电压要求。

使用差分信号驱动NMOS代替PMOS。问题:会多一组反相器和与原来PMOS相当的NMOS。

使用DCVSL结构实现CMOS。动态过程中为有比电路,需要设计PMOS的尺寸。

前面两种比较好理解,就不过多说明了,主要关注第三种结构DCVSL的实现原理。

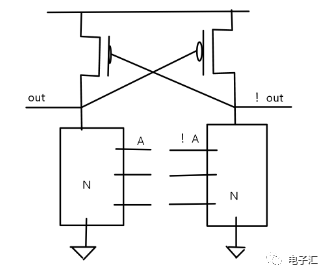

DCVSL,全名差分级联电压开关逻辑,用两个PMOS和两个对偶的互斥输入的NMOS实现逻辑功能,具有使用少量PMOS的优点,支持差分输出。

这就是DCVSL的结构,下面的两个N网络输出为互斥的信号,通过上面两个PMOS的加强实现输出的稳定。基本原理是下面两个N网络总会有一个导通,输出L0,L0使得上面两个PMOS中一个导通,抬高另外一个PMOS的输入使其关闭,实现信号的稳定。实现稳态的过程为有比电路,存在稳定延时。

这个电路与直接使用差分信号输入一个上拉网络为NMOS的结构的区别(也就是第二种思路)的区别在于无需承受上拉NMOS带来的电压摆幅的损失。

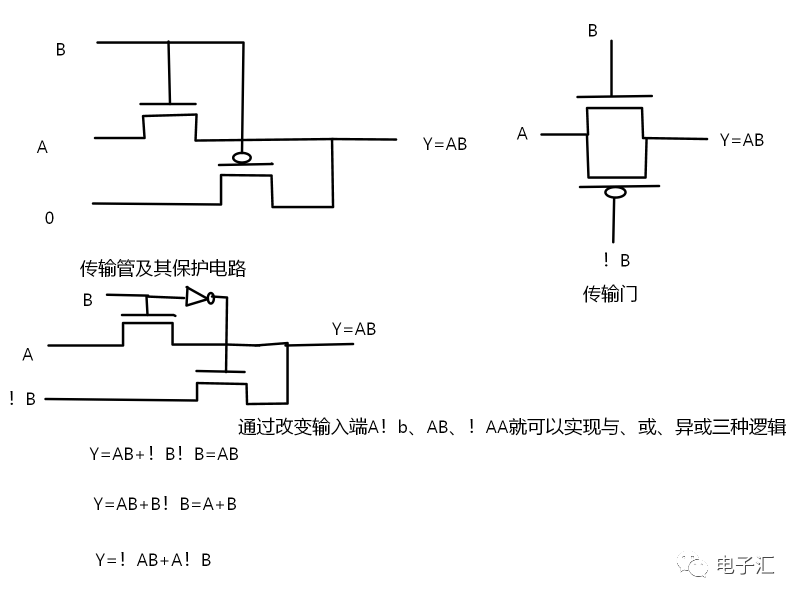

3、TG及其改进

(1)传输管逻辑

传输管和传输门的区别在于否是有全电压摆幅,其实现的逻辑功能是一致的。

可以看到,传输管实现逻辑的关系还是串联和并联,并且串联为与,并联为或,需要使用保护电路防止悬空。输出的逻辑与输入的信号有关,这可以作为可编程的电路的单元。

(2)TG逻辑的改进

TG逻辑的改进还是专注于去除PMOS。根据反向输入的NMOS等于PMOS的思路,如上图3中的结构,可以将PMOS替代。可以看到的传输管不能无损传输,信号需要使用反相器恢复稳定。

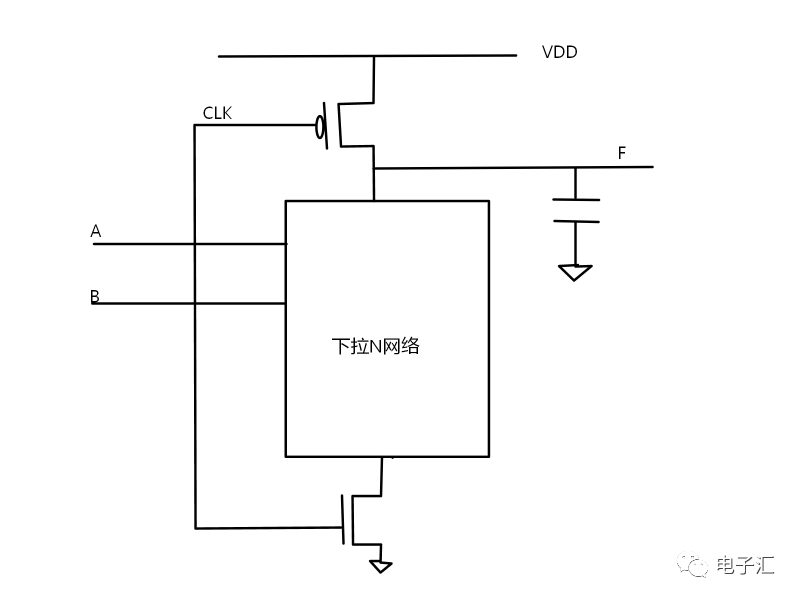

4、动态电路

静态电路需要保持上拉和下拉电路一直互斥,存在动态损耗。

动态电路的思路则是使用时钟信号保证上下电路互斥,这样只需要一个网络就可以实现目标功能。图中是下拉N网络的电路,还可以使用上拉P网络实现,两者的级联要求正好对偶,可以间隔连接。这就是动态电路的级联的形式一PN连接。还有一种方式就是使用多米诺电路,就是在同N或者同P之间使用反相器保证动态电路预充正确。

接下来说明动态电路的工作方式:

预充-求值

在CLK=0时,P导通,输出预充到1;

在CLK=1时,N导通,读取N网络的导通状态,决定求值为0或者1;

一次预充求值完成后即实现逻辑输出。

问题:求值时输入不能发生改变,否则会出现逻辑x,这意味着动态电路多与时序电路联合使用,构成流水线。

问题:电容存储电荷实现电平存在损耗,需要CLK不断刷新。

动态电路的优化:

第一级动态电路CLK需要P和N两个MOS管,对于第二级动态电路,预充时已知某个信号为0(多米诺为0,PN连接为1),如果输入逻辑为与或者可以保证网络关闭,则可以节约一个网络控制MOS管。

5、组合逻辑分析

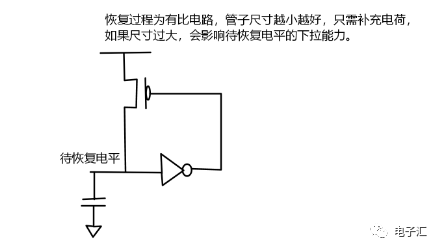

(1)电压摆幅

电平需要能够维持在L1和L0两个状态区间内,一旦混乱,就会出现逻辑错误。一般来说,可以使用电平恢复电路维持电压(一个反相器与PMOS构成的电平恢复)。对于长的逻辑链,需要加入BUFF来维持电压(这点在传输管中尤为重要)。

(2)逻辑延时

这部分是分析组合电路的延时的,采用的反相器为标准的估算方法(软件可以实测,但是设计时需要估值),专业词汇叫逻辑努力。

标准反相器链的延时T=tp0+tp0*f,其中tp0是空载延时,f是扇出。f=Cout/Cin,在同尺寸的反相器串联时,f=1,并联时f=N,N为下一级并联的个数。常用术语FO4即是扇出为4的设计。对于不同的

反相器,则需要使用具体的计算得到比例。反相器链采用f=F^(1/N)的优化规则优化。

基于反相器链,可以推导CMOS门链的延时:

反相器常用P:N的W/L为2:1(综合面积,速度,噪声,功耗的考虑值),以此为基准可以推出同等最优尺寸的与非门尺寸为2:2:2:2,或非门尺寸为4:4:1:1,推算原则就是串联翻倍,并联不变的最优尺寸等效规则。

然后是CMOS门的延时:d=p+gh,p为基准延时tp0的倍数,g为电学努力,h为逻辑努力。

以与非门为例,得出下面的参数:

p=2(等效两个理想反相器),g=4/3(A=2+2,B=2+2),h=Cout/Cin(单链,如果有分支,加上b这个参数,即下一级的负载数)。

优化的方法也是一样的,使得f=F^(1/N),即可实现最优延时。f=gh,F=GBH,大写即为连乘的小写。

6、锁存器

限于篇幅,这里不再再画图,大致解释一下锁存器的结构:

类似一个时钟控制开关(一般使用传输门作为开关),时钟打开开关时读取数据,关闭时锁存数据。通过时钟信号实现输出数据在一段时间内(理想情况下为半个周期)与输入隔离。

7、触发器

由两个锁存器和中间一个存储单元(一般是首尾相连的反相器)组成。锁存器的锁存时间相反,输入端锁存器打开时存入数据,锁存时读出数据。与锁存器整个时钟周期都在锁存依靠电平不同,触发器依靠时钟的上升和下降实现数据的存储,且输出整个时钟周期不发生改变。

8、时序逻辑分析

建立时间:数据需要提前于时钟沿的时间,

保持时间:数据需要在时钟沿到来后保持的时间。

传输时间:数据从存储单元传输到输出所需的时间。

具体的分析是复杂的,但是基本的原理是清晰的。建立时间是为了保证数据能够存入存储单元。保持时间是保证数据能度过时钟触发所需的延时。传输时间是保证存储单元数据能够传输到输出。

具体的时序分析是很复杂的,需要考虑许多参数,如时钟的抖动和歪斜。一般这些参数都是计算好的,使用者只需根据计算值设计相应的满足条件即可。基本的修改方法是:

对于关键路径,建立时间不足降低时钟频率,保持时间不足加BUFF。

至于如何修改建立时间和保持时间,那是电路结构的问题,需要设计更加合理的电路。常用的电路结构为C^2MOS结构,即将时钟和反相器组合成的MOS时序电路,有兴趣可以查一下。这个结构可以和多米诺组成流水线的结构。

9、功能模块

加法器、乘法器、多路选择器、移位寄存器、存储器等具有特定逻辑功能的电路所需的是逻辑设计,学习过数字电路的都不会陌生(存储器就是基于存储单元的读写DRAM和基于电容的SRAM),这里已经到了module层次了。这个层次的设计已经可以使用verilog快捷的实现了。优化也可以基于verilog来调试优化每个门的位置和数量。

10、总结

本文从MOS管开始,基本详细地介绍了CMOS的原理,传输管TG的原理、动态电路的结构、组合逻辑延时的分析,简略地介绍了锁存器、触发器及时序电路的分析,联系到了模块层次的数字电路设计,粗浅地介绍了数字电路设计的各个层次,为以后提高数字电路设计能力打下了一定的基础。

审核编辑:汤梓红

-

CMOS

+关注

关注

58文章

5721浏览量

235605 -

MOS

+关注

关注

32文章

1272浏览量

93847 -

数字电路

+关注

关注

193文章

1606浏览量

80652

原文标题:数字电路之MOS设计

文章出处:【微信号:电子汇,微信公众号:电子汇】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高速数字电路设计

数字电路比模拟电路的优点

数字电路的基础概念:MOS晶体管

数字电路之MOS设计

数字电路之MOS设计

评论