很明显,热量将成为半导体未来的限制因素。已经有很大一部分芯片在任何时候都是黑暗的,因为如果所有东西同时运行,所产生的热量将超过芯片和封装消散该能量的能力。如果我们现在开始考虑堆叠模具,在这种情况下,提取热量的能力保持不变并且热发生器的数量增加,那么这似乎是一个相当暗淡的未来。

也许有人会发明更好的晶体管,或者电阻和电容更小的电线。但在这一点上,更明显的进步已经被探索出来,成本总是会限制一些解决方案。

在过去的 40 或 50 年中,优化一直与性能和面积有关。大约在 20 年前,功耗才开始成为一个考虑因素,当时人们意识到,在相同的基本架构下,性能的每一个百分比的提升都伴随着更大的功耗提升。Dennard 扩展自动停止在每个新节点上提供相同水平的节能也无济于事。

即使在今天,当我采访人们并询问电源是否是主要的优化考虑因素时,答案通常是,“我们必须首先满足性能指标,然后我们才能担心降低功耗。” 在接下来的 10 年里,我预计这种心态将转变为“功耗第一”的方法。真正的问题是,在定义的功率预算内,我可以在给定任务上获得多少性能?你不会通过首先查看性能来得到这个答案。

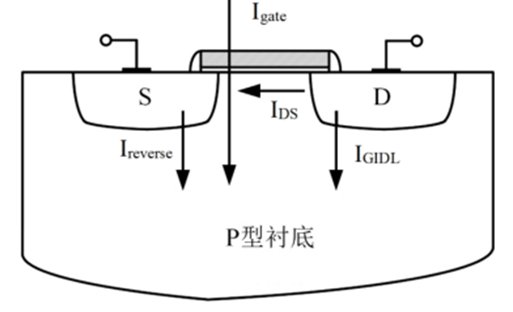

在过去的几十年中,已经创建了一些工具,这些工具可以通过对设计进行分析并找出潜在的节省来节省浪费的电力。大多数时候,这些节省可以自动应用,而不必担心搞砸任何事情。示例是具有松弛的路径或时钟门控的晶体管尺寸,当可以证明它不会产生逻辑影响时。其他策略的影响稍大一些,例如电源域切换,漏电流可以在不使用时分块消除。然而,这些确实增加了设计的复杂性,并且它们引入了一些潜在的灾难性问题,使一些设计陷入困境。

但所有这些技术都只是试图恢复浪费的电力。他们都没有正面解决这个问题。所需要的是影响系统架构的功率优化策略——包括在为它们优化的处理平台上运行的软件中使用和可能实现的算法,这些算法着眼于在系统中移动的每个数据字节的有用性,还有更多。

但是这个行业有如此多的动力和惯性,以至于改变是非常困难的。我们看到为一致性和连接性定义了越来越复杂和重量级的协议,所有这些协议都试图尽可能少地破坏当今存在的不良做法。

有令人鼓舞的迹象。特定领域的计算是由 John Hennessy 和 David Patterson 在 2017 年的 Turing 讲座,以及 RISC-V ISA 和围绕它的所有工作的快速行业采用所引发的一个领域。他们这样做的主要动机可能不是降低功率,但这至少是一个开始。

从 RTL 开始。当被问及以功率优化为主要考虑因素的未来可能性时,人们充满热情、兴奋和希望在未来以更好的方式做事。

20 年前,当电子系统级 (ESL) 一词被广泛用于定义 EDA 新时代的技术时,人们兴奋不已,也许是自行业成立以来我们在新 EDA 工具上看到的最大规模投资。

我也陷入了困境,但我们都错了。没有新的魔法抽象可以驱动新一代的设计师和工具。它确实产生了一些好东西,但与最初预期的完全不同。但我们现在能看到新时代的起源吗?主要关注电力和能源的新抽象、流程和工具?新一代设计将能够最大限度地提高每瓦性能,而不是通过优化,而是通过设计?

是否有足够多的人关心这个星球以将其作为优先事项?作为工程师,我们是否在某种程度上对我们创造的产品的能源消耗负责?我确实看到更多人关心这些事情,但我也看到许多完全浪费电源技术的进步,其中唯一的动机是利润。

编辑:黄飞

-

芯片设计

+关注

关注

15文章

1001浏览量

54811 -

eda

+关注

关注

71文章

2708浏览量

172868

原文标题:功耗,成为芯片设计的头号问题

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

低功耗SOC芯片的优势

Orin芯片功耗分析

栅极驱动芯片选型低功耗原因

一款4644芯片低功耗设计思路解析

TC387芯片通过MCD软件连接芯片时提示Device被锁定,如何解锁?

OTP低功耗语音芯片的工作原理与产品特性

如何解决芯片设计的功耗问题

如何解决芯片设计的功耗问题

评论