最近在公司碰到MOS驱动芯片损坏的问题,啃了一些资料后还算搞明白了点东西,来分享一些其中的基本原理吧。

应用于电机控制的MOS电路基本上都是桥式逆变拓扑,而目前有很多专门应用于这种场景的驱动芯片,基本上把最关键的的驱动控制结构集成在了内部,我们只要根据它推荐的外围电路来搭建就可以很完善的应用。

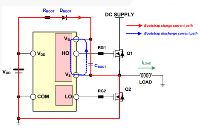

电路原理:

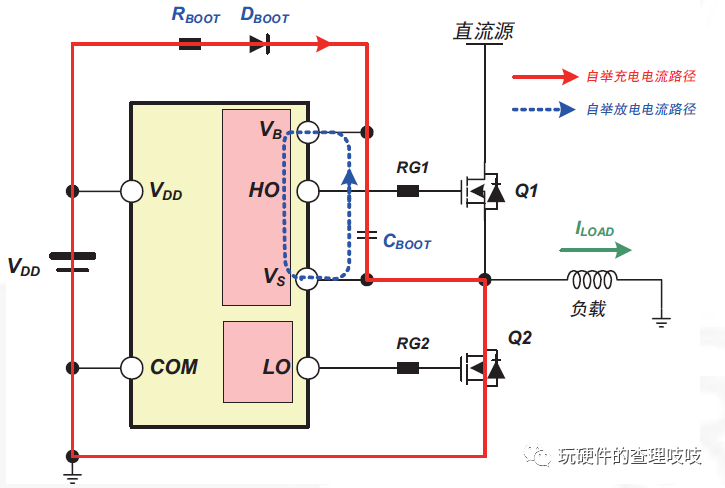

如上图 Q1,Q2作为上下管工作时只能有一个管子导通,同时导通会造成电源直接到地短路直接炸管。VS连接负载,电压是浮动的,当下管导通时,VS被拉到GND,也可以为负压Vn;当上管导通时,VS被拉到直流源主电压。

驱动MOS管完全导通的电压在15V左右,即MOS管的GS之间要保持15V左右的稳定压差。既然VS端是浮动的,那么Q1的栅极电压也应该叠加在VS上随着VS的变化而变化,让VGS的压差始终稳定,这样才能正常驱动上MOS管。如何保持这个压差呢,那就需要靠自举电容Cboot和自举二极管Dboot。

电路分析:

当下管Q2导通,自举电容通过自举二极管,被供电电压VDD瞬间充电。

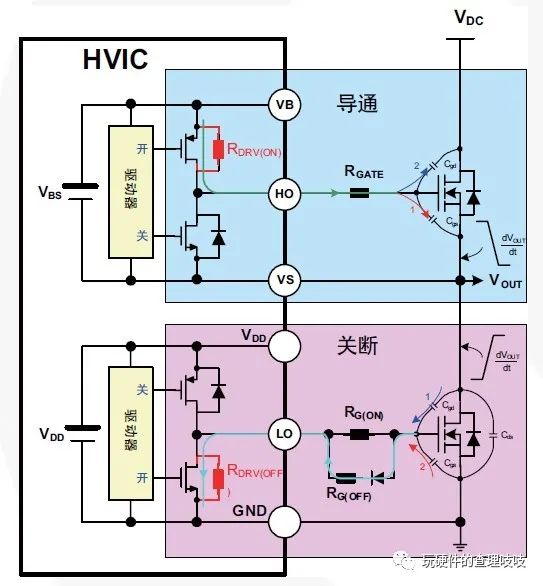

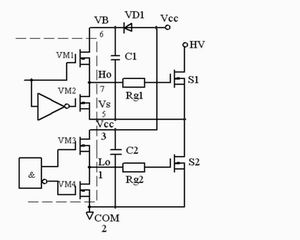

当驱动上管Q1导通时,驱动芯片内部的结构如下图,是也是一组上下MOS管控制输出驱动,通过导通内部上MOS,自举电容通过其给外部上管驱动GS供电,关断时内部下MOS导通,使得驱动外部的MOS管GS寄生电容有放电的路径,从而达到快速关断的目的。(电阻Rboot作用是充电周期内限流,二极管Dboot作用是在上管完全导通的时候,防止电容通过供电回路放电)。

整个电路的基本原理就是这样,但也会有两个问题:

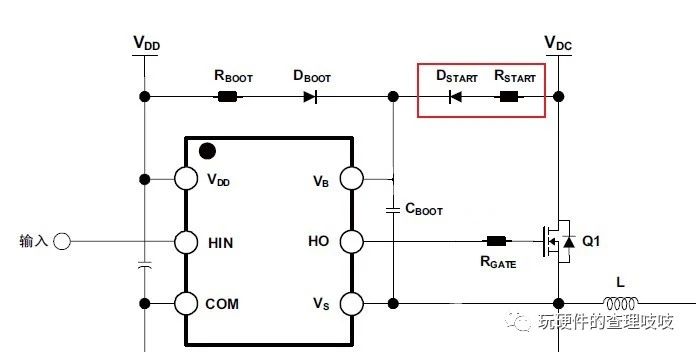

1.自举电容进行初始化启动和充电受限的问题

启动时,在某些条件下,自举二极管可能处于反偏,上管Q1的导通时间不足,自举电容不能保持所需要的电荷,从而使驱动能力不足。如图所示,在Vdc到自举电阻之间串联一个启动电阻Rstart,在上电时对自举电阻充电,可以解决这个问题。

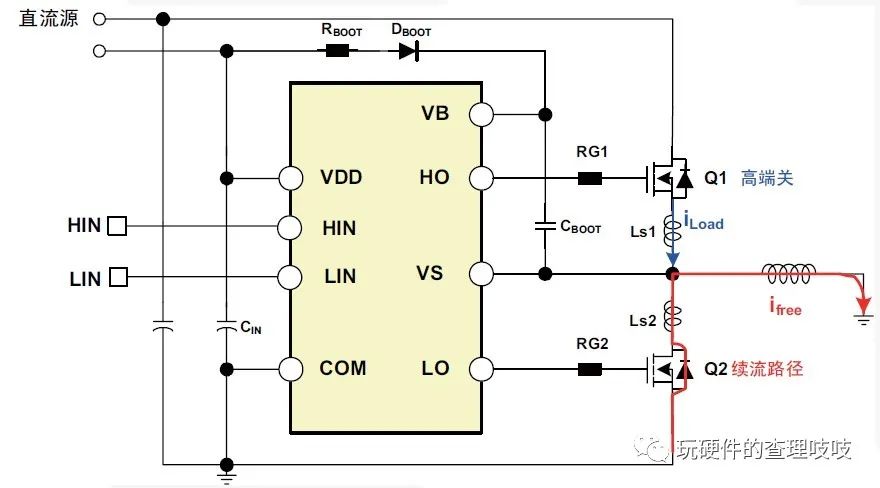

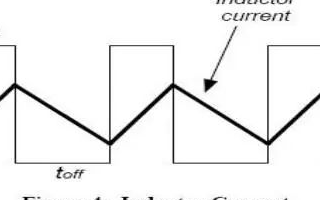

2. VS端产生的负压问题

上管断开的时候,我们的负载电机线圈会产生感应电动势,线圈中的电流会阻止电流的降低,于是瞬间切换到下管的体二极管上续流。由于寄生电感Ls1,Ls2的的存在,VS会感应出负压,这个值VS=-Ls*di/dt,幅值的大小取决于寄生电感Ls。

如果VS幅值过大,又会产生三个问题

①自举电容过压;Cboot的压降等于VDD-VS,VS为负压,相当于负压越大,电容两端承受的压差越大。

②当这个负压超过驱动芯片的极限电压,芯片也会损坏。

③上管Q1的Vgs=Vg-Vs,因为此时上管关断,所以Vg=0,也就代表着Vgs的幅值等于VS的绝对值,当这个值超过MOS管的门限阈值电压,上管就会导通,这时上下管同时导通,管子就会炸裂。

解决方案

①在自举二极管前面的限流电阻,取值不能太大,一般取5-10Ω,用来限制自举电容的充电电流,防止充电时电流过大损坏,同时可缓解VS端负压造成的影响。自举电容也可以并联一个稳压二极管,防止MOS管产生的浪涌电流造成损坏,同时让电容两端电压更稳定。

②在下管Q2的DS之间可以并联一个低压降的肖特基二极管。当上管关断时,VS产生的负压就会被钳位,一般管压降为0.7V。VS负压也就被限制在-0.7V。

总结:

1.由于上管的开启需要自举电容对其放电,为了保证上端的正常开关,需要调节PWM,给自举电容预留一段充电时间。

2.自举电容取值一般以无感或低感的电容为好,另外PCB布局上充放电回路要尽量短,减少走线的寄生电管,避免产生LC振荡。

3.自举二极管Dboot一般考虑导通电流和反向耐压值。自举二极管用于自举电容的充电,当上管开启时,它承受着MOS管漏极相等的电压,所以二极管反向承受电压要大于供电电压。如果VS为负压,反向耐压则>VP+负压 的电压之和。一般选用反向耐压和反向恢复时间性能都较好的快恢复二极管。

审核编辑:汤梓红

-

MOS

+关注

关注

32文章

1269浏览量

93688 -

驱动电路

+关注

关注

153文章

1529浏览量

108493 -

自举电容

+关注

关注

1文章

56浏览量

14787

原文标题:MOS自举式驱动电路原理

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

MOS自举式驱动电路原理

MOS自举式驱动电路原理

评论