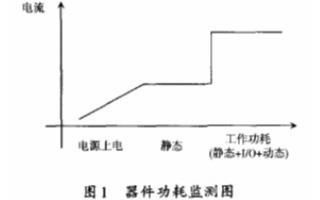

以前,在做数字硬件电路设计的时候,总听到说,CMOS数字电路静态时,基本没有功耗,但是当进行翻转时,功耗就上来了。

但是,为啥子呢?

今天,总算是明白了。

CMOS反相器算是CMOS数字电路中的基础电路,所以下面就以CMOS反相器为例,来看看原因。

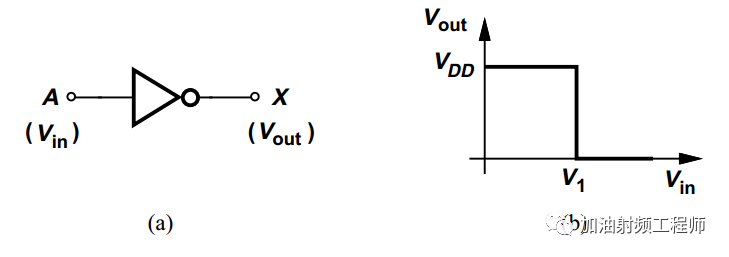

理想的反相器模型和电路特性如上图所示。

也就是,当Vin

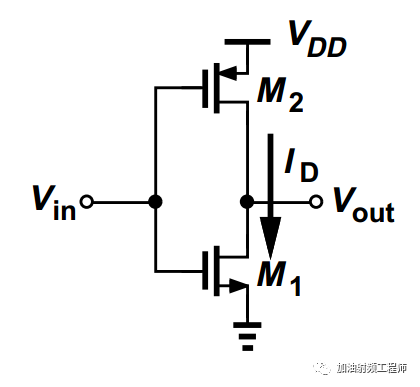

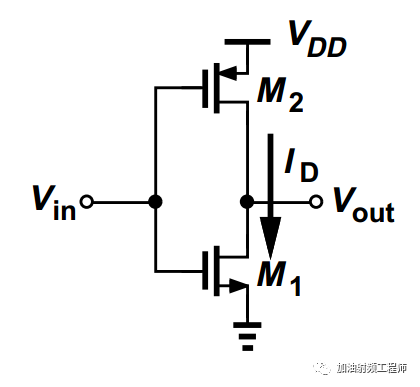

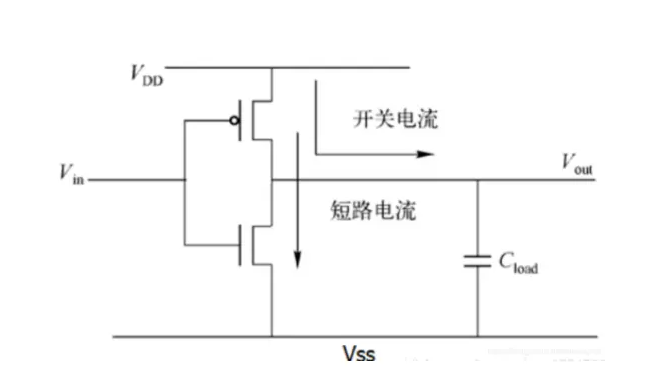

而反相器的内部电路如下图所示。

假设Vin也只有两个电平,0V和VDD。

从反相器的理想电路特性看的话,电路可以简单地将M1和M2看成开关电路,当Vin=0V时,M2打开,M1关断,此时Vout=VDD;当Vin=VDD时,M2关断,M1打开,此时Vout=0V。

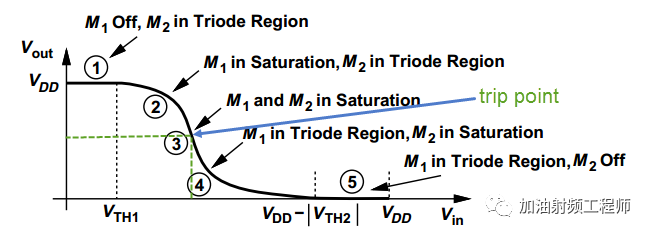

但是,仔细看看的话,上述的两种状态只是反相器开始和结束时候的状态。而在输入的电平从低到高变化时,M1和M2的状态经历了很多种。

需要注意的是,M1和M2晶体管,在所有情况下,流过的电流都相等,当然前提是反相器后面没有加负载。

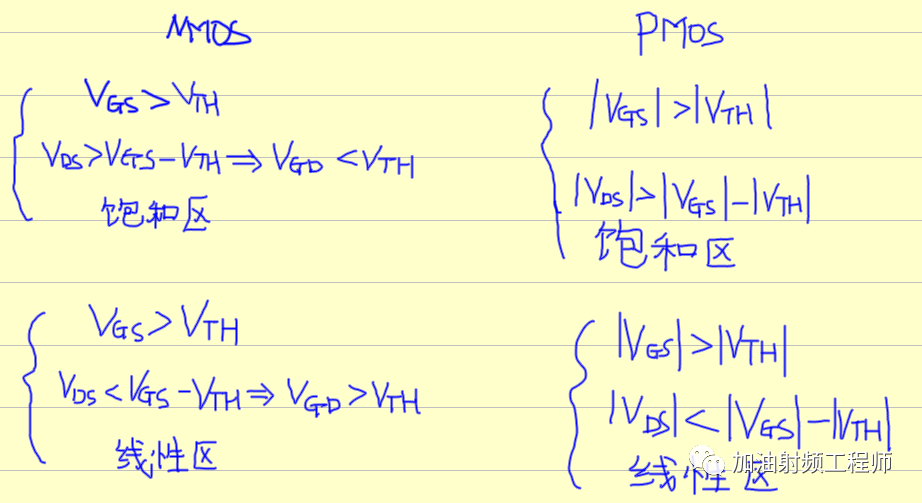

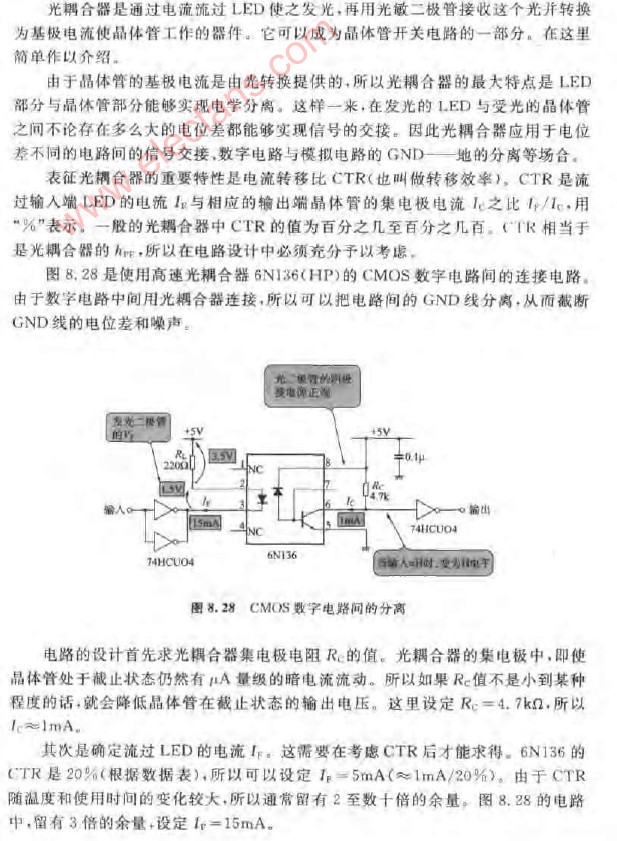

在看下面内容前,先温习一下NMOS和PMOS进入线性区和饱和区所需要的条件。这样,当你知道VGS,VDS时,可以对照着下图,看管子是处于饱和区还是线性区。

当管子处于线性区时,MOS管等效于一个电阻,而且当VGS进一步升高,管子进入深度线性区时,这个电阻值Ron很小。

现在正式开始。假设Vin要开始从0V变到VDD。

状态1:

(1) 假设Vin=0,

此时对于M1来说,VGS1=Vin

而对于M2来说,VGS=-VDD,VDS=0V,满足|VGS|>|VTH2|, |VDS|<|VGS|-|VTH|,所以M2处于线性区。

也就是说,M1关断,M2等效于一个很小的电阻,即M2处于打开状态。

此时,流过M1和M2的电流为0.

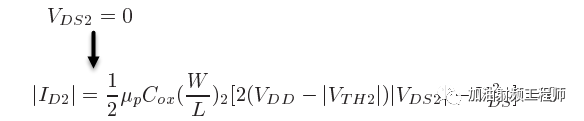

但是M2怎么能在电流I2=I1=0时,仍然处于打开的状态呢?

这只有当Vds2=0时,才可能成立。

即

因此,Vout=VDD。

(2) 当Vin升高时,|Vgs2|开始降低,同时它的Ron开始增加。

但是因为Vin

状态2:

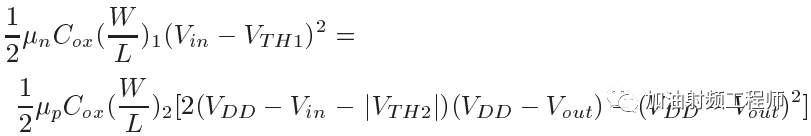

(3) 当Vin稍大于VTH1时,M1打开,M1和M2中开始有电流。因为Vout仍然接近于VDD,所以M1工作在饱和区,而M2处在线性区。

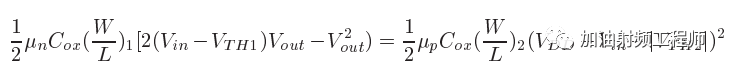

因为流过M1和M2的电流相等。

解上面这样一个方程,最后得到Vout随Vin变化的函数,显然是比较复杂的。

但是定性分析一下的话,发现当Vin升高时,Id和M2的沟道电阻都在增大,所以Vout必然继续下降。

状态3:

(4) Vout继续降低,降低到Vout=Vin+|VTH2|,M2即将退出线性区,进入饱和区。

此时M1的漏极电压为Vout,栅极电压为Vin,且Vout>Vin,所以Vgd=Vin-Vout<0

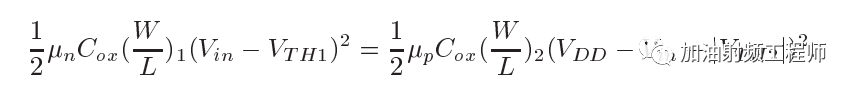

此时:

但是上述的等式中,没有Vout,所以没法根据这个式子推出Vout与Vin的关系。

但是,如果考虑上沟道长度调制效应,则:

当Vin继续下降一点点,使得Vin=Vout时,M1和M2都处于饱和区,称Vin=Vout时的输入电平为trip point,也称为反相器的switching threshold.

状态4:

(6) :Vin继续升高时,Vout继续下降,当Vin-Vout>VTH1时,M1进入线性区,M2仍然处于饱和区。

状态5:

(7) 当Vin继续上升,达到VDD-|VTH2|时,M2关断,M1处于线性区,此时M1类似于一个流过电流为0的电阻。

此时流过M1和M2的电流又变为0.

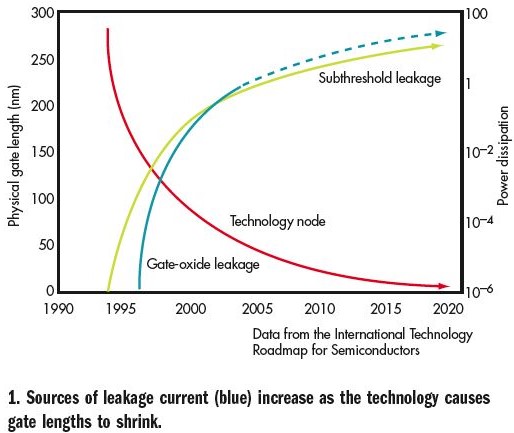

把这5个状态放到一幅图上时,如下。

所以,当反相器工作时,管子的状态并不是简单的关断和打开,而是经历了一系列的状态。

从上面的分析可知,只有在状态1和状态5时,流经管子的电流为0;但在中间态时,流经管子的电流均不为0.也就是说,静态时功耗为0,动态时有功耗。

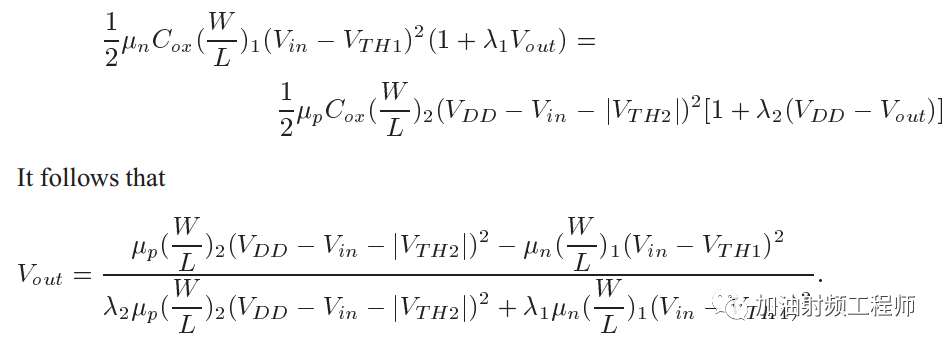

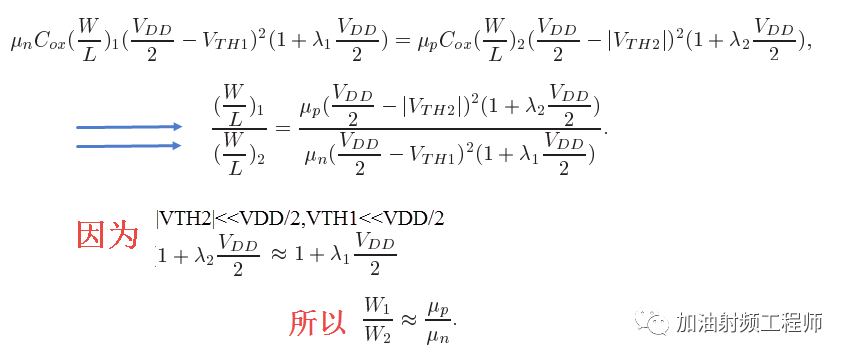

在设计CMOS反相器时,希望CMOS的转换电平(switching threshold)为VDD/2。

由上面的分析可知,当Vin=Vout时,转换点称为switching threshold,而此时M1和M2都处于饱和区。

所以,

因为 PMOS 迁移率约为 NMOS 迁移率的三分之一到二分之一,所以,M2 的宽度通常是 M1 的两倍到三倍。

-

CMOS

+关注

关注

58文章

5750浏览量

236266 -

反相器

+关注

关注

6文章

314浏览量

43549 -

数字电路

+关注

关注

193文章

1630浏览量

80888

原文标题:你知道为啥CMOS数字电路静态功耗小,动态功耗大么

文章出处:【微信号:加油射频工程师,微信公众号:加油射频工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

什么是数字电路

数字电路及其应用

数字电路的应用介绍

数字电路的主要优点

数字电路中的TTL和CMOS区别

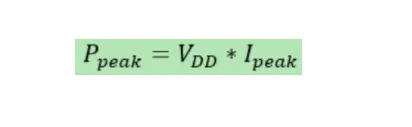

cmos动态功耗公式,cmos动态功耗和哪些电路参数有关

CMOS数字电路静态时动态功耗大的原因

CMOS数字电路静态时动态功耗大的原因

评论