信号完整性 (SI) 正成为 OpenVPX 系统设计人员越来越重要的考虑因素。虽然系统集成商首先面临一些 SI 问题,因为嵌入式行业将性能从 3.125 Gbaud 的第 1 代提升到 6.25 Gbaud 信令的 Gen2,但当前向第 3 代 》10 Gbaud 信令速率的过渡,几乎是第 2 代 OpenVPX 带宽的两倍,需要显著提高工具、能力、专业知识和专有技术水平,以确保成功设计和实施强大的最新一代, OpenVPX系统。

MultiGig VPX 连接器最初设计用于 6.25 Gbaud 信号速率。随着 Gen3 OpenVPX 信令增加到 》10 Gbaud 信令速率,我们正在将 MultiGig 连接器推向其物理极限。除非系统设计人员熟悉 SI 在实现这些新的更快信令速率时所扮演的更重要的角色,否则他们将新的 Gen3 OpenVPX 设计的成功置于危险之中。

第 3 代 》10 Gbaud 信令的仿真研究

为了加强当前对Gen3 OpenVPX SI的研究,备受推崇的第三方信号完整性专家Teraspeed咨询集团进行了广泛的仿真研究。仿真旨在分析MultiGig连接器的物理极限,并在各种背板长度上执行完整的端到端建模,并确保系统级的稳健性能。

测试 VPX 连接器的限制

MultiGig连接器在较高OpenVPX信令速率下操作的物理限制已经认识和理解了一段时间。事实上,VPX 连接器的内部设计可能导致几个众所周知的 SI 损伤。必须积极管理这些损伤,再加上与 VPX 连接器占用空间的物理几何形状相关的问题,以确保可靠的 Gen3 10 Gbaud 操作。这些与连接器相关的损伤包括:

• 由于 VPX 连接器封装中的阻抗不连续而导致的回波损耗 (RL);

• 由于 VPX 连接器封装的物理几何形状而导致的串扰;

• 由于差分对中的编织偏斜导致共模信号(模式转换),夸大了已经很高的串扰;以及

• 过孔和连接器中的谐振会降低 10 Gbaud 下临界 5 GHz 奈奎斯特区域的插入损耗 (IL)、RL 和串扰

仿真测试结果

仿真测试表明,MultiGig连接器过孔中的RL和串扰峰值发生在奈奎斯特附近的4至5 GHz频段,而插入损耗也会降低(参见图1中插入损耗的下降)。这挤压了临界奈奎斯特区域的信噪比。下面的图 1 说明了这种现象。

图 2(左图)显示了由最坏情况排列产生的 40 Gb 以太网 (GbE) 眼图。虽然使用良好的高速设计规则通常足以实现可靠的 10 Gbaud 操作,但这些结果表明,该方法对于 VPX 连接器是不够的。

作为仿真和建模工作的结果,Curtiss-Wright开发了一套新的高速设计规则。图 2(右图)显示了使用新开发的设计规则进行最坏情况排列产生的 40 GbE 眼图。这表明,通过避免最坏情况的排列,可以实现支持 》10 Gbaud 信令的鲁棒通道。

研究表明,以 》10 Gbaud 的 Gen3 信令速率实现强大的 OpenVPX 解决方案是一项艰巨的任务。在我们的研究过程中,运行了超过11,000个模拟案例。这项研究的结果表明,这些参数的排列中有很大一部分,由于制造公差变化而进一步加剧,产生的通道在10 Gbaud下无法可靠工作。(见图3)。

虽然人们可能会认为选择低损耗层压材料有助于减轻这些故障,但事实证明,这个问题非常复杂,无法用这种方法解决。需要对模块和背板应用激进的设计规则,以避免问题排列。

SI 建模结果

SI 建模的结果提供了非常有用的数据,有助于定义设计具有第 3 代信令速率的 OpenVPX 系统的最佳实践规则。为了缓解与 VPX 连接器相关的 SI 损伤问题,需要优化几个设计参数:

• 模块和背板走线长度优化;

• 模块和背板材料选择;

• 模块和背板编织歪斜缓解;

• 模块和背板堆叠优化;

• 模块和背板通过调谐;

• 控制模块和背板制造公差变化;

• 模块交流电容电路优化;以及

• 模块设备封装分线优化。

虽然仿真和建模表明,在OpenVPX系统中可以实现强大的Gen3 》10 Gbaud信令,但它也清楚地表明,成功的设计需要高度的谨慎和专业知识。必须优化模块和背板的设计,以实现强大的Gen3 》10 Gbaud信号。

审核编辑:郭婷

-

以太网

+关注

关注

41文章

6197浏览量

181573 -

连接器

+关注

关注

105文章

16390浏览量

147904

发布评论请先 登录

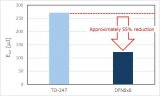

ROHM推出全新第5代SiC MOSFET产品

ROHM开发出新一代EcoSiC™“第5代SiC MOSFET”

维信诺以底层创新驱动OLED持续进化

【中奖通知】地奇星征集令留言有礼获奖公布!!!

TUSB8044A四端口USB 3.2第1代集线器:特性、应用与设计要点

工信部许可两款L3级自动驾驶车型产品,L3时代真的来了吗?

瞻芯电子第3代1200V 35mΩ SiC MOSFET量产交付应用

IPEX第1代与第4代的主要差异

什么是零代码平台?

东芝推出新型650V第3代SiC MOSFET

支持500 +量子比特!国产第4代量子计算测控系统发布

支持500 +量子比特!国产第4代量子计算测控系统发布

QDAT非信令测试介绍

设计OpenVPX系统以支持第3代Gbaud信令

设计OpenVPX系统以支持第3代Gbaud信令

评论