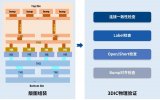

1. 数字IC设计流程相关名词梳理

半定制设计(ASIC):

工艺厂商已经把逻辑门设计好了,只需要搭建自己的电路,不用管逻辑门里面的晶体管。

RTL ( Register Transfer Level)设计:

利用硬件描述语言,如verilog对电路以寄存器之间的传输为基础进行描述;寄存器传输是时序电路,时钟沿到来的时候才变化,寄存器可以统一受时钟控制。

功能验证:

在功能上确保每一步设计与实现的流程转换时,能够保证它的逻辑不要变形,在ASIC设计与实现各个阶段都对应有不同的验证手段和工作。

逻辑综合:

将RTL级设计中所得的程序代码翻译成实际电路的各种元器件以及他们之间的连接关系,可以用一张表来表示,称为门级网表( Netlist ),门级网表也是一个标准的Verilog语言,他描述的层次比RTL层级更低。

门级网表:标准单元的门+连线。图纸是半定制,不用细节到晶体管,只用到门和连线即可;

所需内容:库文件,RTL代码,时序等约束文件(.sdc),综合的脚本(即命令,可以提前写好);

生成内容:门级网表(还是代码 .gv gate verilog),SDC。

形式验证:

主要是检查网表和和RTL是否等价,不需要激励,是静态仿真:通过数学模型的方法看是否满足。做等价性检查用到Synopsys的Formality工具。

STA ( Static Timing Analysis,静态时序分析) :

套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint);静态时序分析:通过数学的方法,来计算所有的路径,有没有满足时序。

对布图前后的门级网表进行STA:在布图前,PrimeTime使用由库指定的线载模型估计线网延时。如果所有关键路径的时序是可以接受的,则由PrimeTime或DC得到一个约束文件,目的是为了预标注到布图工具。在布图后,实际提取的延迟被反标注到PrimeTime以提供真实的延迟计算

时钟树综合CTS(Clock Tree Synthesis):

简单点说就是时钟的布线。由于时钟信号在数字芯片的全局指挥作用,它的分布应该是对称式的连到各个寄存器单元,从而使时钟从同一个时钟源到达各个寄存器时,时钟延迟差异最小。这也是为什么时钟信号需要单独布线的原因。CTS工具,Synopsys的Physical Compiler

布局布线:

布局规划:就是放置芯片的宏单元模块,在总体上确定各种功能电路的摆放位置,如IP模块,RAM,I/O引脚等等。布局规划能直接影响芯片最终的面积。

布线(CTS之后)就是普通信号布线了,包括各种标准单元(基本逻辑门电路)之间的走线。比如我们平常听到的0.13um工艺,或者说90nm工艺,实际上就是这里金属布线可以达到的最小宽度,从微观上看就是MOS管的沟道长度。工具Synopsys的Astro,或者Synopsys的IC Compiler (ICC)(ICC是Astro的下一代取代产品)

Extrat RC和STA:

前面逻辑综合后STA的话,用的是一个理想的时序模型(Timing Model)去做的,这个实际上并没有实际的时序信息,实际cell摆在哪里,两个cell之间的走线延时等信息都是没有的,因为这个时候还没有布局布线,两个的位置都是不确定的,自然没有这些信息。当位置确定之后,才会真正的去提取这些延时信息(Extrat RC),然后再做布局布线之后的STA,此时的STA相较于综合时的STA,拿到的延时信息就是更真实的!包括时钟,也是插了时钟树之后真正的时钟走线,时钟路径的延时也是更真实的。如果布局布线之后还有不满足时序的地方,也会退回去前面的阶段进行修改。

版图物理验证:

对完成布线的物理版图进行功能和时序上的验证,验证项目很多,如:

LVS(Layout Vs Schematic)验证:简单说,就是版图与逻辑综合后的门级电路图的对比验证;

DRC(Design Rule Checking):设计规则检查,检查连线间距,连线宽度等是否满足工艺要求;

ERC(Electrical Rule Checking):电气规则检查,检查短路和开路等电气 规则违例;等等。

工具为Synopsys的Hercules。

实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的DFM(可制造性设计)问题。物理版图验证完成也就是整个芯片设计阶段完成,下面的就是芯片制造了。

GDSII文件:

物理版图以GDSII的文件格式交给芯片代工厂(称为Foundry)在晶圆硅片上做出实际的电路,再进行封装和测试,就得到了实际的芯片。

2. IC设计过程中用到的EDA工具总结

审核编辑 :李倩

-

IC设计

+关注

关注

38文章

1406浏览量

108440 -

eda

+关注

关注

72文章

3148浏览量

183847 -

晶体管

+关注

关注

78文章

10443浏览量

148705

原文标题:数字IC设计流程相关名词梳理及各流程EDA工具总结

文章出处:【微信号:feifeijiehaha,微信公众号:电路和微电子考研】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

英诺达荣登2026中国IC设计Fabless100榜单TOP10 EDA公司

概伦电子荣获2026中国IC设计成就奖之年度产业贡献EDA公司

西门子EDA亮相Semicon China 2026

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】跟着本书来看EDA的奥秘和EDA发展

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】+ 全书概览

【「芯片设计基石——EDA产业全景与未来展望」阅读体验】--EDA了解与发展概况

70%营收砸向研发!这家EDA企业破局高密度存储EDA、数字EDA

【书籍评测活动NO.69】解码中国”芯“基石,洞见EDA突围路《芯片设计基石——EDA产业全景与未来展望》

AI重塑EDA,3D-IC成关键战场:Cadence的洞察与应变

华大九天物理验证EDA工具Empyrean Argus助力芯片设计

西门子推出用于EDA设计流程的AI增强型工具集

EDA是什么,有哪些方面

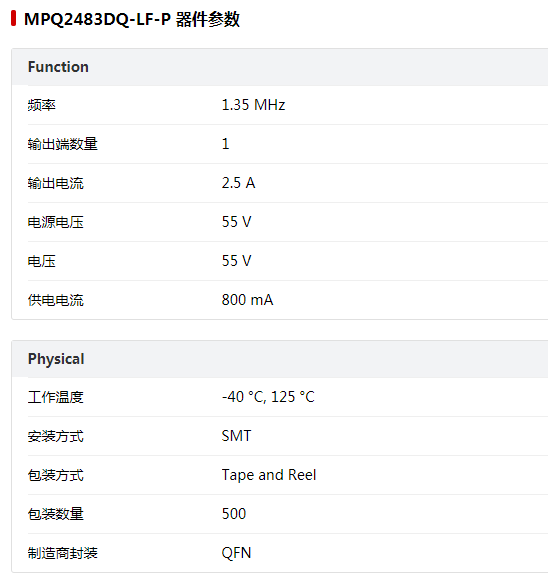

Monolithic Power Systems (MPS)MPQ2483DQ-LF-P PWM LED驱动IC的参数特性 EDA模型和数据手册分享

产学研融合!思尔芯数字EDA工具走进北航课堂

数字IC设计+EDA流程及专有名词

数字IC设计+EDA流程及专有名词

评论