最近一个项目开始使用Xilinx的ZU+系列MPSoC,于是对其官网上的相关文档进行了学习梳理,包括电源、时钟、复位、配置和外围接口等。

本篇就电源部分进行梳理,其他部分会在后续的文章进行梳理,如有不妥之处,敬请留言指正为谢!

1、电源概述

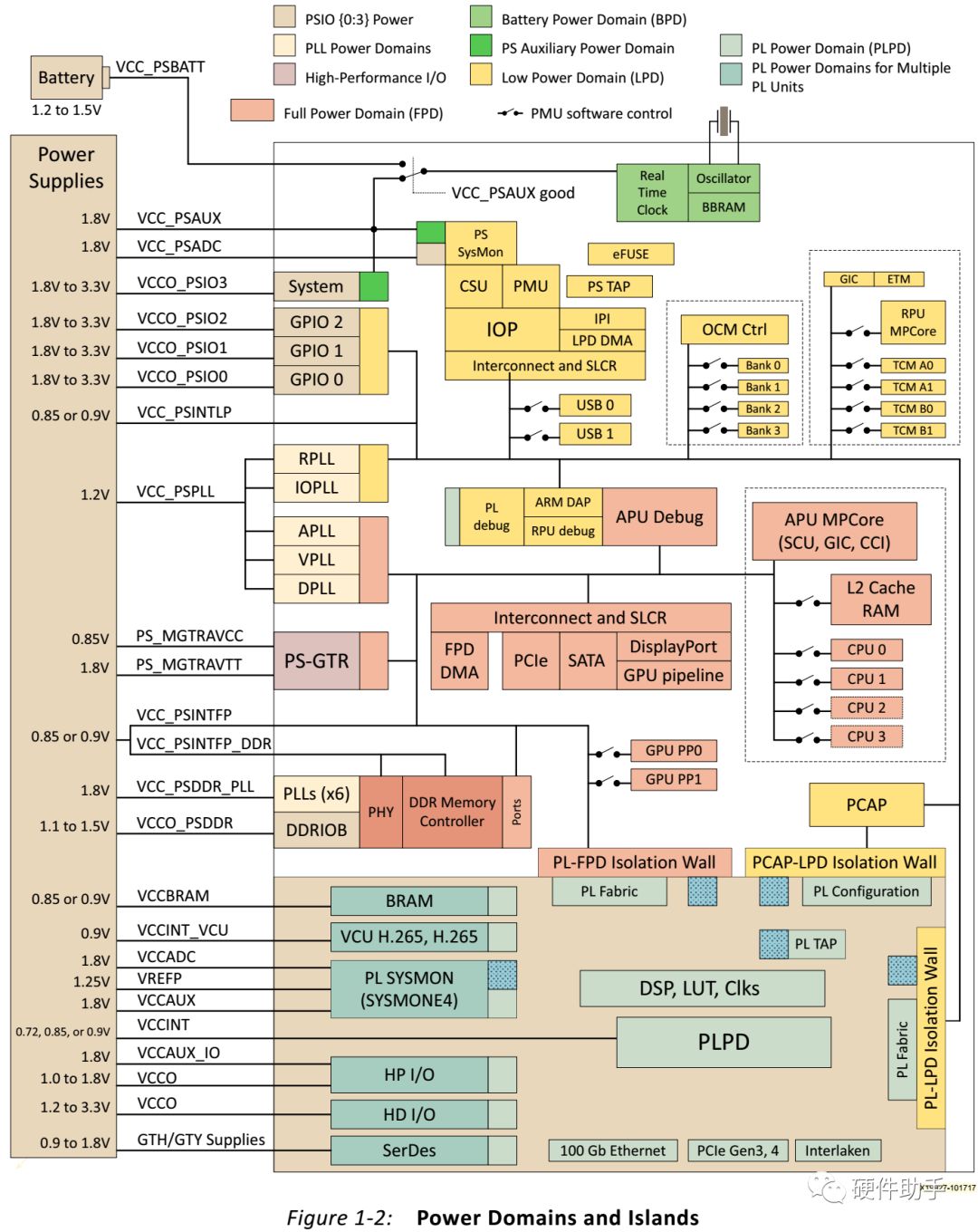

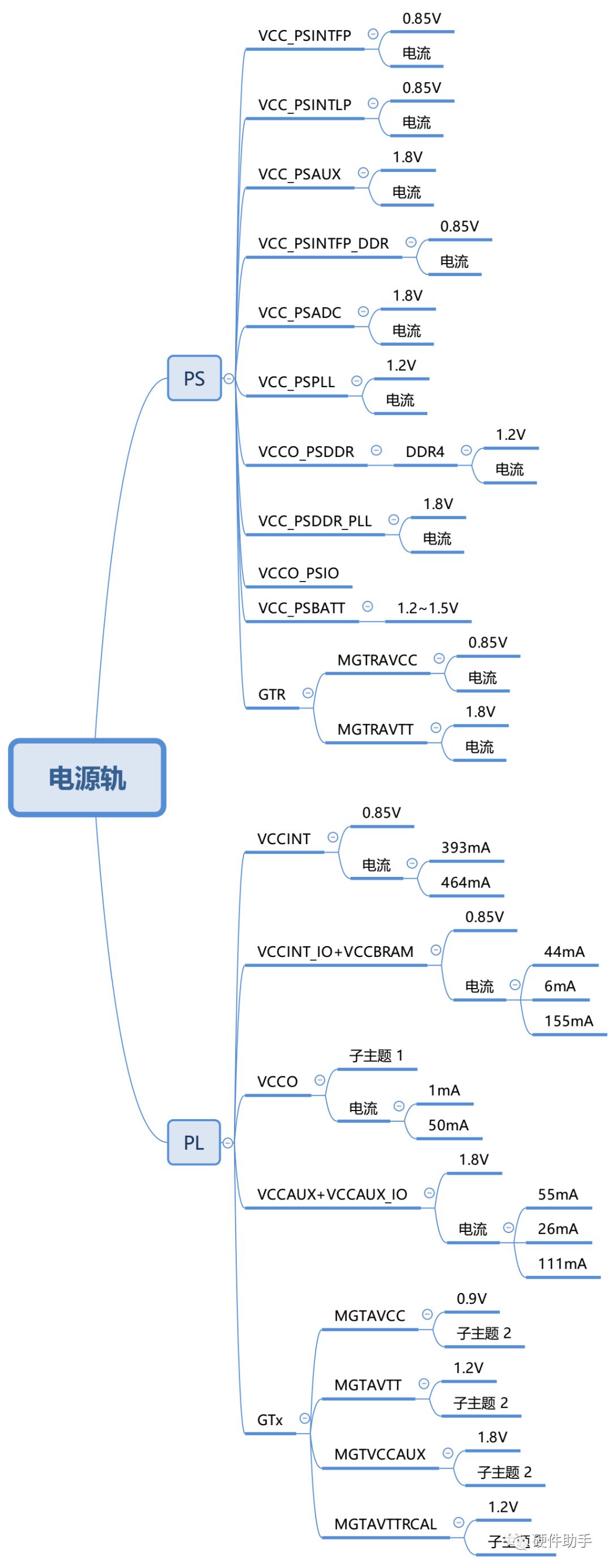

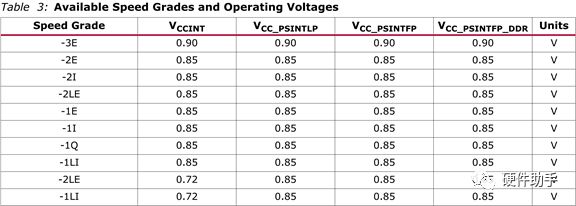

引用UG1085中的一张图可以看出ZU+的电源还是相当复杂的,不过细细琢磨也就分为两部分:PL和PS,PL部分再细分为logic部分和GTx部分;PS部分再细分为LPD、FPD(含GTR)和公共部分(PLL、ADC、AUX)。下面是用思维导图整理的相关电源域,其中以-2E等级为参考,电流部分由于所选型号、所用资源不一,暂未统一评估,后续会进行详细评估。

电源相关引脚描述可参考UG1085和DS925。

2、上电时序

上面简单的概述了一下ZU+的电源域,下面就上电时序进行叙述。

PS部分和PL部分的上电时序是独立的,为了防止损坏器件,器件内部已经进行了隔离。

PS部分的LPD(Contains the ARM Cortex-R5 real-time processor unit (RPU), theplatform management unit (PMU), and the configuration security unit (CSU), aswell as the remaining on-chip peripherals.)要先于FPD(Contains the ARM Cortex-A53application processor unit (APU) as well as a number of peripherals typicallyused by the APU.)上电,或者同时上电。

LPD部分的上电顺序为:

VCC_PSINTLP

CVCC_PSAUX, VCC_PSADC, andVCC_PSPLL in any order or simultaneously.

CVCCO_PSIO

FPD部分的上电顺序为:

VCC_PSINTFP andVCC_PSINTFP_DDR driven from the same supply source.

VPS_MGTRAVCC andVCC_PSDDR_PLL in any order or simultaneously.

VPS_MGTRAVTT andVCCO_PSDDR in any order or simultaneously.

PL的逻辑部分的推荐上电时序为VCCINT,VCCINT_IO/VCCBRAM, VCCINT_VCU, VCCAUX/VCCAUX_IO, and VCCO. VCCINT_IO和VCCBRAM必须连接到一起,VCCAUX/VCCAUX_IO必须连接到一起。如果VCCINT和VCCINT_IO/VCCBRAM电压相同,可以使用同一电源并且同时上电;如果VCCAUX/VCCAUX_IO和VCCO电压相同,可以使用同一电源并且同时上电。

PL的GTx部分的推荐上电时序为VCCINT, VMGTAVCC, VMGTAVTT OR VMGTAVCC, VCCINT,VMGTAVTT. VMGTVCCAUX没有时序要求。

VMGTAVCC和VCCINT没有时序要求,可以同时上电。如果不满足时序要求,则VMGTAVTT上下电的电流可能比规范规定的高。

所有的下电时序都和上电时序相反。一般都不进行下电时序控制,如果有需要低成本的下电时序控制电路,可以参考NVIDIA的Jetson TX2的底板,本人之前就使用过这套方案进行过K7的下电时序控制,还是非常好用的,这套方案成本较低,同时考虑了外部掉电和主动关机的情况,值得参考。

上下电时序相关资料可参考DS925。

3、电流评估

Xilinx FPGA的电流评估常见的有几种方案:Xilinx自己的XPE(使用该种方式你一定会惊叹excel的强大之处!)、TI的WEBENCH(貌似只有FPGA部分,没有ARM部分)、Vivado软件、开发板等,这几种方案都可以根据自己的外设进行定制,方便灵活。

以下为XPE评估的一个样例:

PS部分的电流评估:

| Domain | Source | Voltage | Total (A) | Total |

| Battery Power | VCC_PSBATT | 1.200 | <0.001 | <0.001W |

| Low Power (Logic + IO) | VCC_PSINTLP | 0.850 | 0.380 | 0.323W |

| VCCO_PSIO0_500 | 3.300 | 0.008 | 0.026W | |

| VCCO_PSIO1_501 | 3.300 | 0.005 | 0.017W | |

| VCCO_PSIO2_502 | 3.300 | 0.002 | 0.007W | |

| VCCO_PSIO3_503 | 3.300 | 0.001 | 0.002W | |

| LPD Power | 0.375W | |||

| Full Power (Logic + IO) | VCC_PSINTFP | 0.850 | 0.867 | 0.737W |

| VCCO_PSDDR_504 | 1.200 | 1.107 | 1.329W | |

| VPS_MGTRAVCC | 0.850 | 0.284 | 0.241W | |

| VPS_MGTRAVTT | 1.800 | 0.042 | 0.076W | |

| VCC_PSINTFP_DDR | 0.850 | 1.228 | 1.044W | |

| FPD Power | 3.427W | |||

| Others | VCC_PSPLL | 1.200 | 0.078 | 0.094W |

| VCC_PSDDR_PLL | 1.800 | 0.013 | 0.023W | |

| VCC_PSADC | 1.800 | 0.011 | 0.019W | |

| VCC_PSAUX | 1.800 | 0.002 | 0.004W | |

| Others Power | 0.140W |

PL部分的电流评估:

| Power Supply | ||

| Source | Voltage | Total (A) |

| VCCINT | 0.850 | 3.819 |

| VCCINT_IO | 0.850 | 0.234 |

| VCCBRAM | 0.850 | 0.057 |

| VCCAUX | 1.800 | 0.178 |

| VCCAUX_IO | 1.800 | 0.176 |

| VCCO3.3V | 3.300 | 0.000 |

| VCCO2.5V | 2.500 | 0.000 |

| VCCO1.8V | 1.800 | 0.033 |

| VCCO1.5V | 1.500 | 0.000 |

| VCCO1.35V | 1.350 | 0.000 |

| VCCO1.2V | 1.200 | 0.326 |

| Vcco 1.0V | 1.000 | 0.000 |

| VCCADC | 1.800 | 0.008 |

注:我使用的是XCZU3,没有引出GTx部分。

同样可以使用TI的WEBENCH进行评估,也可以使用vivado进行预评估。

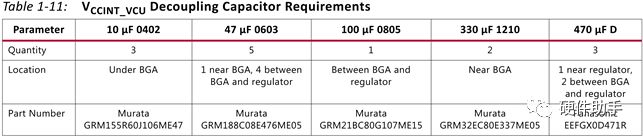

4、电源相关设计(主要是去耦电容)

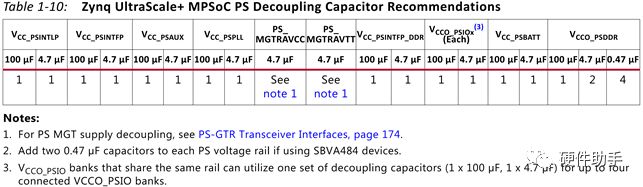

PL部分电源的去耦电容根据型号不同、封装不同,具体的数量不同,具体参见UG583,也可以根据XTP427的checklist进行对照检查。

PL部分电源域主要包括:VCCINT/VCCINT_IO,VCCBRAM/VCCINT_IO,VCCAUX/VCCAUX_IO,HDIO,HPIO几组。

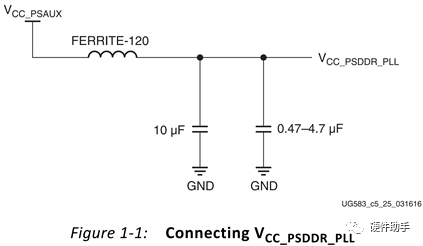

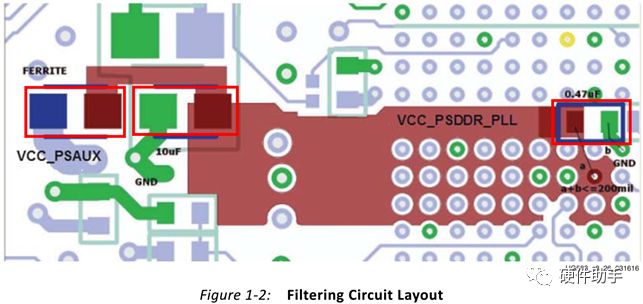

PS部分电源域较多,具体参见UG583,也可以根据XTP427的checklist进行对照检查。针对VCC_PSDDR_PLL和VCCINT_VCU(MPSoCEV Devices Only)还需要特殊处理。

5、电源解决方案

5.1、Xilinx推荐的解决方案

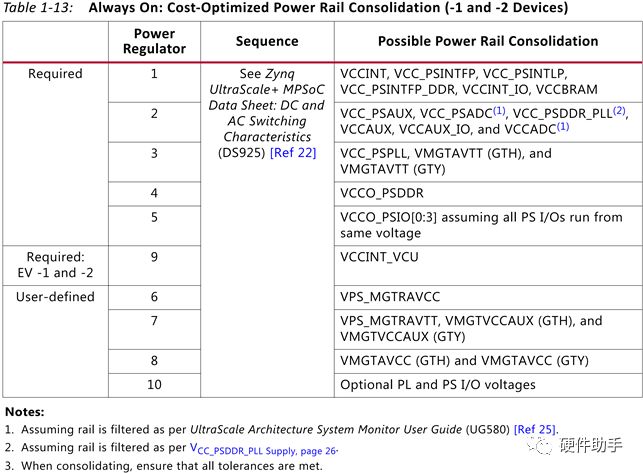

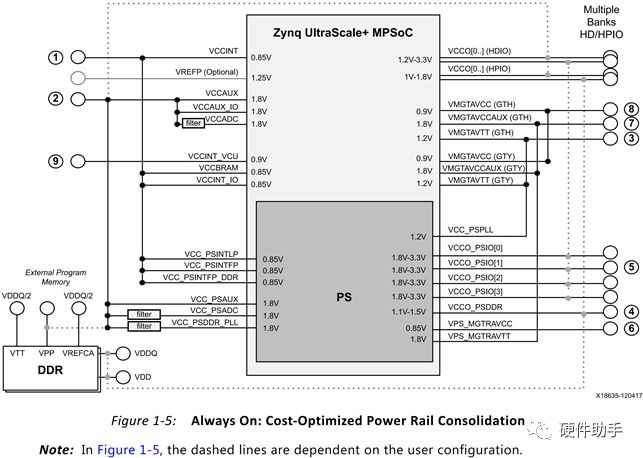

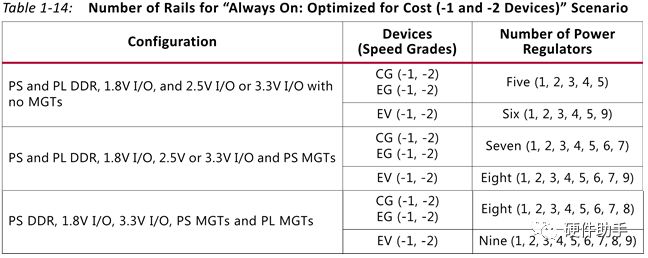

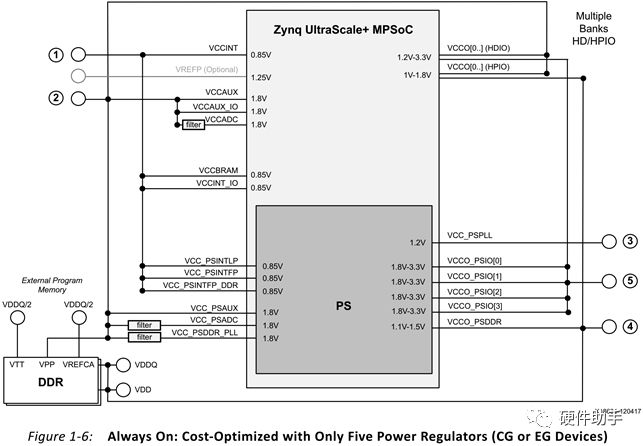

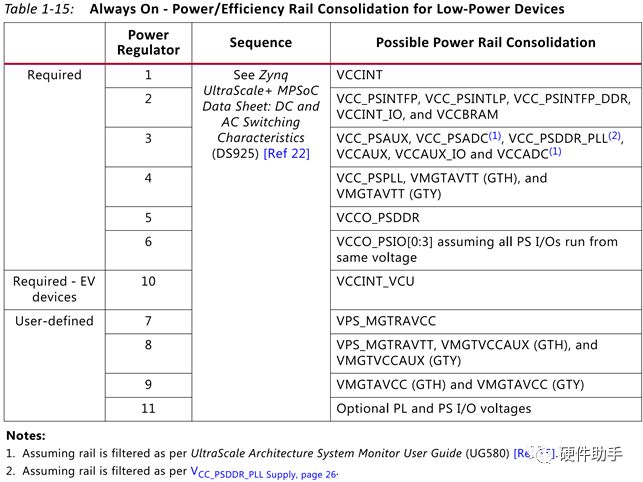

在了解市面上常见解决方案之前,先看看Xilinx官方提供的电源解决方案,在UG583中Xilinx提供了四种解决方案:

Always on: Cost optimized (-1 and -2 devices)

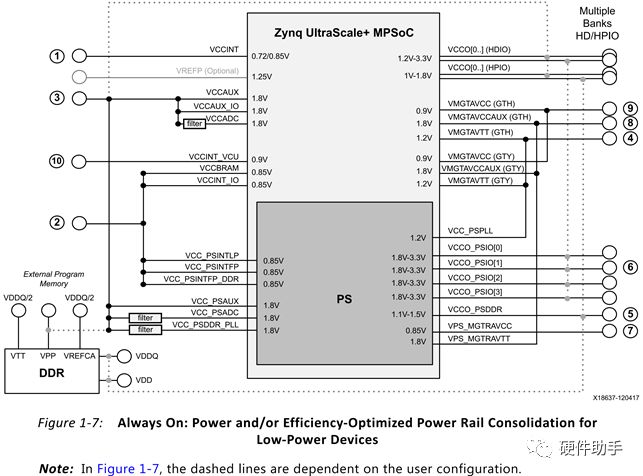

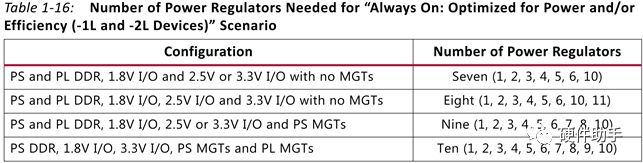

Always on: Power/efficiency optimized (-1L and -2L devices)

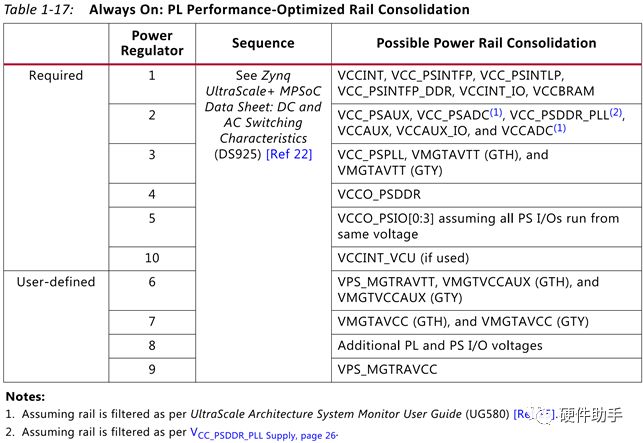

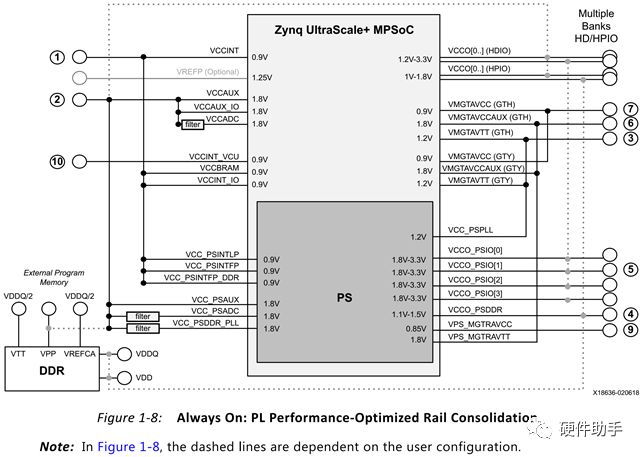

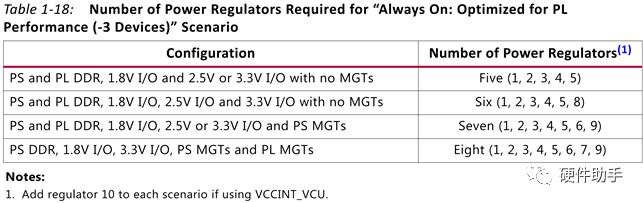

Always on: PL performance optimized (-3 devices)

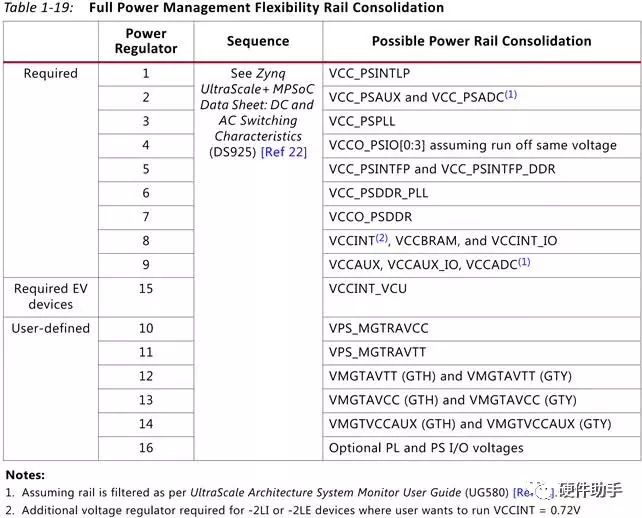

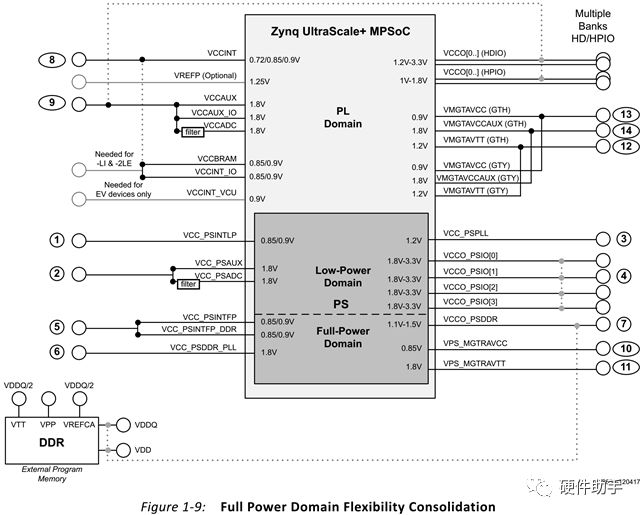

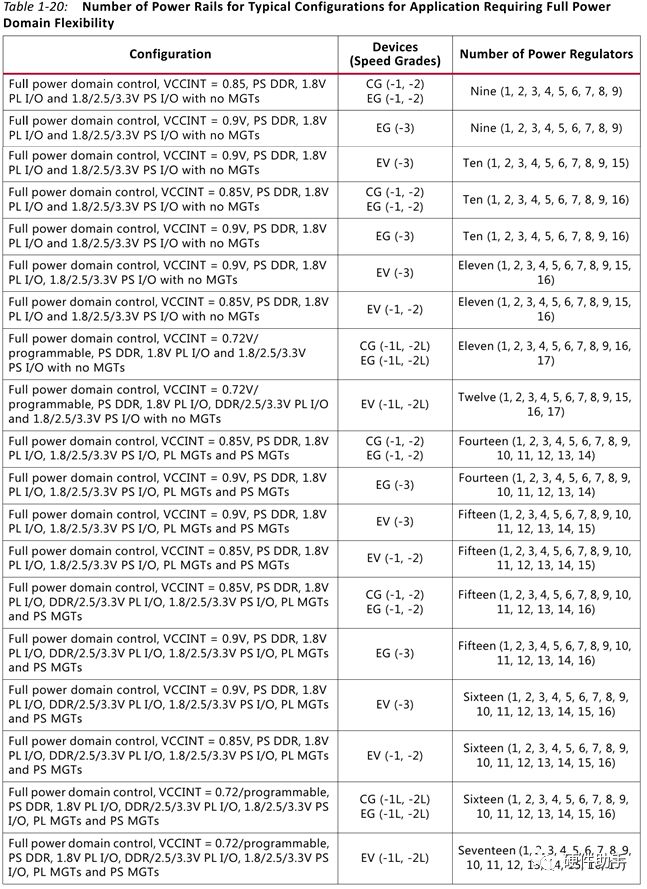

Full power management flexibility (all devices/speed grades)

并针对每一种提出了相应的解决方案,详细见后。

-----------------Always on: Cost optimized (-1 and -2 devices)--------------------------

-----------Always on: Power/efficiency optimized (-1L and -2L devices)------------

-------------------Always on: PL performance optimized (-3 devices)------------------

-------------Full power management flexibility (all devices/speed grades)--------

5.2、电源厂家的解决方案

市面上ZU+的电源解决方案较多,常见的电源芯片厂家均有,出去单路输出的解决方案外,如TI、ADI(linear)、dialog、Infineon等厂家均有相应的PMIC解决方案,比较常见的ZU+的电源解决方案主要有以下几种:

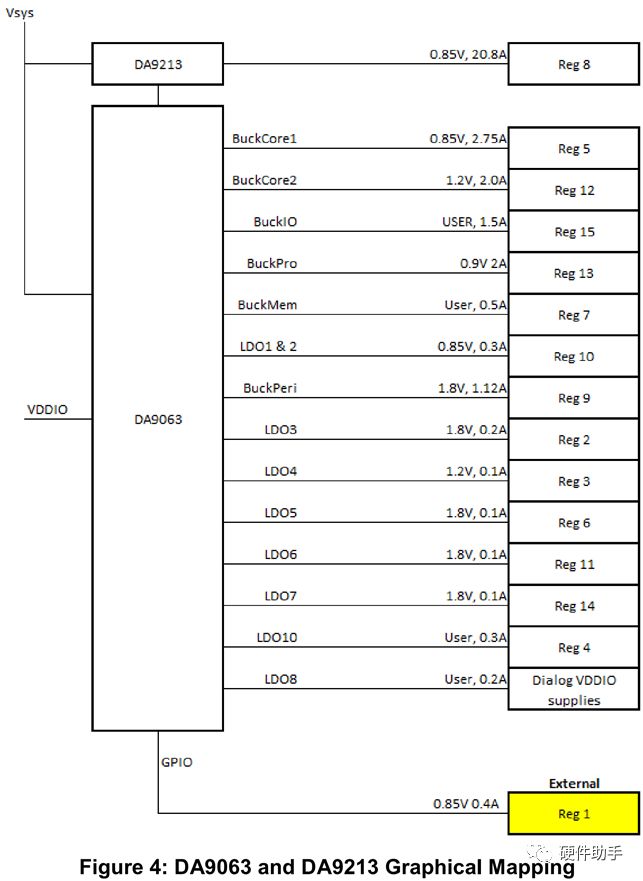

Dialog公司的DA9063

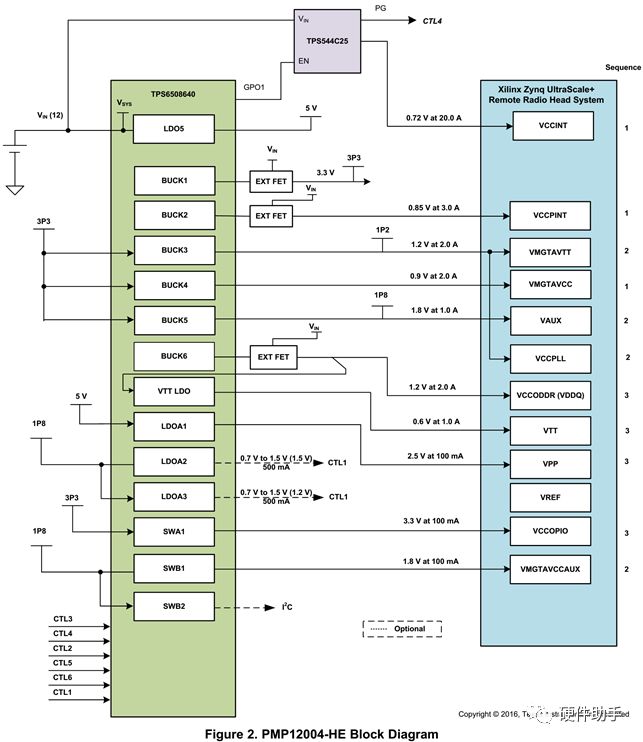

TI的TPS6508640,PMP10555、PMP11328(只有core rail)、TIDA-01480、PMP12004-HE等

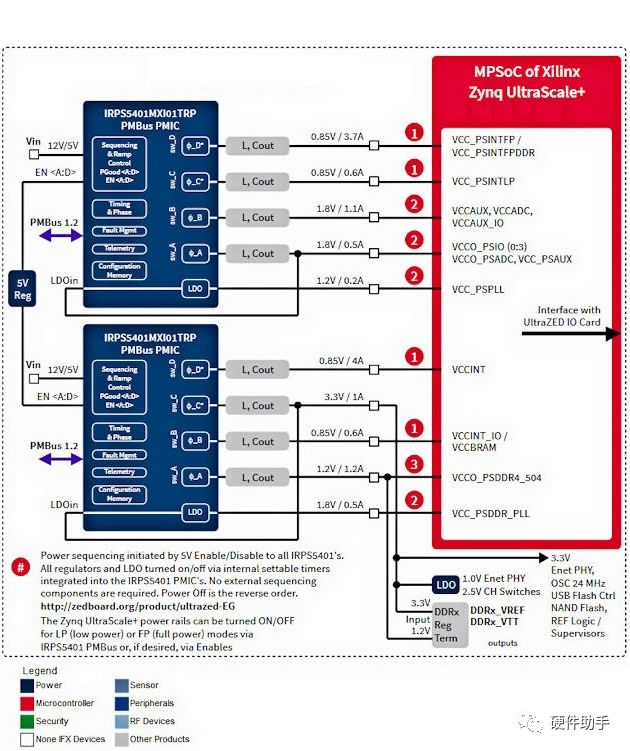

Infineon的IRPS5401

----------------------------Dialog公司的DA9063和DA9213解决方案---------------------

----------------------------------TI的TPS6508640解决方案-----------------------------------

-------------------------------------Infineon的IRPS5401---------------------------------------

由于不同的使用情况,功耗差异较大,具体方案的选择,需根据使用的资源、封装选型等因素考虑,切记照抄照搬!

-

电源

+关注

关注

184文章

17769浏览量

250749 -

接口

+关注

关注

33文章

8643浏览量

151387 -

Xilinx

+关注

关注

71文章

2168浏览量

121672 -

时序

+关注

关注

5文章

389浏览量

37356

原文标题:Zynq UltraScale+系列之“电源”

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Ti推出面向Zynq UltraScale+ MPSoC的电源参考设计

Xilinx Zynq UltraScale MPSoC可扩展电源设计

开源硬件-TIDA-01480.11-适用于 Xilinx Zynq® UltraScale+™ ZU2CG−ZU5EV MPSoC 的集成电源 PCB layout 设计

开源硬件-TIDA-01480.03-适用于 Xilinx Zynq® UltraScale+™ ZU2CG−ZU5EV MPSoC 的集成电源 PCB layout 设计

开源硬件-TIDA-01480.12-适用于 Xilinx Zynq® UltraScale+™ ZU2CG−ZU5EV MPSoC 的集成电源 PCB layout 设计

开源硬件-TIDA-01480.01-适用于 Xilinx Zynq® UltraScale+™ ZU2CG−ZU5EV MPSoC 的集成电源 PCB layout 设计

开源硬件-TIDA-01480.06-适用于 Xilinx Zynq® UltraScale+™ ZU2CG−ZU5EV MPSoC 的集成电源 PCB layout 设计

开源硬件-TIDA-01480.16-适用于 Xilinx Zynq® UltraScale+™ ZU2CG−ZU5EV MPSoC 的集成电源 PCB layout 设计

开源硬件-TIDA-01480.05-适用于 Xilinx Zynq® UltraScale+™ ZU2CG−ZU5EV MPSoC 的集成电源 PCB layout 设计

开源硬件-TIDA-01480.08-适用于 Xilinx Zynq® UltraScale+™ ZU2CG−ZU5EV MPSoC 的集成电源 PCB layout 设计

开源硬件-TIDA-01480.09-适用于 Xilinx Zynq® UltraScale+™ ZU2CG−ZU5EV MPSoC 的集成电源 PCB layout 设计

开源硬件-TIDA-01480.02-适用于 Xilinx Zynq® UltraScale+™ ZU2CG−ZU5EV MPSoC 的集成电源 PCB layout 设计

【Zynq UltraScale+ MPSoC解密学习2】Zynq UltraScale+的电源系统

Zynq UltraScale+ZU+的电源域

Zynq UltraScale+ZU+的电源域

评论