3.3 CXL.mem

3.3.1 介绍

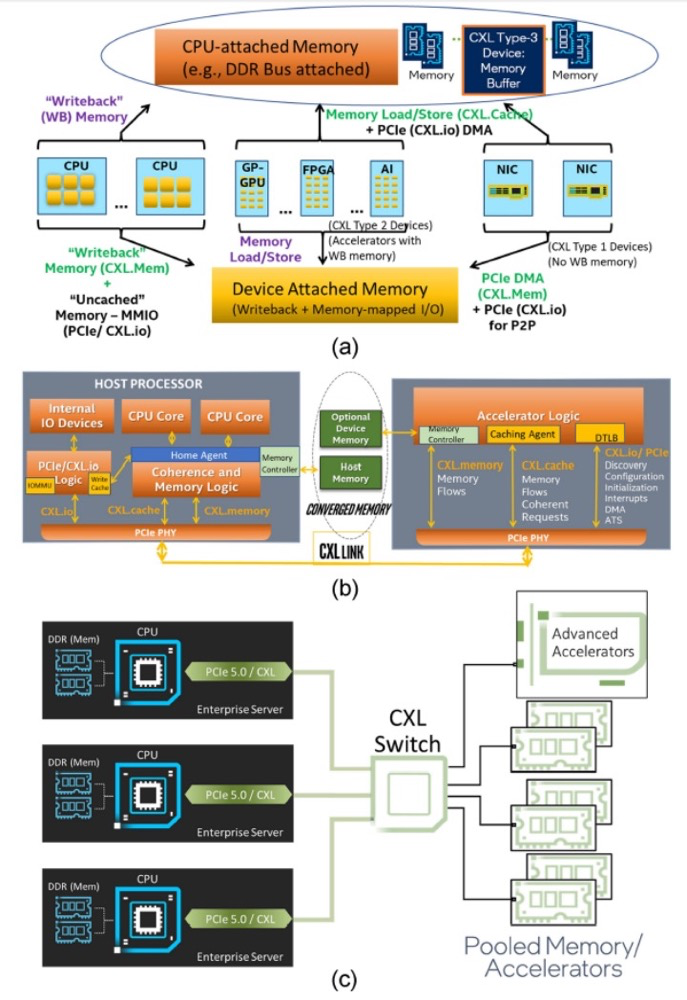

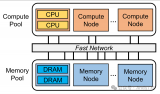

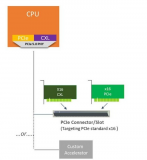

CXL内存协议被称作CXL.mem。CXL.mem定义了CPU和内存之间的传输接口。该协议可用于多个不同的内存连接选项,包括当内存控制器位于主机CPU中时,或当内存控制器位于加速器设备内时,或当内存控制器移动到内存缓冲芯片时。

CPU中的一致性引擎使用CXL.mem请求和响应与内存接口。在此配置中,CPU一致性引擎被视为CXL.mem主设备(Master),内存设备被视为CXL.mem从设备(Subordinate)。主设备负责向从设备发起读写请求,从设备负责响应主设备的读写请求。

当从设备是一个加速器时,CXL.mem协议认为设备内部也有一个一致性引擎(Device Coherency Engine,简称DCOH)。

从Master到Subordinate的CXL.mem事务被称作M2S;反过来,从Subordinate到Master的事务称作S2M。

M2S事务只有两种消息类型:

无数据的请求(Req)

有数据的请求(RwD)

对应的,S2M事务也只有两种类型:

无数据的响应(NDR)

有数据的响应(DRS)

3.3.2 内存QoS遥测

内存QoS遥测是内存设备的一种机制,用于在CXL.mem请求的每个响应消息中指示其当前负载级别(DevLoad)。这使主机能够根据负载级别来衡量对部分设备、单个设备或设备组的CXL.mem请求的速率,从而优化这些内存设备的性能,同时限制结构拥塞。

插播一句,QoS是Quality of Service的缩写,翻译过来就是服务质量。对于内存系统而言,带宽和延时受到一定的限制,如何向其它的模块提供服务是一个系统问题。SoC有的模块可能带宽需求不大,但是对于延时要求很高,比如显示模块。而有的模块对于带宽要求很大,但是延时可以略高,比如数据处理器。如果对SoC所有模块的内存需求一视同仁,可能影响整个系统的运行。利用QoS机制,可以对每个模块的内存访问排列顺序,达到内存系统的最佳利用。

内存QoS遥测内容比较绕,我也没看太懂,暂时略过,不影响CXL的学习。

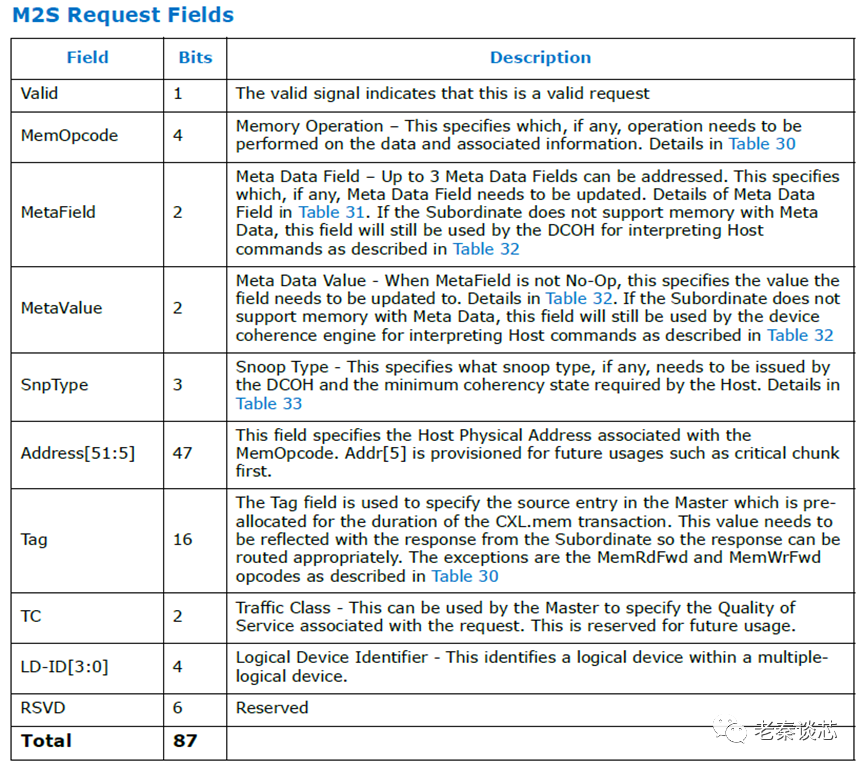

3.3.3 M2S请求(Req)

Req消息是无数据请求,消息字段定义如下:

各字段的编码和详细解释就不贴图了,如果有需要,大家可以去协议里面查找。

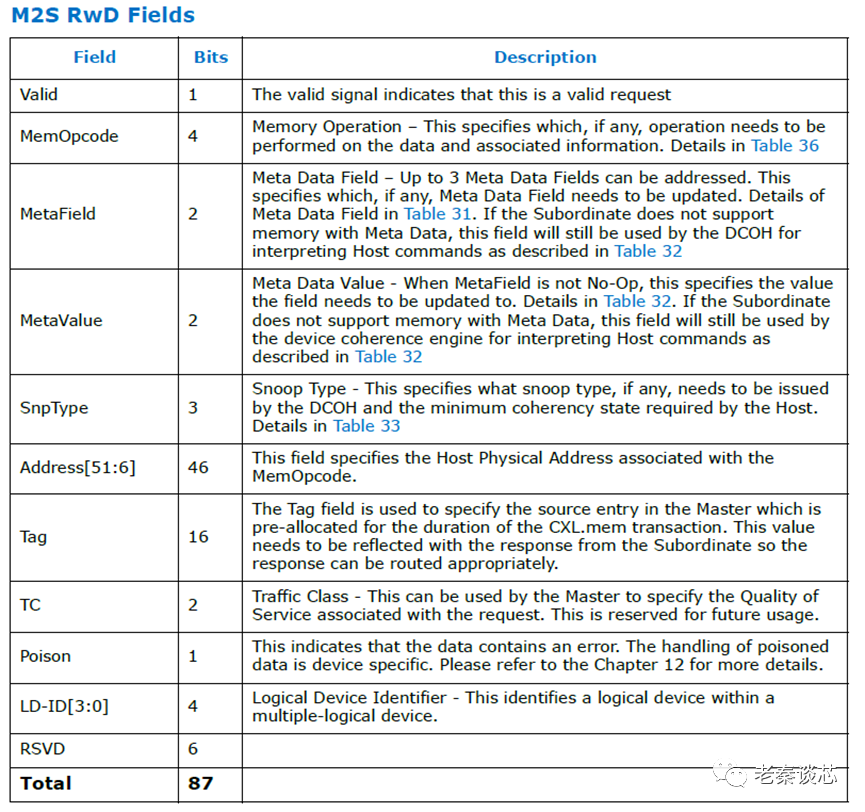

3.3.4 M2S带数据请求(RwD)

RwD是有数据请求,消息字段定义如下:

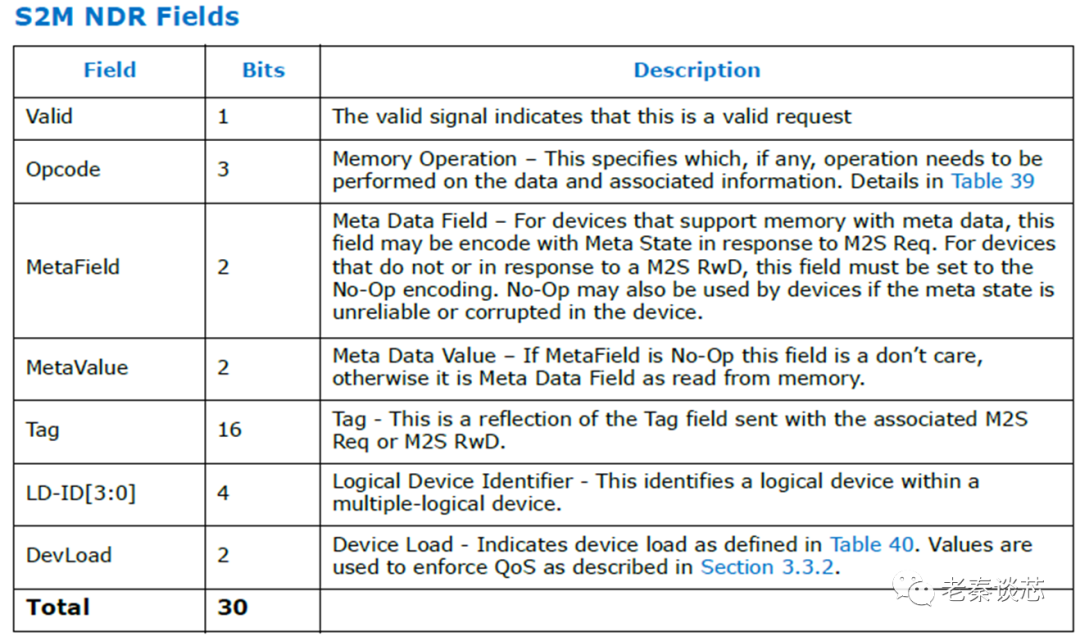

3.3.5 S2M无数据响应(NDR)

NDR消息类包含从Subordinate到Master的完成和指示,不带数据。

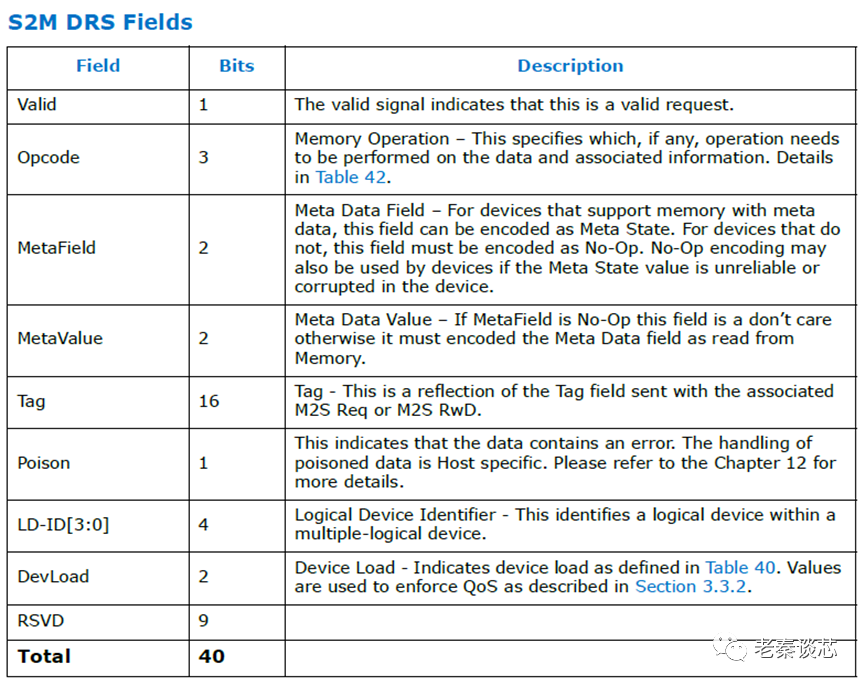

3.3.6 S2M数据响应(DRS)

DRS消息类包含从Subordinate到Master读取的内存数据。

3.3.7 转发和排序规则

在多跳互连网络中,Req和RwD消息的每一跳都需要信用值

如果请求和MemRdFwd或MemWrFwd指向相同的缓存行地址,则M2S Req通道中的CXL.mem请求不能发送MemRdFwd或MemWrFwd

NDR和DRS消息需要在源位置预先分配

在CXL.mem上,只有在写入完成后,写入数据才能保证对以后的访问可见

CXL.mem请求需要在设备上进行转发,而不依赖于任何设备启动请求

缓存行的M2S和S2M数据传输不能与其它缓存行交织

3.4 事务顺序总结(Transaction Ordering Summary)

没什么重要内容,暂时略过。

3.5 到设备挂载内存(DAM)的事务流

3.5.1 Type 1和Type 2的事务流

3.5.1.1 注释和假设

下面的示意图做了如下假设:

设备内部有一个设备一致性引擎,称作DCOH

DCOH里包含一个监听过滤器,是用来追踪监听设备的缓存

DCOH有一个偏置表查找机制,具体实现依赖于设备

设备特定的流程,如下图红色箭头所示,不需要完全遵守下图,具体实现取决于设备

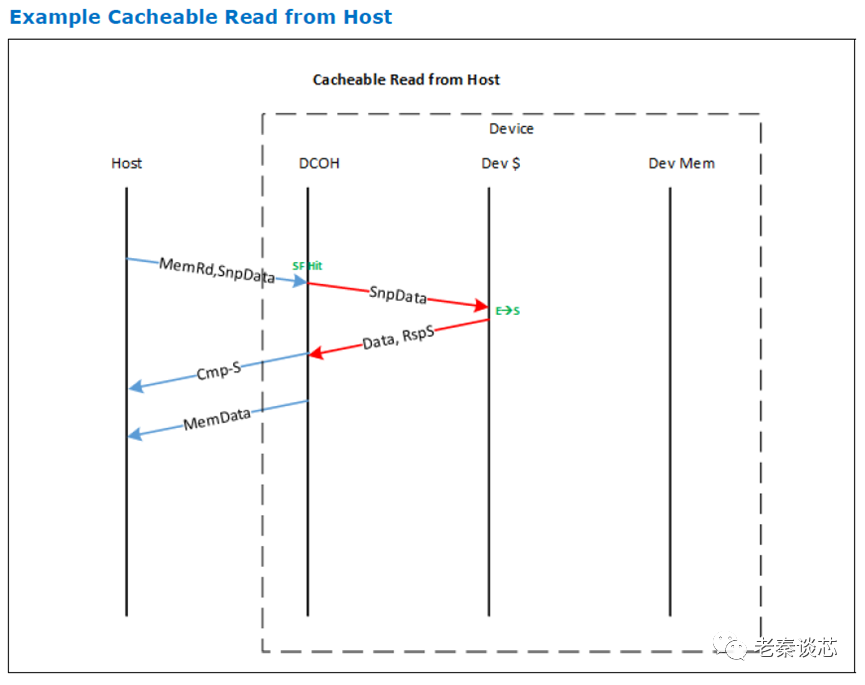

3.5.1.2 主机请求

主机发起的可缓存读(Cacheable read)示例如下图。主机请求获得一个缓存行的非独占副本。主机发送MemRd,SnpData给设备,设备DCOH接收到SnpData,在侦听过滤器中查找此缓存行。如果SF Hit(图中绿色字体),设备将该缓存行状态从Exclusive变为Shared(图中绿色字体)。随后将数据和响应发给DCOH,DCOH收到之后,回复Cmp-S给主机,然后将数据通过MemData发送给主机。

CXL协议中还给了好几个示例,就不一一贴上了。

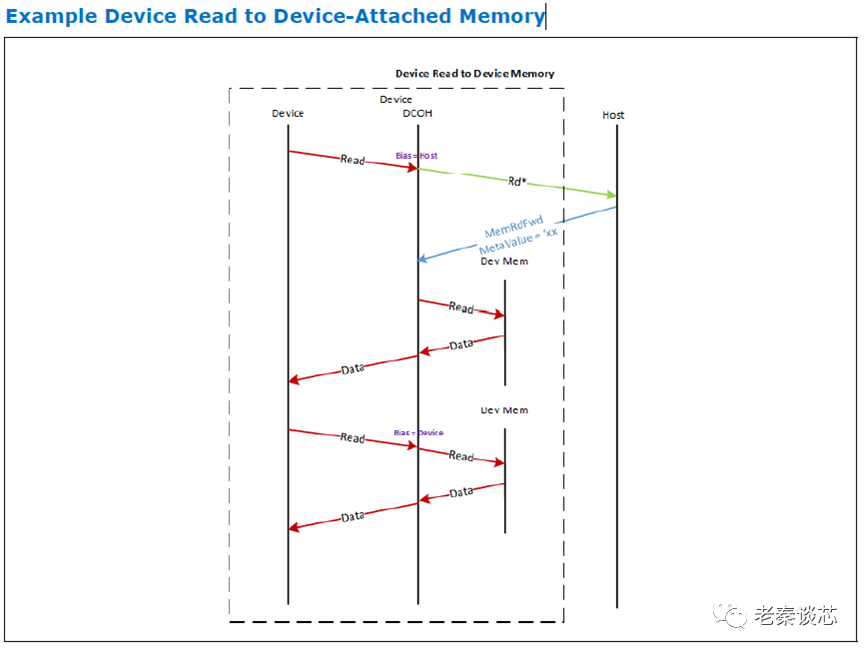

3.5.1.3 设备请求(主机偏向和设备偏向)

到设备挂载内存的设备读取示例如下图,包含两个流程分支。第一个,设备向设备挂载的内存发起读请求,由于配置成主机偏向(图中的紫色字体),设备要向主机发送一致性请求。主机在解析完一致性后,在CXL.mem上发送MemRdFwd以完成事务,此时设备可以在内部完成读取。第二个,配置成设备偏向,设备读取可以在设备内完成,不需要向主机发送请求。

同样的,后面还有几个流程示例,先不贴了。

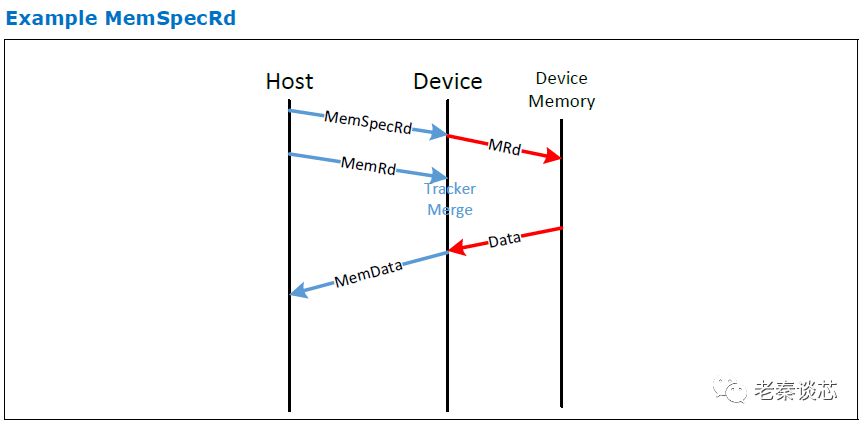

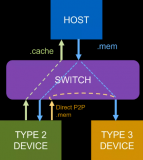

3.5.2 Type2和Type 3的内存流

为了支持节省延迟,CXL.mem包含一个推测性内存读取命令(MemSpecRd),用于在主代理解决一致性之前启动内存访问。解决完一致性问题后,主机可能会发出请求读取(MemRd,MemRdOwn),设备应与较早的MemSpecRd合并以节省延迟,见下图。为了避免性能影响,建议将MemSpecRd命令视为低优先级,以避免其它正常请求访问增加延迟。

3.6 Type 3设备的事务流

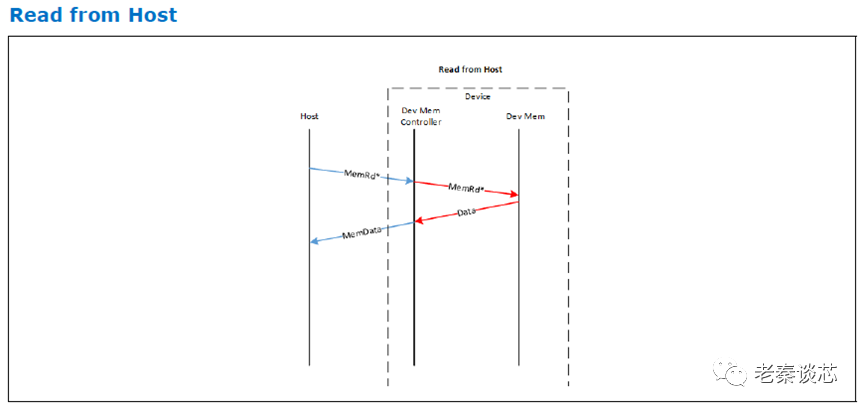

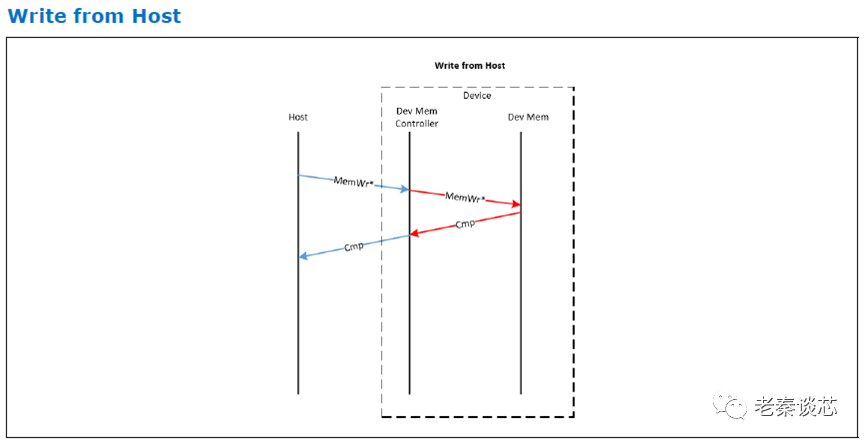

Type 3设备是内存扩展器,它既不缓存主机内存,也不需要主机主动管理设备缓存。因此,Type 3设备没有DCOH代理。主机将这些设备视为分解的内存控制器。到Type 3设备的事务流简化为两个类,即读和写。

M2S读取Type 2设备与Type 3设备的关键区别在于,Type 3设备没有S2M NDR响应消息。与Type 2设备一样,向Type 3设备的写入完成也需要S2M NDR Cmp消息

本章总结:这一章的内容极多,很多地方看的也是晕头转向,先搭个架子在这,以后有需要或者有时间再来仔细研究。

审核编辑 :李倩

-

cpu

+关注

关注

68文章

10854浏览量

211585 -

内存控制器

+关注

关注

0文章

40浏览量

8884

原文标题:技术分享 | CXL学习(五)

文章出处:【微信号:Ithingedu,微信公众号:安芯教育科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

内存扩展CXL加速发展,繁荣AI存储

韩国无晶圆厂初创公司Panmnesia展示第一个支持CXL的AI集群

研华科技推出SQRAM CXL 2.0 Type 3内存模块SQR-CX5N

如何利用CXL协议实现高效能的计算架构

打造异构计算新标杆!国数集联发布首款CXL混合资源池参考设计

新思科技CXL 3.1验证解决方案

国数集联研发出首款CXL多级网络交换机

三星研发CXL混合存储模组,实现闪存与CPU数据直传

利用CXL技术重构基于RDMA的内存解耦合

什么是CXL技术?CXL的三种模式、类型、应用

三星电子与红帽成功验证CXL内存操作

三星与红帽联合验证CXL内存与最新操作系统的兼容性

佰维公司成功推出支持CXL 2.0规范的CXL DRAM内存扩展模块

三星与红帽共同验证CXL技术,推动内存技术发展

佰维发布CXL 2.0 DRAM,赋能高性能计算

CXL.mem是什么?

CXL.mem是什么?

评论