作者:李 杨,苏和平,张 丹,许乔

摘要:针对现有的千兆以太网通信接口设计中存在的价格昂贵、不能胜任多路以太网传输等问题,提出并实现一种基于 FPGA+ARM 的多路千兆以太网通信接口模块。该设计分为 ARM 和 FPGA 两个部分,通过 STM32 微处理器带有的灵活静态存储控制器(FSMC)接口进行数据交换。ARM 部分通过发送函数、接收函数实现对以太网接口控制以及对数据的处理;FPGA 部分采用自顶向下的设计方法,通过时序转换模块、打包解包模块以及 MAC 控制模块实现以太网接口功能,并且定义了两个自定义协议,分别用于 ARM 与 FPGA 通信以及 FPGA 内部打解包模块与 MAC 控制模块的通信。搭建了硬件测试验证平台对设计进行了全面验证。硬件测试验证结果表明该设计能够正确实现以上功能。该方案成本低廉、扩展性强、支持多通道传输且支持网络风暴抑制,适用于对成本要求较高且需多通道以太网传输的场景。

引 言

随着人工智能、大数据和物联网等新兴技术的发展,原始数据井喷式地涌现出来,这也对接口提出了更高的要求[1⁃2],高速、可靠的传输接口往往是整个项目的技术关键。

近年来,国内对于以太网接口的研究取得了显著进步。文献[3⁃4]采用 Zynq⁃7000 芯片,利用 ARM+FPGA 架构在芯片内搭建了千兆以太网模块,传输速度分别为640 Mb/s 和 870 Mb/s。文献[5]采用国产 FPGA 芯片,自行研发了 SGMII core与 MAC core,实现了千兆以太网口的设计。文献[6]采用 DSP+FPGA 架构形式,搭建了多路串口、以太网通信系统,实现 40 路 RS 422/RS 485 通信功能。文献[7]采用 ARM 和 FPGA 芯片,利用 FSMC 实现两个芯片通信,采集多路光栅数据。文献[8]采用 FPGA设计实现了一种UDP 网络 IP 核,兼容GMII、RGMII以及SGMII接口,且移植性较强。

但是上述设计存在价格昂贵、不能胜任多路以太网传输任务、不支持风暴抑制等不足。而网络风暴抑制[9⁃11]的功能一般在软件层面,这会消耗大量资源算力。为此本文采用 ARM+FPGA 架构,通过 FSMC 总线进行芯片间通信,充分发挥 ARM 在控制方面及 FPGA 善于扩展和并行处理的优点,实现一种多通道、扩展性强、成本低廉且支持风暴抑制的千兆以太网接口模块。

1 整体结构

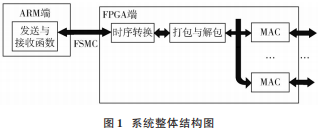

基于 FPGA+ARM 的多路千兆以太网通信系统的整体结构如图 1 所示。外部数据通过千兆网口进入 FPGA进行解包,然后通过 FSMC 总线[12]传递给 ARM 进行处理;下行数据由 ARM 发出,通过 FSMC 总线进入 FPGA中进行打包,根据命令从相应通道的千兆以太网口向外发送。

FPGA 与 ARM 之间通过 FSMC 总线连接,如图 2 所示。FSMC 总线包含 6 位地址总线、16 位数据总线以及控制总线。

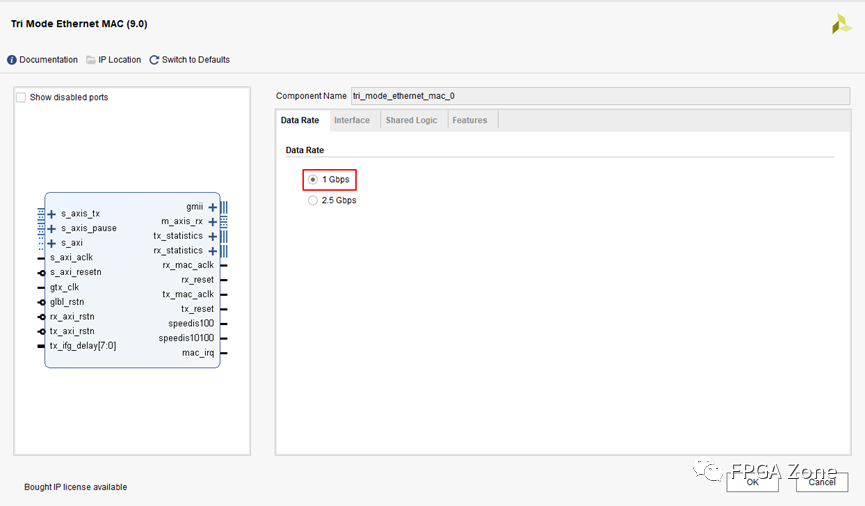

2 FPGA 设计

FPGA 芯 片 选 用 Altera 公 司 的 EP4CE10F17C8 芯片,其拥有 10 320 个逻辑单元,可以满足本系统功能要求。ARM 处理器选用 ST 公司的 STM32F407IG,具有Cortex⁃M4处理器内核,1 MB FLASH 且具有 FSMC。

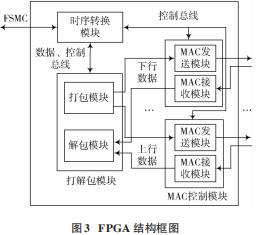

FPGA 用 Verilog语言开发,FPGA 结构框图如图 3所示,由时序转换模块、打包解包模块和 MAC 控制模块三部分组成,其中可以接多个 MAC接收模块。

2.1 时序转换模块

时序转换模块将 FSMC 复杂时序转换为较简单时序,同时将一路 FSMC转换多路内部总线,其中包括传递数据的总线和各个模块的控制总线。其中转换出来的控制总线使能各个模块功能,访问各个模块的寄存器。

2.2 打包模块和解包模块

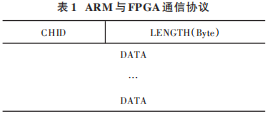

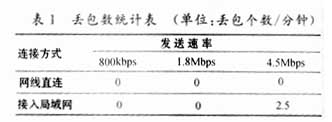

打包解包模块约定了 ARM 与 FPGA 通信的协议,如表 1 所示。在要发送的数据前添加要发通道号以及待发送数据的字节长度,以便于打包模块知道数据应当发送到哪个 MAC 和解包模块,以及数据包来自哪个 MAC,同时将一路内部数据总线又分为多路数据总线,与多个MAC相连。

发送功能:当检测到发送开始寄存器操作后,将发送数据寄存器的数据写入前级 FIFO 缓存,直到检测到发送完成寄存器操作,停止向前级 FIFO 缓存,接着开始检查保存包是否正确并产生接收完成信号,若当前包不正确,读出当前包同时丢弃,正确则保留。根据表 1 协议判断当前包要发送到的 MAC,待其可以接收数据时向其发送。

接收功能:4 个通道的数据首先进入 4 个通道 FIFO中,随后通道扫描器会依次循环扫描这 4 个通道 FIFO,若该通道使能且有数据,就将该通道数据缓存到前级FIFO 并产生接收完成信号,等待 ARM 读取数据,待ARM 读取完继续循环之前操作。

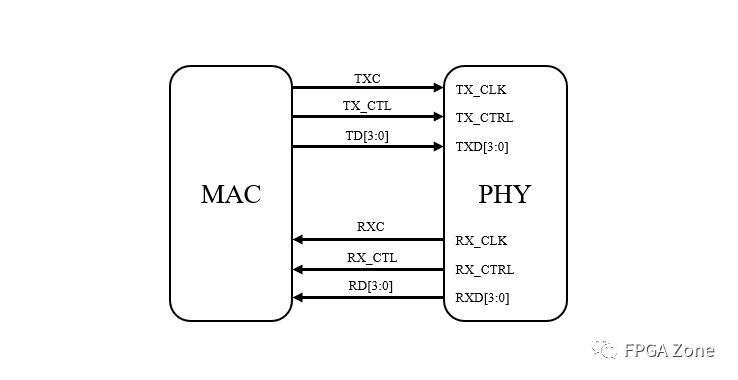

2.3 MAC模块

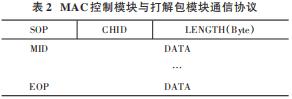

MAC 控制模块实现以太网的数据链路层协议,同时定义了与打解包模块的通信协议,如表 2 所示。这个协议是在表 1 通信协议的基础上,在包头添加包头标志SOP,包中部添加中部标志 MID,在包尾添加包尾标志EOP,以便于以数据包的形式进行传输和处理。设计功能:速率为 1 000 Mb/s,帧间隔可配,支持自动填充,支持 CRC 校验,支持广播/组播风暴抑制,支持 MAC 地址白名单。

MAC 发送的逻辑:首先有 MAC 数据帧待 MAC 模块发出,等待设定的帧间隔时间结束,接着发送前导码和帧定界符,然后发送待发送 MAC 数据帧,若长度小于60 B则用零填充至 60 B,最后发送循环校验序列。

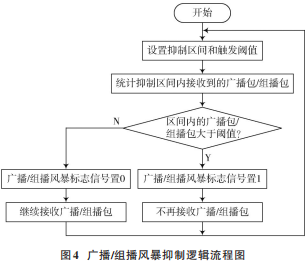

广播/组播风暴抑制逻辑如图 4 所示。根据设定时间以及设定的广播包阈值,如果在设定的时间内接收的广播包数量超过阈值,进行广播包抑制。同理,组播风暴抑制逻辑和广播风暴抑制逻辑相同。

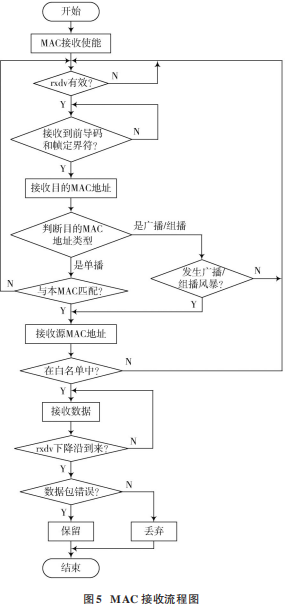

MAC 接收的逻辑流程图如图 5 所示。接收使能MAC 模块开始接收,若 rxdv 信号有效且接收到前导码和帧定界符,则进行下一步的目的 MAC 地址接收。接下来进行广播/组播/单播的类型判断,广播或组播的处理类似,会判断是否已经发生广播/组播风暴,发生则不再接收数据,没有就继续;单播的话不需要考虑抑制,所以这步跳过。接下来接收源 MAC 地址,仅单播需要判断是否源 MAC 地址在 MAC 地址白名单中,不在白名单则停止操作,在就接收数据,直到 rxdv 变为低电平。最后判断接收是否错误,包括长度和 CRC校验。

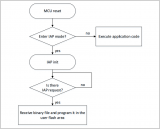

2.4 ARM 系统软件设计

ARM 端程序是运行在 μCOSⅢ操作系统[13]之上的,ARM 程序使用 C 语言编写,ARM 程序分为两个模块,即发送程序和接收程序。

当任务调用发送函数,向发送开始寄存器写操作,接着向发送数据寄存器发送通道号以及数据长度,然后向发送数据寄存器发送待发送数据,发送数据完成后,向发送完成寄存器写操作。

当有 ARM 检测到接收中断时,ARM 查询中断状态寄存器,确定是接收中断,同时清除该中断标志,然后进行读取操作。同时接收过程也支持轮询寄存器,方法与中断接收类似,不再赘述。

3 验 证

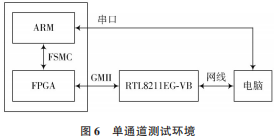

测试内容包括单通道和多通道功能验证。单通道验证通过如图 6 所示的测试环境验证,多通道的验证通过 ModelSim 仿真验证。

3.1 单通道验证

单通道测试环境如图 6 所示。待测试设计模块外接一个 RTL8211EG⁃VB 芯片的扩展板,然后通过网线与电脑相连。用 Wireshark 软件抓取 ARM 发来的数据帧,验证本系统的发送功能;采用科来数据包生成器生成验证接收功能所需的各种数据帧,使用科来数据包播放器从电脑端向本接口发送数据帧,并用串口助手查看本接口接收到的包数。

测试项目分为两部分:发送功能测试和接收功能测试。发送功能测试需要验证发送内容是否正确,需要填充的数据帧是否填充。接收功能测试需要验证正确接收、MAC地址白名单功能以及广播/组播风暴抑制功能。

3.1.1 发送功能验证

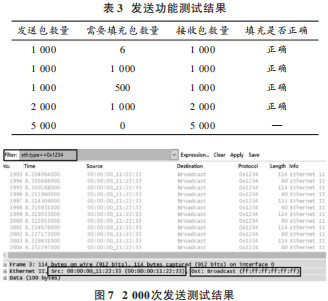

测试工具为 Wireshark。测试内容:ARM 端生成一些待发送数据,统计电脑接收数据包个数,以及检查要填充的数据包是否填充。测试结果见表 3。其中,图 7是 2 000 次发送测试的 Wireshark 抓包图。为了不影响抓取,固定 MAC帧类型为 0x1234,设计系统的 MAC地址为00:00:00:11:22:33,以广播的形式发包进行测试。

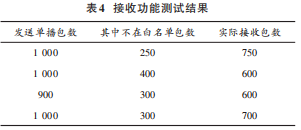

3.1.2 接收功能验证

1)正常接收验证

测试工具:科来数据包生成器、科来数据包播放器、串口调试助手。向设计接口发送不在白名单中的单播包,验证接口的接收功能以及地址白名单功能。具体测

2) 广播包/组播包风暴抑制

测试工具:科来数据包生成器、科来数据包播放器、串口调试助手。测试中固定风暴抑制区间间隔为65 ms。设置不同的广播包接收的抑制阈值,构造广播包与单播包各不同的组合,将其循环向设计接口发送。测试结果见表 5,其中理论接收包数等于发包总数乘以一次循环中不会发生风暴的比例。

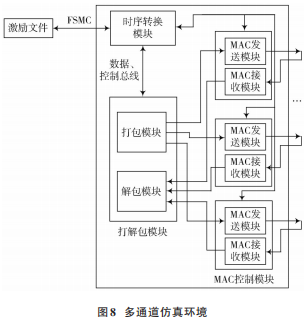

3.2 多通道验证

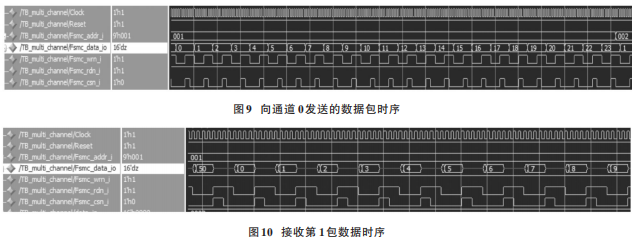

仿真环境如图 8所示,例化 3个 MAC 模块,将这 3个模块的 MAC 发送端口和接收端口相连构成回环。激励文件模拟 FSMC 时序,通过 FSMC 接口分别向通道 0,1,2各发送一包数据。这三包的构成一致都是从 0 开始递增,且结尾为固定值 1,他们的长度分别是 50 B,46 B,60 B。图 9是这三包数据中的第一包数据。

根据表 1 所示的协议,经过回环得到的数据包头部是该数据包的长度与通道号。要验证多通道功能的正确性,需保证接收的数据包头部的长度和通道号正确且后面数据部分正确。仿真测试中将包头的[15:14]位表示通道,[10:0]位表示数据部分长度,单位为字节。如图 10所示,按照协议解析,表示通道 0,长度为 50 B。其余两包内容类似,由于篇幅原因就不附上,同时核对各包实际数据部分也与对应发送包相同。

经过以上一系列测试,数据发送和接收功能正常,传输时不丢包,且能稳定可靠工作,满足设计要求。

4 结 语

本文针对多路以太网通信需求,基于 ARM 和 FPGA特点,综合两者的优势提出一种基于 ARM+FPGA 的多路千兆以太网通信系统。实现了 MAC 帧发送和接收、广播/组播风暴抑制、帧间隔配置、MAC 白名单和错误检测。从验证结果来看,系统运行稳定可靠,满足设计需求。本设计只针对千兆以太网进行设计,在实际应用中可以做成 10M/100M/1 000M 自协商,以适应市场需求。本文设计的以太网接口相比其他设计,具有多通道和硬件风暴抑制的功能,适合多通道的以太网传输。由于日益紧张的国际形势,使得国内对于芯片国产化的观念日趋强烈,下一步将考虑实现此接口在国产化芯片上的移植应用。

审核编辑:郭婷

-

FPGA

+关注

关注

1625文章

21665浏览量

601776 -

ARM

+关注

关注

134文章

9043浏览量

366781 -

以太网

+关注

关注

40文章

5374浏览量

171075

原文标题:论文速览 | 基于FPGA+ARM多路千兆以太网通信接口设计

文章出处:【微信号:现代电子技术,微信公众号:现代电子技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于Xilinx FPGA的千兆以太网控制器的开发

FPGA+DSP;FPGA+ARM硬件设计

TM1300芯片的以太网通信接口的设计和实现

LPC23xx的自适应以太网通信接口设计

S7-200SMART开放以太网通信

基于FPGA的UDP RGMII千兆以太网通信方案

基于FPGA+ARM多路千兆以太网通信接口设计

基于FPGA+ARM多路千兆以太网通信接口设计

评论