概述

网表约束MARK_DEBUG可应用在源码中的任意一个网络信号上,被施加该约束的网络信号在调试界面中可见,从而方便在线调试时快速定位该信号,提升调试效率。话不多说,下面以FPGA中的在线逻辑分析仪(ILA)的调试实践为例,让大家感受一下网表约束MARK_DEBUG的妙用。

工程实践

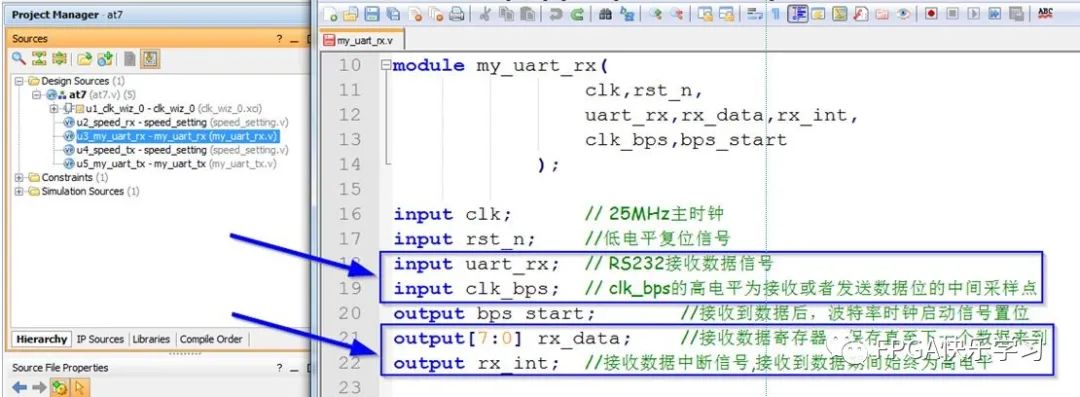

以STAR FPGA开发板中的at7_ex10工程为例,这个工程实现UART传输的loopback功能。该实例中使用在线逻辑分析仪希望探测到FPGA端接收并进行串并转换过程中所设计的一些主要信号。

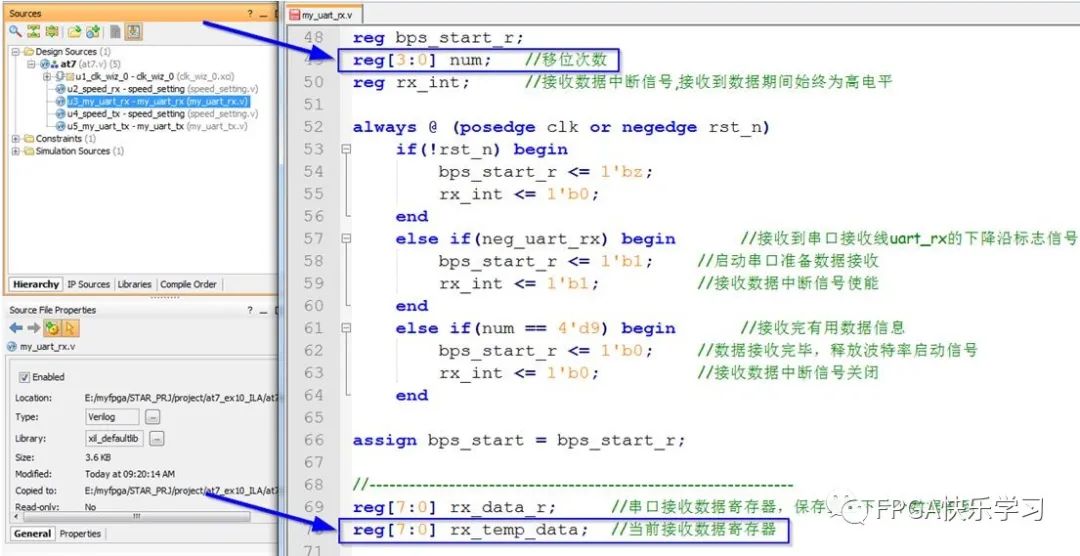

首先需要找出待探测的信号。如图1和图2所示,在my_uart_rx.v模块中,uart_rx、clk_bps、rx_data、rx_int、num、rx_temp_data是需要探测监控的信号。

图1 识别需要进行探测的信号1

图2识别需要进行探测的信号2

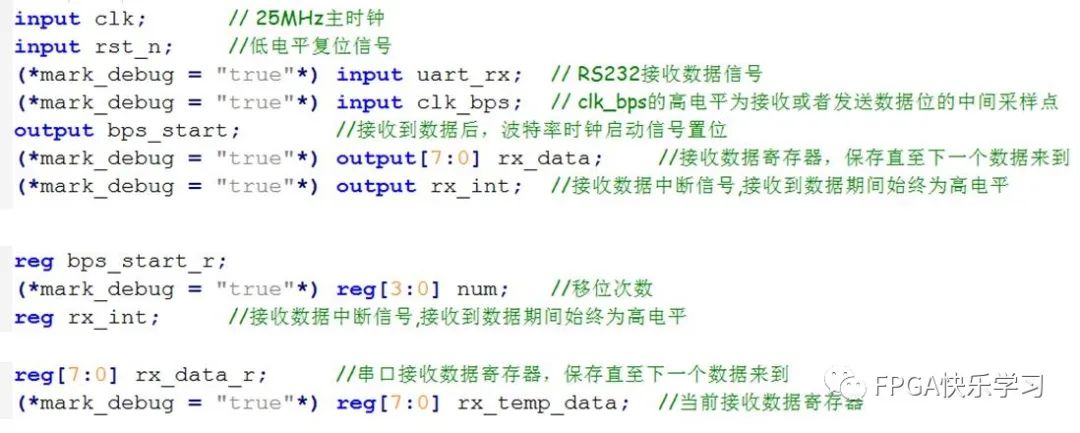

如图3所示,在待探测信号定义申明前面增加语句:(*mark_debug= "true"*)。当然了,如果后续不探测这个信号了,直接修改“true”为“false”就可以。

图3 标注需要探测的信号

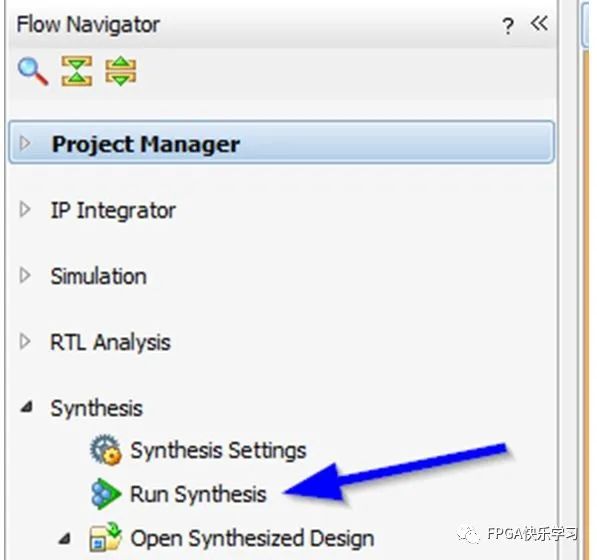

完成对探测信号的mark_debug标记后,如图4所示,点击“Synthesis à Run Synthesis”对工程进行综合编译。

图4 工程的综合编译

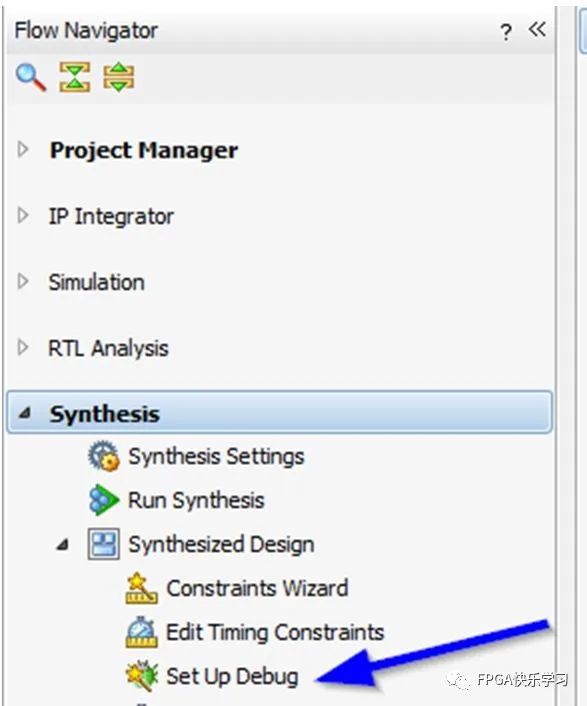

综合编辑完成后,如图5所示,接着点击“Synthesis à Synthesized Design à Set Up Debug”。

图5 Set Up Debug菜单

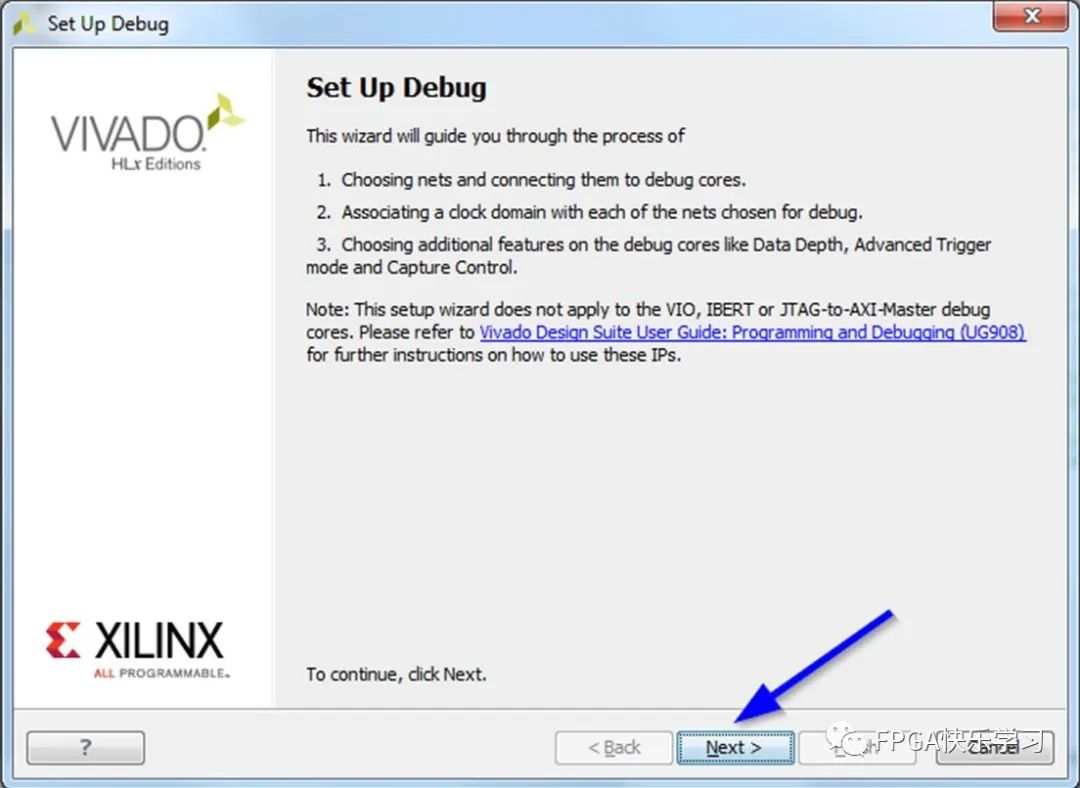

如图6所示,点击Next进入下一步。

图6 Set Up Debug Wizard页面

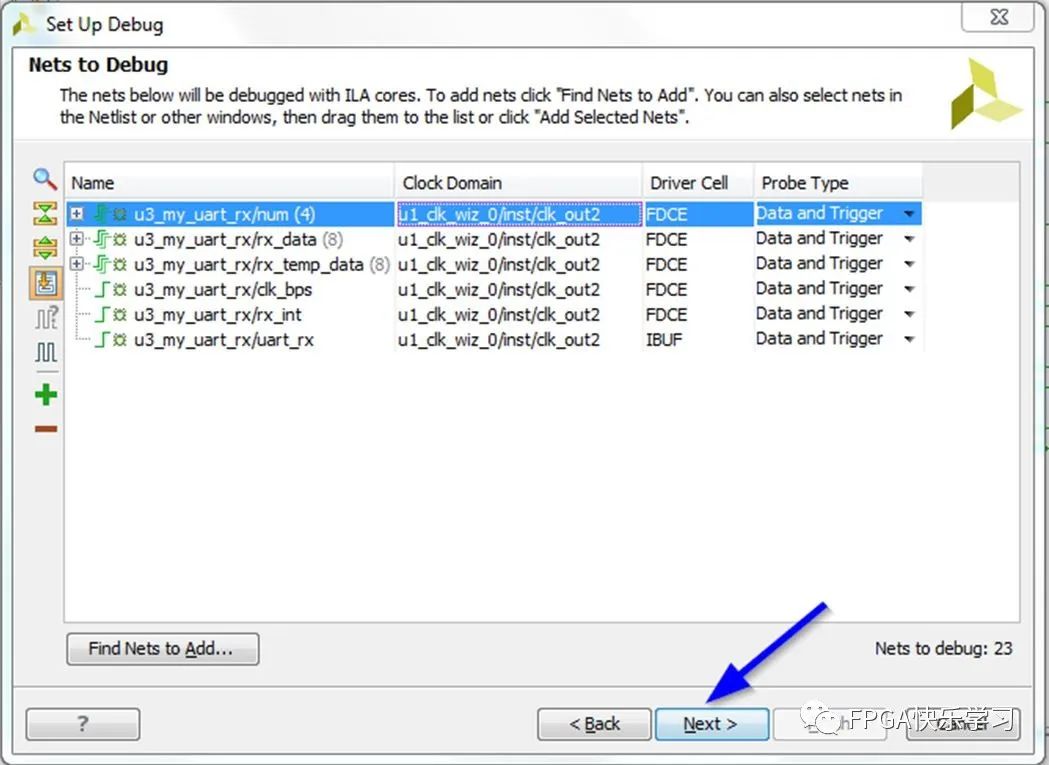

如图7所示,Nets to Debug界面显示的信号正是我们在前面的工程源码中标记了(*mark_debug = "true"*)的信号。如果没有被标记过的信号,我们希望添加到Nets to Debug界面中,就要点击Find Netsto Add…按钮逐个查找并添加了,效率要明显低于直接在工程源码中事先标记。对这些调试信号做采样和触发属性设置后,点击Next进入下一页面。

图7 Nets to Debug页面

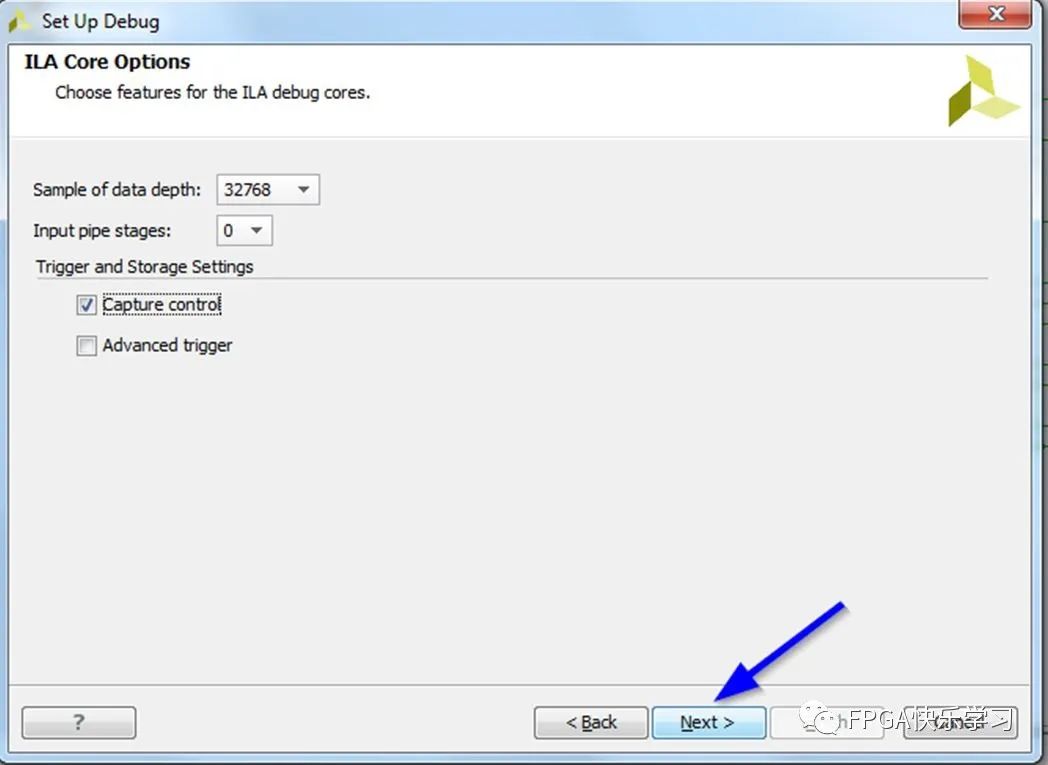

如图8所示,ILA Core Options页面中,可以设定探测信号的采样深度、缓存寄存器等级和信号采集触发相关控制选项。完成设置后,点击Next进入下一页面。

图8 ILA CoreOptions页面

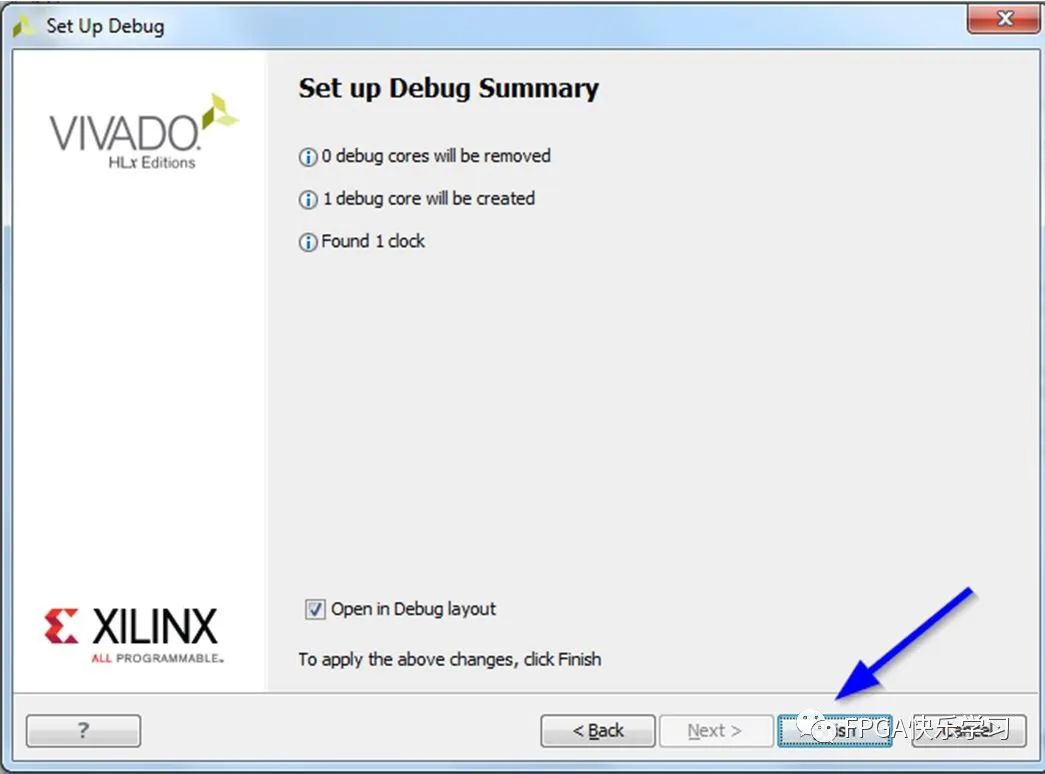

如图9所示,Set up Debug Summary中点击Finish完成设置。

图9 Set upDebug Summary页面

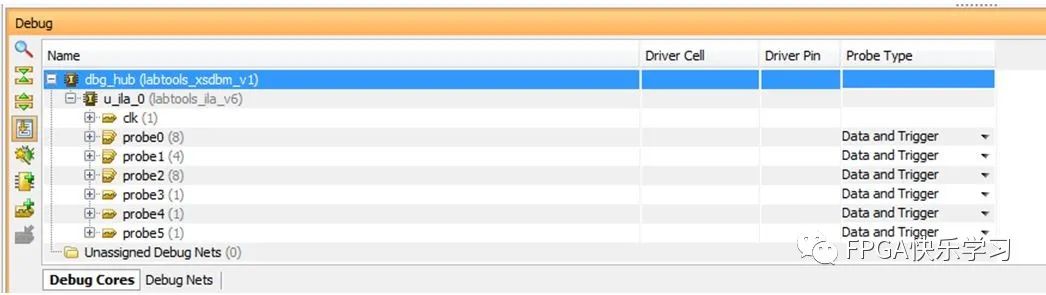

此时,如图10所示,所有的探测信号出现在了Debug窗口中。

图10 Debug窗口

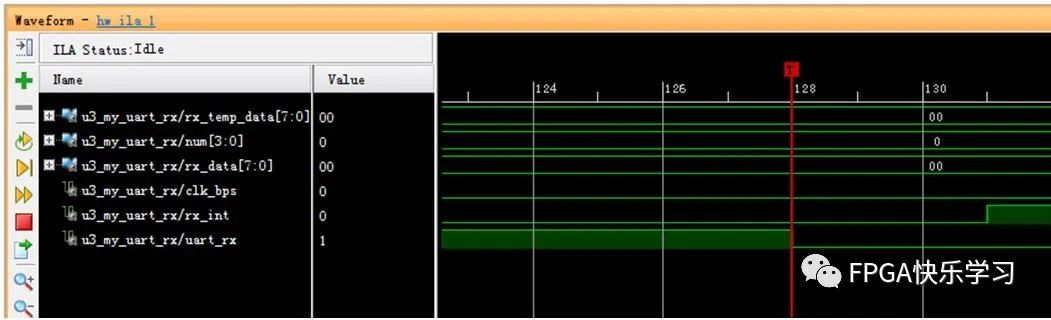

接着,重新对工程进行编译,将产生的比特流烧录到FPGA器件中,最终便能捕捉到如图11所示的实际的信号波形。

图11 触发位置的波形

审核编辑 :李倩

-

FPGA

+关注

关注

1635文章

21837浏览量

608344 -

源码

+关注

关注

8文章

656浏览量

29786 -

约束

+关注

关注

0文章

82浏览量

12813

原文标题:物理约束实践:网表约束MARK_DEBUG

文章出处:【微信号:FPGA快乐学习,微信公众号:FPGA快乐学习】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

xilinx FPGA IOB约束使用以及注意事项

浅谈多目标优化约束条件下充电设施有序充电控制策略

时序约束一主时钟与生成时钟

常用时序约束使用说明-v1

与非门构成的基本RS触发器的约束条件是什么

SR锁存器有约束项的原因

两种SR锁存器的约束条件

加法进位链的手动约束

Xilinx FPGA编程技巧之常用时序约束详解

时序约束实操

Xilinx FPGA的约束设置基础

物理约束实践:网表约束MARK_DEBUG

物理约束实践:网表约束MARK_DEBUG

评论