作者:赵欢 ,朱 倩 ,唐 衡

引 言

随着 FPGA 数字信号处理系统复杂度不断提高,FPGA 信号处理系统的功能验证已经成为影响产品上市时间和成本的关键[1]。尽管在验证领域已经发展出多种自动测试方法,但是针对信号处理算法进行验证时,仍然需要手动编写代码搭建仿真平台[2],生成仿真激励,效率较低。信号处理系统往往包含大量复杂的算法[3],对于验证人员编写代码的经验及技能要求较高。

针对这一情况,本文提出了一种基于 Simulink 与IES 联合搭建的功能验证平台。使用 Simulink 的 HDLCoder自动生成代码完成仿真平台中的信号处理算法部分。首先,利用 Matlab强大的分析、计算和可视化功能,使用 Simulink 对算法进行建模仿真[4],当仿真结果达到设计要求后,再使用该模型直接生成 HDL 代码[5],从而大幅提高了验证平台开发效率,避免了对复杂信号处理验证模型的硬件语言设计,提升了平台的复用性和仿真平台搭建效率。同时,由于无需手动编写代码,也避免了人为引入的错误,提升了验证平台的可靠性。

1 SMA 基带信号处理

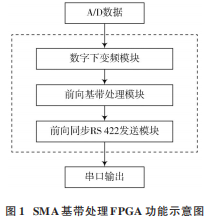

本文验证的SMA基带信号处理FPGA,是SMA(S⁃BandMultiple Address)测控终端系统的重要组成部分[6],主要完成前向链路中的中频信号解调、解扩,将解调结果通过 RS 422 接口输出至管理单元。该 FPGA 的主要功能

模块包括:

1)数字下变频模块:输入 A/D 信号的采样,将输入中频信号下变频到基带。

2)前向基带处理模块:生成解调所需的 GOLD 码;实现频率捕获和伪码捕获;在捕获的基础上实现信号跟踪并对相关积分结果进行自动增益控制;解扩和位同步。

3)前向同步 RS 422 发送模块:通过 RS 422 接口输出解调数据。功能示意图如图 1所示。

2 联合仿真平台

2.1 验证平台概述

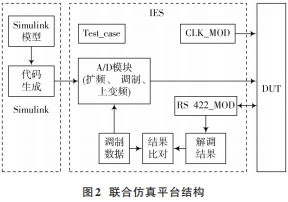

本平台主要用于验证 SMA 信号处理 FPGA 的解调功能和算法性能,确认该 FPGA 是否能够正确解调规定调制格式的输入信号,并确认是否满足接收载噪比、捕获时间、捕获频偏范围、跟踪多普勒变化率等性能要求。本平台采用 IES 和 Simulink 联合的仿真方法,在被测设计外围搭建基于 System Verilog 和 Verilog 混合编程的仿真平台。使用 Simulink 搭建信号处理模型,使用System Verilog搭建其他外围接口模型。主要包括:

1)使用 Simulink 搭建信号处理模型,将调制数据进行扩频、调制、成型滤波、上变频后通过 A/D 接口输入至 DUT,然后自动生成 Verilog代码用于仿真。

2)RS 422 接口模型,使用 System Verilog 搭建,接收 DUT 输出的解调数据并发送至 scoreboard 用于数据比对。

3)时钟模型,使用 System Verilog 搭建,为测试环境和 DUT提供工作时钟。

4)数据比对模块,基于System Verilog的scoreboard,自动比对测试环境发送的调制数据和 DUT 输出的解调结果,测试是否存在误码。

5)Test_case,用例控制模块,使用 System Verilog 生成不同的Test_case 以验证被测设计在不同输入条件下是否满足算法性能要求。

除了验证解调数据正确性以外,在 Simulink 中搭建信号处理模型时,将上变频模块的载波频率和码NCO的码速率控制字设置为外部输入可控,通过 Test_case灵活控制不同用例,测试 DUT 在不同输入载波频率下的捕获和跟踪性能是否满足要求。联合仿真平台如图2所示。

2.2 Simulink信号源建模

根据对被测设计的分析,A/D 信号源模块的主要技术指标包括:A/D 接口输入信号位宽为 12 bits,A/D 采样频率为 100 MHz。扩频模式为直接序列扩频模式,扩频码为 GOLD 码,码长为 1 023,码速率为 3.069 Mc/s,G1生 成 多 项 式 为 x10 + x8 + x7 + x4 + x2 + x + 1 ,初 相 为1101111100,G2 生 成 多 项 式 为 x10 + x7 + 1 ,初 相 为1001001000。需要对扩频后的序列进行成型滤波,滤波器选择成型系数为 0.6的平方根升余弦滤波器。应将滤波后的信号调制至中频,中频为 30 MHz,并且为了验证性能需求,载波多普勒、码多普勒、载噪比需要根据用例要求灵活控制。

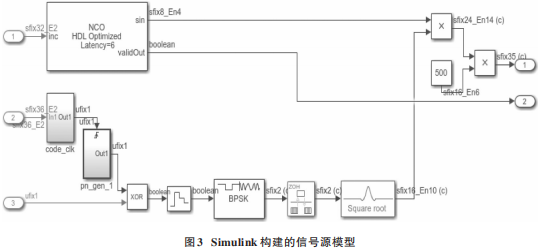

依据上述要求,设计了 A/D 信号源模型如图 3 所示,整个模型由扩频码时钟模块、GOLD 码发生器模块、BPSK 调制模块、成型滤波器模块和上变频模块构成。

1)扩频码时钟模块 code_clk:扩频码时钟模块使用NCO 模型产生正弦波输出,然后使用比较器将正弦波转换成方波,作为 GOLD 码发生器模块的 Trigger 信号。为了能够根据用例设置灵活控制码钟频率,将 NCO 频率控制字设置为外部输入模式(Input Port)。

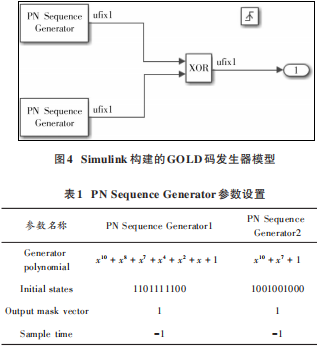

2)GOLD 码发生器模块 pn_gen_1:GOLD 码发生器模 块 由 2 个 PN Sequence Generator 构 成 ,将 2 个 PNSequence Generator 的输出异或后得到 GOLD 码[7],模型结构如图 4 所示,2 个 PN Sequence Generator 的参数设置见表 1。

3)BPSK 调制模块:使用 BPSK 模型对扩频后的结果进行 BPSK 调制。

4)成型滤波器模块:成型滤波器模块用于消除码间串扰,本文中使用 Raised Cosine Transmit Filte模型实现,设置滤波器类型为平方根升余弦滤波器,滚降系数为 0.6。

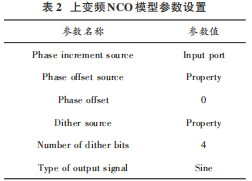

5)上变频模块:上变频模块使用 NCO HDL模型实现,为了能够根据用例设置灵活控制载波频率,将载波NCO 频率控制字设置为外部输入模式(Input Port),其他参数设置见表2。设置载波 NCO 输入频率为90 kHz~30 MHz时,该 NCO 输出信号的频谱如图 5所示。

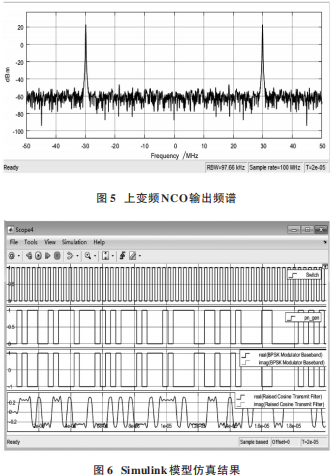

信号源模型仿真结果如图 6 所示,图中信号波形从上到下分别为:扩频码时钟、扩频码序列、BPSK 调制输出、成型滤波器输出。

需要注意的是:为了能够自动生成代码,构建仿真模型必须使用 hdllib 内的模型,hdllib 是支持生成 HDL代码的模型库[8],并且需要将模型的输入设置为定点输入,这样模型自动成为定点模型,生成代码时即生成定点代码[9⁃10]。

2.3 Simulink模型的 HDL代码直接生成

搭建 Simulink 模型并完成仿真后,就可以直接在HDL Coder中生成 HDL 代码[11]。Simulink 使用高层次综合合成技术,将硬件可实现的 Simulink 模型编译为可读、可追溯且可模型化的 VHDL 或 Verilog HDL 代码,此代码经过优化可以跨任意 FPGA、ASIC 或 SoC 硬件进行移植[12⁃13]。代码生成的过程如下:

1)将需要生成代码的部分封装为一个子系统。

2)检查模型是否可综合:选中子系统后右键选择HDL Code→check subsystem compatibility,如果检查通过,可继续生成代码;如果失败,则需要进行模块替换。

3)参数设置,可以设置生成的语言类型、复位信号极性等。

4)设置完成后,右键点击需要生成的子系统,选择HDL CODE→Generate HDL for subsystem,最 终 生 成代码。

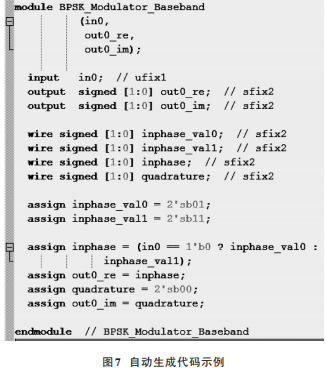

其中一个自动生成模块——BPSK 调制模块代码如图 7 所示,可以看出最终生成代码有较好的可读性,便于仿真调试和修改。

3 仿真结果与分析

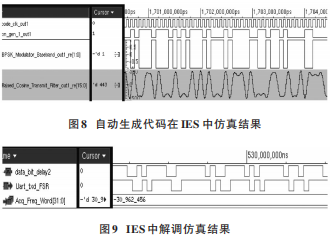

以载噪比 Eb N0=10 dB、初始多普勒偏差 90 kHz、多普勒变化率 1 kHz/s的测试用例为例,IES仿真结果如图 8和图 9所示。

图 8 中,仿真波形从上到下依次为码发生器时钟、扩频码时钟、扩频码序列、BPSK调制输出、成型滤波器输出。图 9 中,data_bit_delay2 是仿真平台发送的调制数据,Uart_txd_FSR 是 DUT 输出的解调数据,通过比对可 以 确 认 ,输 出 解 调 数 据 与 发 送 的 调 制 数 据 一 致。Acq_Freq_Word为捕获得到的载波频率,被测 FPGA 内部 NCO 时钟为 12.5 MHz,计算可得捕获得到的频率为( -30 962 456 × 12.5 × 106) 232 =-90.112 Hz。

综上可以确认被测FPGA能够在载噪比Eb N0=10 dB、初始多普勒偏差-90 kHz 时成功捕获,并且跟踪、解扩、解调数据,验证了设计功能的正确性和性能指标。

4 结 语

本文提出了一种基于 Simulink与 IES联合搭建的功能验证平台,给出了联合仿真实例,成功对 SMA 信号处理 FPGA 进行了功能和性能验证。该仿真平台利用了Matlab 丰富的信号处理算法模型,生成了验证平台中的关键算法模块代码,极大地降低了验证平台的开发难度,提升了仿真平台的开发效率,提高了平台的复用性。同时,避免了手动编写代码而引入的错误,提升了环境的可靠性,对其他类似复杂信号处理类 FPGA 设计的验证具有极大的参考价值。

审核编辑:郭婷

-

FPGA

+关注

关注

1631文章

21808浏览量

606807 -

代码

+关注

关注

30文章

4841浏览量

69225

原文标题:论文速览 | 基于Simulink代码生成的 FPGA 信号处理系统仿真验证平台

文章出处:【微信号:现代电子技术,微信公众号:现代电子技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Simulink与 MATLAB 的结合使用 Simulink中的信号处理方法

Simulink模型仿真与分析技巧

Matlab/Simulink/Stateflow建模开发及仿真测试

FPGA仿真黑科技\"EasyGo Vs Addon \",助力大规模电力电子系统仿真

解决方案丨EasyGo新能源系统实时仿真应用

新的 MathWorks 硬件支持包支持从 MATLAB 和 Simulink 模型到高通 Hexagon 神经处理单元架构的自动化代码生成

EasyGo实时仿真丨PCS储能变流器控制仿真应用

信号采集与处理系统通常由哪些模块组成

EasyGo使用笔记丨分布式光伏集群并网控制硬件在环仿真应用

基于MATLAB的信号处理系统与分析

Vivado 使用Simulink设计FIR滤波器

Simulink自动生成代码现阶段的学习笔记

基于Simulink代码生成的FPGA信号处理系统仿真验证平台

基于Simulink代码生成的FPGA信号处理系统仿真验证平台

评论