电子发烧友网报道(文/周凯扬)尽管制造工艺的推进速度已经放缓,芯片设计的复杂程度依然丝毫不减,对于芯片设计者来说,在这样一个AI驱动的时代下,如果不能将AI为自己所用,无疑会让自己乃至整个设计项目的效率停滞不前。虽说大家都已经察觉到AI开始渗透进EDA工具中,那么现阶段的AI,究竟能解决哪些设计上的挑战呢?

验证

验证是芯片设计中最大的挑战之一,我们已经见识过了价格高昂的专用验证硬件,以及验证上云的潮流,这些都足以说明验证是芯片设计中一个多么耗费资源的过程,这里指代的也不仅仅是硬件计算资源,还有时间资源。验证所耗时间甚至可能高过其他流程,这些年诸多芯片开发团队中的验证工程师人数也在逐渐增长,增速甚至已经超过了设计工程师,然而业内却很少有人去优化验证这个流程。

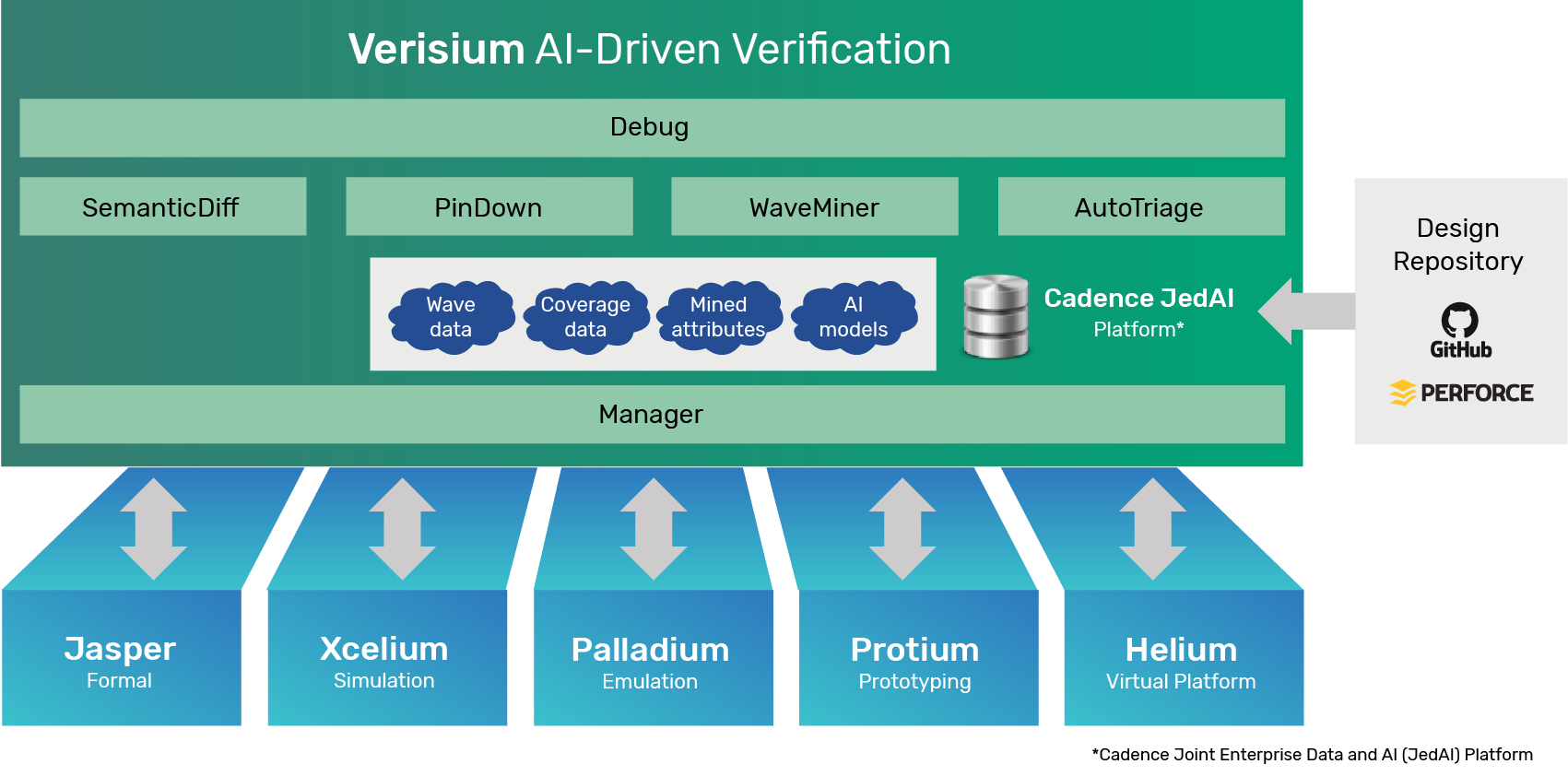

AI的出现终于让这个缺口出现了松动,不少厂商都开始利用AI去优化验证这一流程,比如通过覆盖率预测和激励优化来加速覆盖率达标。Cadence也在今年发布了Verisium AI驱动验证平台,根据Cadence的说法,Verisium 的出现意味着SoC验证从单运行单引擎算法,转向了由AI和大数据辅助的多运行多引擎算法,从而减少了调试周转时间、提高了调试效率,还会自动对失败测试案例分类,减少人为分析的工作量。

模拟设计自动化

相对数字IC设计来说,模拟IC的设计显然在自动化程度上还是差了不少的。在数字电路的设计过程中,整个流程的自由度是在逐级降低的。模拟电路设计虽然也是如此,但其下降幅度还是不比数字电路设计的,尤其是在布局布线和验证上,所以自动化一直没有提上日程,现阶段大部分模拟电路设计主要还是取决于设计者本身的直觉、技能和经验。

有了AI的帮助后,EDA工具在大量数据的训练下给出了先进的机器学习算法,使得模拟电路的布局布线有了更高效的自动化流程,尤其是在约束提取和生成,布局优化上,模拟电路的优化和生成及仿真验证也可以在AI驱动下获得提速。如此一来,每个模拟电路设计的迭代数量会进一步减少,芯片的上市周期也随之缩短。

系统集成

近几年流行起来的UCIe、Chiplet、3D封装等,其实都是一个系统集成的概念。以此引入的设计与制造优化方案也受到了持续关注,比如DTCO等。如何集成更多的晶体管、更多的内存以及逻辑+内存集成,还有最后软件联合硬件的热管理等,都是系统集成需要考虑的问题。

那么AI该如何从系统集成上进行优化呢?答案就是提供一个更高效探索设计空间的路线,能够给出预测模型和更快的实现方式,例如新思的DSO.ai和Fusion Complier,就提供了完备的AI设计方案,以求实现更好的PPA和更快的设计验收。据了解,新思的这些方案最近在台积电的N3E工艺上得到了验证,为高性能计算、AI和移动设备等计算密集负载提供了增强的功耗、性能和良率。

写在最后

其实一旦芯片设计进入AI辅助的时代,也对设计工程师们提出了相应的更高要求,因为不少低级设计问题已经被AI预测、优化和生成给解决了。设计工程师们需要在更高层级的设计上实现创新,比如系统/软件联合优化等等,这样自己才不会被“优化”掉。设计工程师们的专业技能,未来也会更加趋向于数据科学家需要掌握的技能,而数据科学家们也说不定会因此获得抢设计工程师饭碗的机会。

验证

验证是芯片设计中最大的挑战之一,我们已经见识过了价格高昂的专用验证硬件,以及验证上云的潮流,这些都足以说明验证是芯片设计中一个多么耗费资源的过程,这里指代的也不仅仅是硬件计算资源,还有时间资源。验证所耗时间甚至可能高过其他流程,这些年诸多芯片开发团队中的验证工程师人数也在逐渐增长,增速甚至已经超过了设计工程师,然而业内却很少有人去优化验证这个流程。

AI的出现终于让这个缺口出现了松动,不少厂商都开始利用AI去优化验证这一流程,比如通过覆盖率预测和激励优化来加速覆盖率达标。Cadence也在今年发布了Verisium AI驱动验证平台,根据Cadence的说法,Verisium 的出现意味着SoC验证从单运行单引擎算法,转向了由AI和大数据辅助的多运行多引擎算法,从而减少了调试周转时间、提高了调试效率,还会自动对失败测试案例分类,减少人为分析的工作量。

模拟设计自动化

相对数字IC设计来说,模拟IC的设计显然在自动化程度上还是差了不少的。在数字电路的设计过程中,整个流程的自由度是在逐级降低的。模拟电路设计虽然也是如此,但其下降幅度还是不比数字电路设计的,尤其是在布局布线和验证上,所以自动化一直没有提上日程,现阶段大部分模拟电路设计主要还是取决于设计者本身的直觉、技能和经验。

有了AI的帮助后,EDA工具在大量数据的训练下给出了先进的机器学习算法,使得模拟电路的布局布线有了更高效的自动化流程,尤其是在约束提取和生成,布局优化上,模拟电路的优化和生成及仿真验证也可以在AI驱动下获得提速。如此一来,每个模拟电路设计的迭代数量会进一步减少,芯片的上市周期也随之缩短。

系统集成

近几年流行起来的UCIe、Chiplet、3D封装等,其实都是一个系统集成的概念。以此引入的设计与制造优化方案也受到了持续关注,比如DTCO等。如何集成更多的晶体管、更多的内存以及逻辑+内存集成,还有最后软件联合硬件的热管理等,都是系统集成需要考虑的问题。

那么AI该如何从系统集成上进行优化呢?答案就是提供一个更高效探索设计空间的路线,能够给出预测模型和更快的实现方式,例如新思的DSO.ai和Fusion Complier,就提供了完备的AI设计方案,以求实现更好的PPA和更快的设计验收。据了解,新思的这些方案最近在台积电的N3E工艺上得到了验证,为高性能计算、AI和移动设备等计算密集负载提供了增强的功耗、性能和良率。

写在最后

其实一旦芯片设计进入AI辅助的时代,也对设计工程师们提出了相应的更高要求,因为不少低级设计问题已经被AI预测、优化和生成给解决了。设计工程师们需要在更高层级的设计上实现创新,比如系统/软件联合优化等等,这样自己才不会被“优化”掉。设计工程师们的专业技能,未来也会更加趋向于数据科学家需要掌握的技能,而数据科学家们也说不定会因此获得抢设计工程师饭碗的机会。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

AI

+关注

关注

87文章

30643浏览量

268824

发布评论请先 登录

相关推荐

光伏电站运维系统解决传统光伏电站运维痛点

光伏电站运维系统解决传统光伏电站运维痛点 随着光伏电站的日益普及,光伏运维成为保障光伏电站安全、高效运行的重要手段,但是传统的运维方式面临着一系列挑战,为了应对这些挑战并提高运维效率,陕西公众

工业级路由器:解决网络传输的痛点

工业级路由器专为工业应用场景设计,具备高可靠性、稳定性和带宽,解决实时性要求高、大量数据传输、复杂网络环境等痛点,适用于制造业和能源行业,提升生产效率、产品质量和企业竞争优势。

risc-v多核芯片在AI方面的应用

RISC-V多核芯片在AI方面的应用主要体现在其低功耗、低成本、灵活可扩展以及能够更好地适应AI算法的不同需求等特点上。

首先,RISC-V适合用于高效设计实现,其内核面积更小,功耗更低,使得它能

发表于 04-28 09:20

数据采集边缘网关解决企业数据采集痛点的关键

网关 应运而生,成为解决企业数据采集痛点的关键所在。 一、企业背景与痛点分析 在当前信息化、智能化的时代背景下,许多企业面临着海量数据采集和处理的难题。这些企业通常拥有多个分散的业务场

电梯物联网技术如何解决电梯管理的痛点?

随着物联网技术的不断发展,电梯行业也迎来了新的变革。电梯物联网技术的应用为电梯管理带来了许多新的机遇和优势,同时也有效地解决了传统电梯管理中存在的各种痛点。

本文梯云物联网将探讨电梯物联网技术如何解决电梯管理的痛

5G网络通信有哪些技术痛点?光耦技术在5G网络通信的应用

5G网络通信有哪些技术痛点?光耦技术在5G网络通信的应用 5G网络通信的技术痛点: 1. 频谱资源短缺:5G通信需要更高的频谱资源来支持更大的数据传输量和更高的速度,但是目前无线通信

通过Goooood®狗帝 融合CDN解决内容传递痛点:

Goooood®狗帝 融合CDN解决了与内容传递相关的痛点,为企业提供了一个全面的解决方案,优化性能、增强安全性、扩展全球覆盖范围并实现可扩展性。借助Goooood®狗帝 融合CDN强大的功能和全球网络基础设施,企业可以无缝地传递内容,提供卓越的用户体验,并在当今竞争激烈

华芯邦:创新MEMS技术,改善电子烟痛点

传统电子烟存在许多痛点,而华芯邦的创新型MEMS技术和孔科微电子的电子烟PCBA方案妥善解决了这些问题。华芯邦的MEMS传感器集成咪头电子烟芯片具有高容错率和防粘柱功能,显著提高了口感和使用效率。

放心交给AI解决的芯片设计痛点

放心交给AI解决的芯片设计痛点

评论