创建时钟

使用SDC命令create_clock创建时钟,时钟周期20,占空比50%的时钟信号;

create_clock-nameCLK-period20[get_portsCLK]-waveform{07}

-waveform 时钟占空比,不指定该选项,则时钟默认占空比为50%

生成时钟

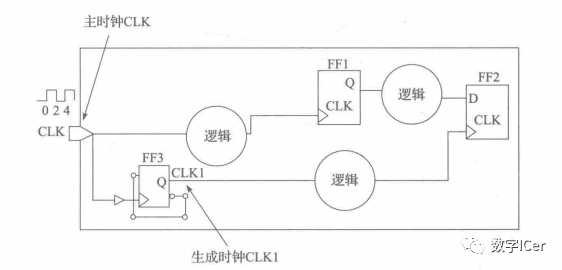

生成时钟:是基于一个主时钟并通过相关逻辑转换后,在相位,频率,占空比等方面和主时钟有一定变化的分支时钟;

生成时钟的时钟源来自主时钟,其相位参考主时钟;

生成时钟可以通过以下方式生成:

时钟分频

时钟倍频

时钟门控

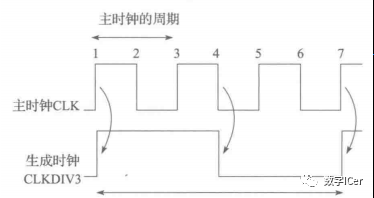

通过SDC命令 create_generated_clock 来定义生成时钟:

create_generated_clock-nameclk_gen-source[get_portsCLK][get_pins{DFF/Q}]-divide_by3

-source 设定生成时钟的源引脚

divide_by 3 :3分频

divide_by:表示生成时钟通过分频生成;

multiply_by :表示生成时钟通过倍频生成;

edges: 占空比设置

生成时钟

生成时钟

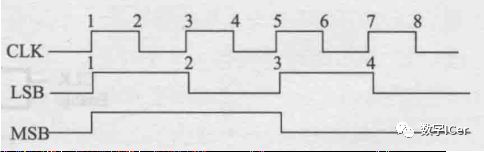

可对生成时钟占空比进行设置:

占空比进行设置

占空比进行设置

create_generated_clock-nameCLK_LSB-source[get_portsCLK][get_pins{DFF/Q}]-edges{135}

create_generated_clock-nameCLK_LSB-source[get_portsCLK][get_pins{DFF/Q}]-edges{159}

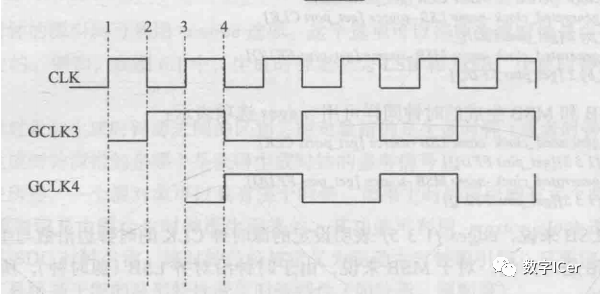

分频器由源时钟下降沿触发:

源时钟下降沿触发

源时钟下降沿触发

create_generated_clock-nameGCLK3-source[get_portsCLK][get_pins{DFF/Q}]-edges{246}

create_generated_clock-nameGCLK4-source[get_portsCLK][get_pins{DFF/Q}]-edges{468}

虚拟时钟

虚拟时钟即设计中不存在的时钟,定义虚拟时钟应满足:

设计中的某个时钟实际存在,但其时钟源不是来自设计中任何引脚和端口;

由于虚拟时钟和设计中的任何引脚和端口无直接关系,故定义虚拟时钟时并不指定时钟端口;

虚拟时钟用于作为输入输出端口延时约束的时钟源;

通过SDC命令创建虚拟时钟:

create_clock-nameVIRTUAL_CLK-period10-waveform{05}

IO端口延迟

输入延迟:在一个时钟周期内,外部逻辑的输出数据到达设计输入端口所需的时间;

输出延迟:在一个时钟周期内,设计输出端口数据到达外部逻辑所需的时间;

通过SDC命令set_input_delay在输入端口指定延迟;

set_input_delay-clockCLK1.2[get_ports{IO}]

set_input_delay-max-add_delay-clock[get_clocks{CLK}]15[get_ports{IO}] set_input_delay-min-add_delay-clock[get_clocks{CLK}]15[get_ports{IO}]

-add_delay:通知工具除了现存的约束外,这是一个额外的约束,不会覆盖前一个约束;如果没有-add_delay,那么后面的约束会覆盖前面的约束。

通过SDC命令set_output_delay在输出端口指定延迟;

set_output_delay-max-add_delay-clock[get_clocks{CLK}]15[get_ports{IO}]

set_output_delay-min-add_delay-clock[get_clocks{CLK}]15[get_ports{IO}]

负延迟:

下面值可能是负值:set_input_delay -max

set_input_delay -min

set_output_delay -max

set_output_delay -min

时钟分组

同步时钟:时钟存在固定的相位关系,来自同一个时钟源;异步时钟:不存在固定的相位关系;

为了让时序工具忽略异步时钟之间的时序路径或串扰分析,SDC提供了set_clock_groups命令,表明时钟组之间的时序路径不必考虑;

set_clock_groups-name{clk_group1}-group{GCCK}-group{RCLK}

-asynchronous:时钟彼此不共享相位关系时可使用;

例:

set_clock_groups-name{clk_group1}-group[get_clocks{CCK1CLK2CLK3}]-group[get_clocks{CCK4CLK5CLK6}]

表示:CLK1,CLK2,CLK3分别异步于CLK4,CLK5,CLK6;

伪路径

不需要做时序分析的时序路径,可以通过伪路径忽略该路径,使得工具对该路径不进行时序分析;

set_false_path-from[get_clocksCLK1]-to[get_clocksCLK2]

定义两个时钟域CLK1和CLK2之间的路径为伪路径;

set_false_path-through[get_pinsX1]-through[get_pinsX2]

定义按X1->X2的顺序通过X1 X2引脚的路径为伪路径;

-from,-to,-through指定false的路径;

-from X1 -to X2:表示从起点X1到终点X2的路径;

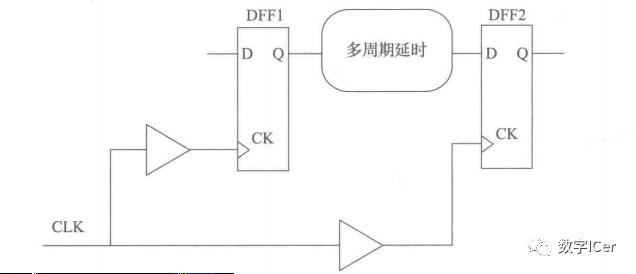

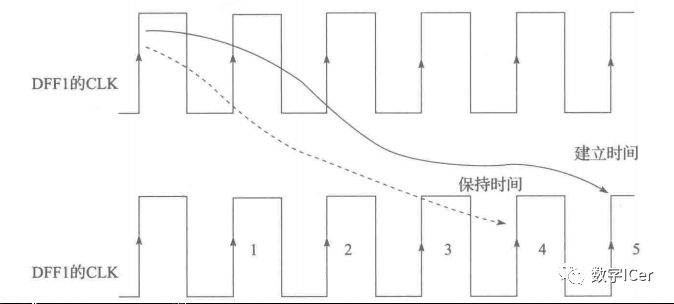

多周期路径

多周期路径,存在时序路径较长或者信号在延时等于几个时钟周期的时间,如果仍然按照单周期进行约束,可能会出现时序违例,如下图所示:

通过SDC命令set_multicycle_path:

set_multicycle_path-from[get_pinsDFF1/Q]-to[get_clocksDFF2/D]-setup5 set_multicycle_path-from[get_pinsDFF1/Q]-to[get_clocksDFF2/D]-hold4

-setup和-hold成对出现;

保持时间比建立时间少一个周期;

最大最小延迟

当需要点对点对某些路径进行约束时,可通过最大最小延迟实现;

异步电路之间

输入信号直接通过组合逻辑后输出

当约束定义的是时序路径中的节点时,则约束的仅在两个节点之间;

set_max_delay-from[get_portsA1]-to[get_portsA2]8 set_min_delay-from[get_portsA1]-to[get_portsA2]5

上述定义A1到A2之间的时序路径的约束最大延时8ns最小延时6ns;

当约束定义是时钟时,最大最小延时将应用于该时钟源所控制的所有路径;

set_max_delay-from[get_clocksCLK1]-to[get_clocksCLK2]8 set_min_delay-from[get_clocksCLK1]-to[get_clocksCLK2]5

上述定义从时钟域CLK1到CLK2之间的所有时序路径的约束最大延时为8ns,最小延时为6ns;

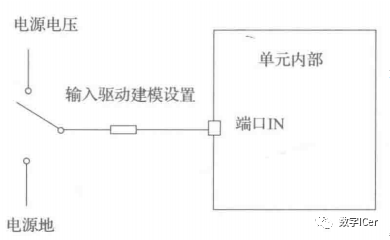

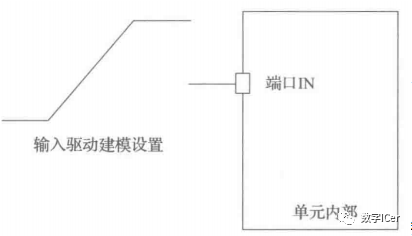

IO环境建模

输入驱动建模:默认情况下,如果没有设置外部输入驱动,时序分析工具则默认外部输入驱动为无穷大;

推荐查看:综合对象及环境属性

1.set_drive

设置外部输入驱动信息,通过该命令定义驱动该引脚的输入驱动电阻值,通过该驱动电阻值计算出驱动端的转换时间,并计入时序路径延时信息;

当定义为0时,代表输入端驱动力为无穷大;

set_drive0[get_portsCLK]

上述定义CLK输入的驱动值为无穷大;

set_drive-rise0.4[all_inputs] set_drive-fall0.3[all_inputs]

上述命令定义所有输入的驱动值,上拉驱动电阻为0.4,下拉驱动电阻为0.3;

-min指定最小电阻,用于保持时间分析;

-max指定最大电阻,用于建立时间分析;

如果不指定-max和-min,那么指定的值既用于建立时间分析,也用于保持时间分析;

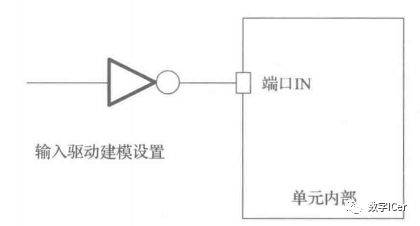

2.set_driving_cell

指定驱动单元

set_driving_cell-lib_cellINVX1M[all_inputs]

上述命令定义设计所有驱动力等价于单元库中INVX1M单元的驱动力;

-lib_cell:指定驱动引脚的单元;

3.set_input_transition

通过set_input_transition 定义驱动该引脚的输入驱动端转换时间,设置的转换时间越大驱动力越小,当定义为0时,其代表输入端驱动力无穷大;

输出负载建模:默认情况下,如果没有设置外部输出负载,时序分析工具则默认外部输出负载为0;

1.输出负载可通过SDC命令set_load,定义外部负载为一个等效电容,其电容值即为负载值(指定的是负载的实际电容值);

set_load10[all_outputs] set_load[expr[load_of$LIB_NAME/AND2X1M/A]*3][all_outputs]

上述命令定义所有输出负载等效为库中与门AND2X1M的引脚A的电容值的3倍;

负载类型:-pin_load,-wire_load可以指定负载类型是引脚负载还是线负载;

2.set_port_fanout_number value port_list

指定输出的扇出数(如果已知外部寄生负载并且已经通过set_load指定了外部寄生负载,则这个命令没有具体含义)

3.set_fanout_load value port_list

指定扇出负载(根据标准负载指定负载值)

其他时钟特性

1.时钟转换时间:

时钟在高低电平状态下切换所需要的延时;

通过SCD命令 set_clock_transition 来定义时钟转换延时;

-rise 提供时钟上升沿的转换时间;

-fall 提供时钟下降沿的转换时间;

-max和-min 设置转换时间的最大最小条件;

set_clock_transition-rise0.2[get_clocksCLK] set_clock_transition-fall-min0.2[get_clocksCLK] set_clock_transition-fall-max0.4[get_clocksCLK]

该命令仅用于预布局阶段,即时钟树综合完成之前,再时钟树生成之后,该命令不应用于任何的后布局时序分析;

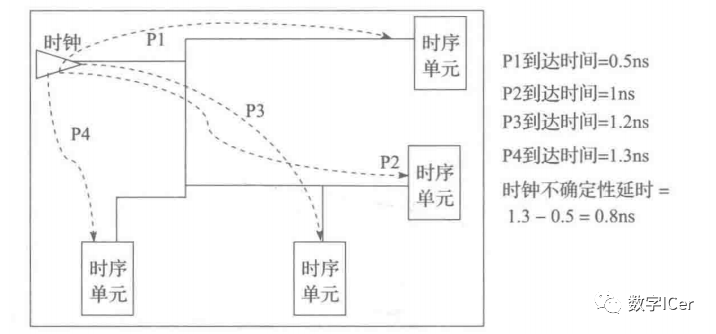

2.时钟不确定性

实际时钟本身与理想时钟存在一定的差异,比如时钟抖动,时钟偏斜等因素;

时钟偏斜:时钟到达不同触发器时间差异;

时钟抖动:时钟周期的不良偏差;

如上图,时钟到达P4时间为1.3ns,到达P3时间为1.2ns,那么不确定性延时为1.3-1.2=0.1ns;

通过SDC命令set_clock_uncertainty 可将时钟偏斜和抖动模型化;

set_clock_uncertainty0.5[get_clocksCLK1] set_clock_uncertainty-setup0.5[get_clocksCLK2] set_clock_uncertainty-hold0.2[get_clocksCLK2]

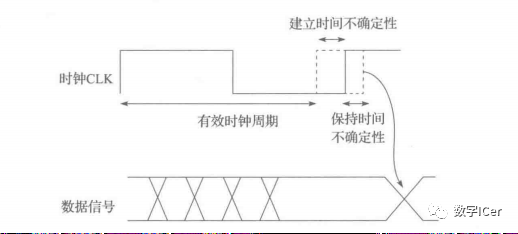

以上时钟不确定性为建立时间0.5ns,保持时间0.2ns;如下图所示:

不同时钟的不确定性

对于不同时钟不确定度建模时,源时钟可用-form,目的时钟可用-to;

#C1到C2的建立时间和保持时间不确定度 set_clock_uncertainty-fromC1toC2-setup0.5 set_clock_uncertainty-fromC1toC2-hold0.5 #C1上升沿到C2下降沿的不确定度 set_clock_uncertainty-rise_fromC1fall_toC20.5 #C1和C2之间的不确定度 set_clock_uncertainty-fromC1toC20.5 set_clock_uncertainty-fromC2toC10.5

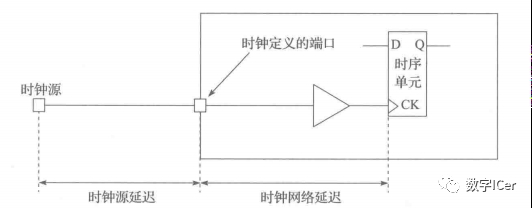

3.时钟延迟

时钟信号从时钟源输出端到达时序单元时钟输入端(如触发器)所需要的时间,称为时钟延迟;

时钟延迟包括源延迟和网络延迟,源延迟是指源时钟到达时钟定义的端口的延迟;

网路延迟是指时钟定义的端口到时序单元时钟输入端的延迟;

通过SDC命令set_clock_latency来定义时钟延迟信息:

-source 设定源延迟:

set_clock_latency-source0.5[get_clocksC1]

set_clock_latency-source-early0.5[get_clocksC1] set_clock_latency-source-late1.0[get_clocksC1]

最长路径的延迟可用-late,最短路径的延迟可用-early。

或者:

set_clock_latency-source-min0.5[get_clocksC1] set_clock_latency-source-max1.0[get_clocksC1]

当未设定-source时,表示网路延迟;

#上下降沿网路延迟 set_clock_latency0.5-rise[get_clocksC1] set_clock_latency0.3-fall[get_clocksC1]

时钟网路延迟和时钟源延迟区别:

时钟网络延迟是时钟树生成前的设置,当实际时钟树生成后,时钟网络延迟将通过set_propagated_clock被时钟树的实际结果所替代;而时钟源延迟则会一直存在。

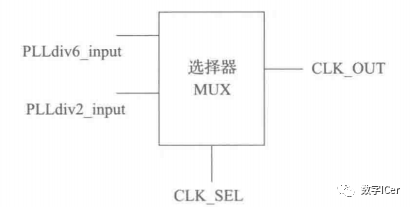

模式分析

恒定状态约束:

根据设计中不同模式的需要,通过设置恒定状态约束来定义时钟选择端口的对应状态值,

在多个模式中选择的时候,设定指定单一模式(相当于mux选择器);

通过SDC命令set_case_analysis定义恒定状态约束;

如上图,假如CLK_SEL为0时,选择PLLdiv6_input,CLK_SEL为1时,选择PLLdiv2_input,则可设

set_case_analysis0[get_pins{mux.CLK_SEL}]

上述定义模式端口mux.CLK_SEL恒定状态为0;

可以是0,1,rising,falling

其他SDC命令

指定工作条件和要执行分析类型:

set_operaing_conditions-maxss_1v62_125c-libraryss_1v62_125c

指定相应工作条件的库(根据PVT温度,电压,工艺决定)

线负载模型:

set_wire_load_model-namesmic18_wl10-libraryss_1v62_125c

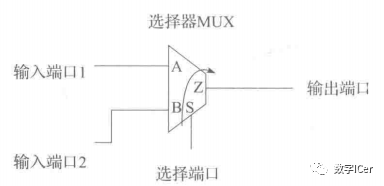

屏蔽时序弧:

set_disable_timing-fromS-toZ[get_cellsMUX]

上述命令屏蔽选择器单元MUX中从S端到Z端的时序弧;

最大转换时间:

set_max_transition0.8[all_outputs]

上述命令定义所有输出驱动最大转换时间为0.8ns;

最大电容负载:

set_max_capacitance0.6[all_outputs]

上述命令定义所有输出驱动最大电容负载为0.6pF;

最大扇出:

set_max_fanout15[all_outputs]

上述命令定义所有输出驱动最大扇出为15;

附:SDC命令

SDC约束分为:

时序约束

面积与功率约束

设计规则约束

接口约束

特定模式和配置约束

设计要求的异常

其他命令

时序约束

命令包括指定时钟特性,端口延迟,引脚和路径命令;

create_clock

create_generated_clock

set_clock_groups

set_clock_uncertainty

set_clock_latency

set_clock_transition

set_input_delay

set_output_delay

set_propagated_clock

set_clock_gating_check

set_ideal_latency

set_ideal_network

set_ideal_transition

set_max_time_borrow

set_resistance

set_time_derate

set_data_check

group_path

set_load

set_drive

set_input_transiton

set_fanout_load

面积与功率约束

set_max_area

create_valtage_area

set_level_shifter_threshold

set_level_shifter_strategy

set_max_dynamic_power

set_max_leakage_power

设计规则约束

set_max_transition

set_max_capacitance

set_min_capacitance

set_max_fanout

接口约束

set_load

set_drive

set_driving_cell

set_fanout_load

set_port_fanout_numberset_input_transitionset_input_delay

set_output_delay

特定模式和配置约束

set_case_analysis

set_logic_dc

set_logic_zero

set_logic_one

时序例外

set_false_path

set_multicycle_path

set_max_delay

set_min_delay

set_disable_timing

其他命令

set_wire_load_model

set_wire_load_mode

set_wire_load_selection_group

set_wire_load_min_block_size

set_units

set_operating_condition

sdc_version

SDC查询命令

get_cells

get_ports

get_pins

get_nets

get_clocks

all_inputs

all_output

all_registers

all_clocks

get_libs

get_lib_cells

get_lib_pins

current_design

审核编辑:刘清

-

时序分析

+关注

关注

2文章

127浏览量

22647 -

SDC

+关注

关注

0文章

49浏览量

15629 -

时钟源

+关注

关注

0文章

94浏览量

16077

原文标题:SDC约束

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

VIVADO时序约束及STA基础

ETD第14期:SDR源同步接口时序约束方法

如何将Altera的SDC约束转换为Xilinx XDC约束

调用timequest工具对工程时序进行分析

时序约束的步骤分析

时序分析基本概念—SDC概述

时序分析的设计约束(SDC)

时序分析的设计约束(SDC)

评论