这两年由于疫情,太过于动荡,包括我们的FPGA,也由于市场、供应链、以及某些人的短期趋利问题,价格简直上了天。

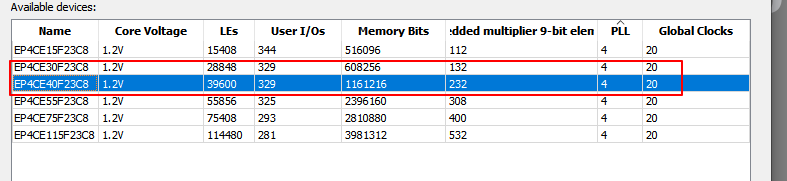

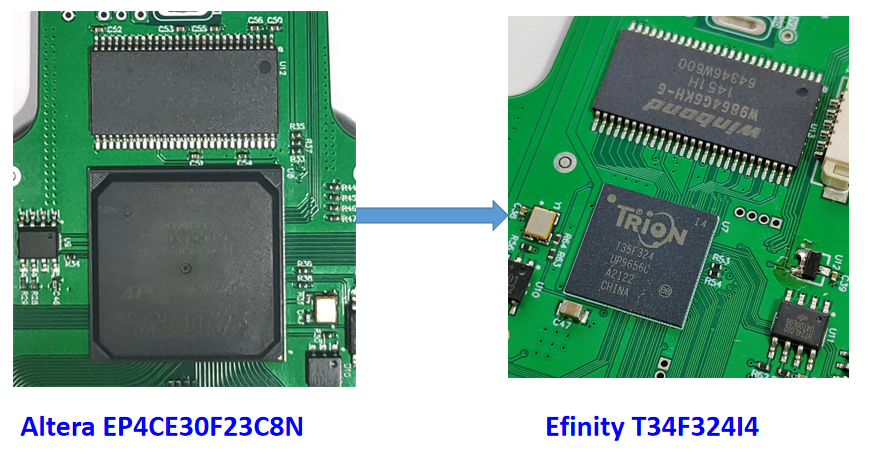

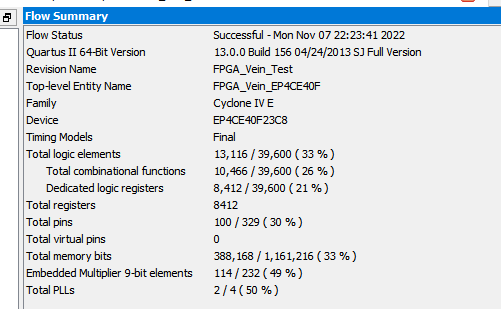

过去一个设计用了Altera的EP4CE30F23C8N,这款芯片几乎是Altera性价比最高的芯片,并且他和EP4CE40F是同一个Die,因此熟悉门路的人知道,可以直接将EP4CE30F价格采购的芯片,当作EP4CE40F来用,瞬间资源倍增,如下图所示,LE直接增加1/3,Memory和乘法器几乎翻倍:

可惜是曾经可以用60-80RMB的零售价买到的EP4CE30F FPGA,由于这两年的动荡,以及供应链的转移,10倍的价格也只能买到翻新的料了。或许Altera也可能已经放弃了中低端Cyclone IV系列FPGA,或者更多的将产能放到了高端Stratix FPGA上了。

那么我们就难了,原有的产品不能因此断片,全新的EP4CE30几乎需要几千才能买得到,进退两难,只能另谋出路,上帝给你关闭一扇门的同时,很有可能还会给你开另一扇门。

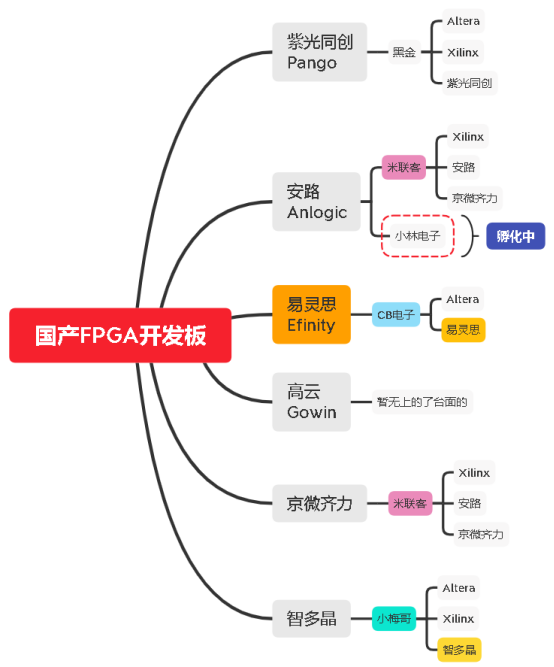

之前我写过一篇公众号,时隔10年,我将重新杀回国产FPGA,其中我列举了当前国产FPGA的市场格局,如下图所示:

我在这些选项中寻找寻找可以替代EP4CE30F的FPGA,希望这款FPGA可以满足以下要求:

逻辑资源在30K左右

引脚在256-484之间

有丰富的Memory资源

可以运行在200MHz左右的频率

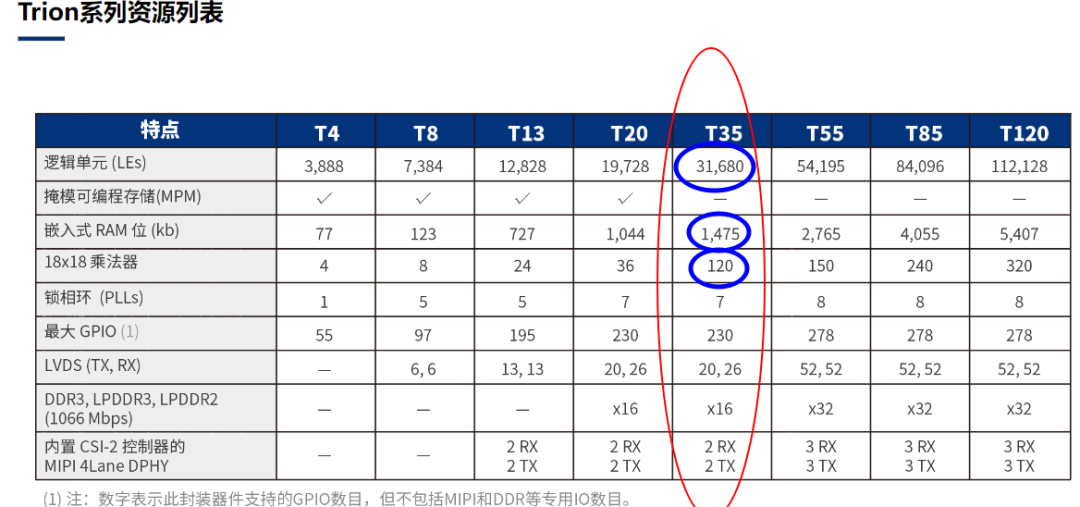

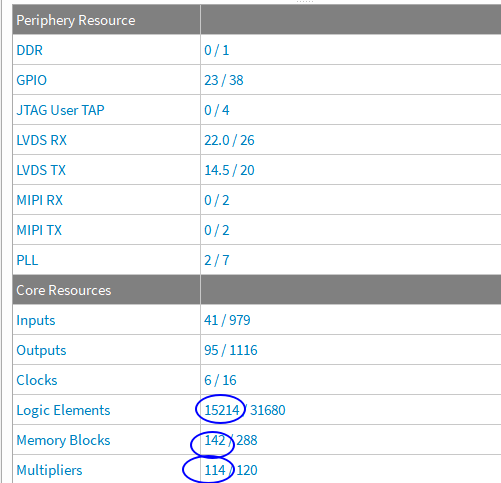

纵观思维导图,我找不到可以同时满足以上5个要求,同时价格还可以和EP4CE30F不相上下的FPGA。直到有一天,Eric给我推荐了易灵思。易灵思有Trion和钛金两个系列,相比工艺Trion系列和Cyclone IV更贴近,同时第一次观摩T35(35K LE)的内部资源,瞬间让我找到了北,太满足替代EP4CE30F的需求了,其资源如下。

尤其是乘法器的数量,在同等规格的国产FPGA中,我几乎找不到能做到这么慷慨的,这给需要做一点图像运算的我笑出了声。

一直拖着,一直拖着,直到有一天,我确实被Altera的货源逼疯了,最终不得已,我下手将EP4CE30F给成了T35F324,即便是降低性能我不能让设计承受50倍物料的成本,为此不惜代价。也感谢自己放弃了很久,最终还是坚持到了曙光,虽然这一路上的坎坷,真的不堪入目。

(一)软件使用的艰难

这应该是使用国产FPGA,尤其是使用易灵思FPGA的同仁的心声。细数目前国产FPGA的软件开发环境,只有类Quartus和不类Quartus两种,前者以紫光、安路为代表,换个环境根本不需要什么手册教程;后者就是易灵思的Efinity,思路清奇,别具一格,用FAE的话说是:没有他们的指导很难摸透(所以之前写过一篇文章:骨骼清奇的易灵思FPGA-小试牛刀驱动LVDS屏)。

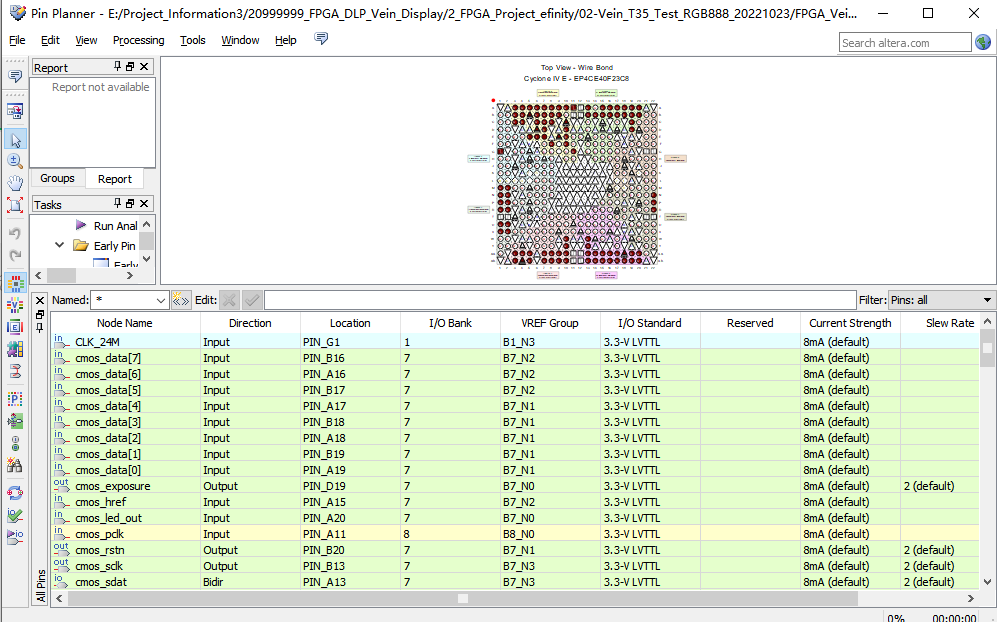

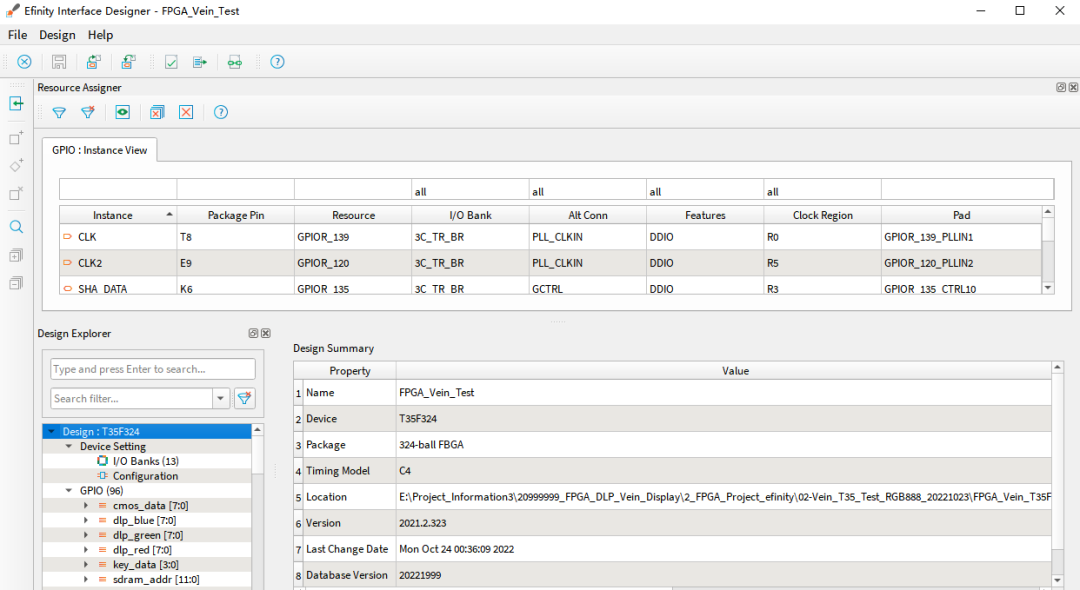

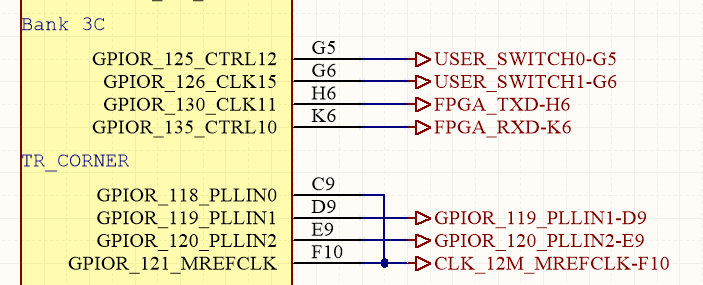

这过程确实浪费了不少的时间,包括Interface是纯硬件的设计,到Design的物理连接是分离的,所以原先Altera的设计不能直接移植。同时RAM ROM使用LUT描述再映射RAM的方式,确实和之前直接用IP Core非常不一样。这里以引脚分配为例,截图为证:

(二)软件综合和PR的坑

由于原本在设计中,采用ShiftRAM生成了41*41的窗口进行后续的图像处理,因此简单粗暴的有1681*8个寄存器,用于计算。但一模一样的设计,在易灵思的Efinity中半天都无法综合出结果,更别说PR,百思不得其解,最后只能花费巨大的精力,将按窗口的存储修改成按照列的存储模式,但是代价是需要复杂的逻辑以及主频。下图分别是Quartus与EfinityPR后的资源报表:

因此,这里不得不说国产FPGA的EDA工具链的重要性。在IC行业,EDA工具是被Synopsys、Cadence、Mentor三大家垄断的,国产EDA目前还只是萌芽阶段,这方面少说还有几十年的差距。

FPGA行业也亦是如此,Quartus II的软件是做的宇宙最好的,那是真的好用;Xilinx的Vivado是做的很强大甚至一个软件30多G,强大到一时半会儿还学不会。国产FPGA的软件,那简直做的是一塌糊涂,到底是PR优先,还是时序有限,或者其综合、PR算法,那真的不敢恭维,个人认为还是有很长的路要走。

不过易灵思的Efinity软件,相对其他某几家,做得还是不错的。

(三)硬件设计的约束

这方面真的太难了,如果没有FAE的支持,处处是坑。如果有FAE这根避雷针,很多时候可以避免掉坑里,毕竟爬出来还要很久。比如:

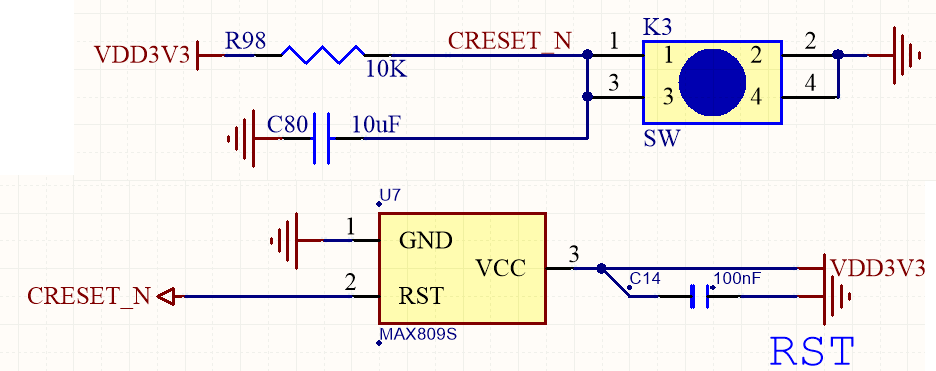

1)CRESET必须有上拉电阻+下拉电容,或者加一个复位芯片,否则无法正常启动工作

2)硬件设计的时候,有些GCLK输入的时钟可以去PLL,而有些GCLK输入的时钟只能直接使用。

那么问题来了,如果全局只有从PLL GCLK输入的时钟,如果我想先延时一段时间在释放PLL的复位,那么就得用PLL之前输入的时钟,但是Efinity从PLL输入的时钟,不允许用户直接拿来用,似乎是PLL专用的。。。所以这就很尴尬,强行使用,采用Efinify 2021编译直接报错,采用2022编译会给出Warming,但流程可以继续往下走,这就很尴尬了。

个人目前对Efinify的GCLK网络结构还是有一点懵圈,不知道只有bug呢,还是有特别的妙招,反正现在使用受限。

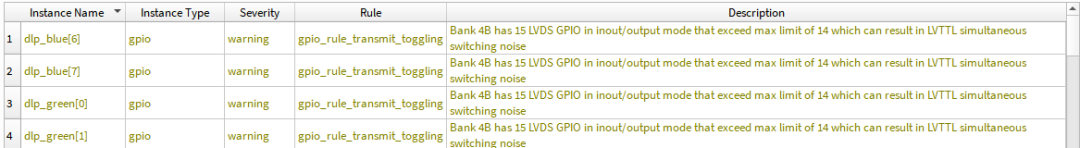

3)一个BANK并不是所有IO都可用的,但用了也不会咋地,FAE又据说速度慢一点可以,但有时也真是有一些异常,官方有明确的答案吗?

然后我现在确实有遇到一些神奇的问题,比如某一个一定时序启动的设备,有概率性时间起不来,不知道是不是IO用多了的问题。

面积与功耗的优势!!

但不得不说易灵思的FPGA,0.65mm的球间距,12*12mm的封装尺寸,还有当前设计没有用上的DDR硬核和MIPI CSI控制器,简直是图像领域FPGA设计的福音。

还有非常关键的一点,我们都知道Altera FPGA功耗比Xilinx FPGA的功耗做的好很多,但与易灵思FPGA相比;同等规模+同样设计的Altera的功耗,还是做的略逊了一点。如下所示,同样的系统+同样的设计(后来用了同一套代码),分别测试Altera与易灵思T35方案,实际的5V下电流,如下所示:

从原先的6.4W,到采用易灵思T35后降低到3.8W,几乎降低了40%的功耗。并且这还是整机的功耗,如果单纯评估FPGA的功耗,估计降了100%以上(系统中还有一个吃电的DLP光机)

至此,最近几个月的易灵思FPGA项目实战的坎坷精力,已经给大家汇报完毕,期间也是一把鼻涕一把泪,换方案想着简单,做起来还是挺麻烦的。此处感谢易灵思T35,可以把物料成本上天的方案降低到合理水平,得以让此继续。也真心祝愿各位采用国产FPGA做替代的朋友,早点让自己的设计安顿下来,找到一条可以走得更远的路。

审核编辑 :李倩

-

FPGA

+关注

关注

1629文章

21736浏览量

603227 -

供应链

+关注

关注

3文章

1674浏览量

38888 -

易灵思

+关注

关注

5文章

47浏览量

4862

原文标题:易灵思FPGA做替代,到底有多难?

文章出处:【微信号:疯狂的FPGA,微信公众号:疯狂的FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

差分输入和和单端输入在本质上到底有什么区别?

易灵思FPGA产品的主要特点

lm2902做的二阶低通滤波器,无论怎么调试C1的值,电路的波特图都保持不变,请问一下C1的作用到底有多大?

易灵思RAM使用--Update5

国产FPGA应用专题--易灵思Efinity软件使用心得

易灵思RAM使用--Update4

易灵思FPGA做替代,到底有多难?

易灵思FPGA做替代,到底有多难?

评论