本篇博文旨在演示如何通过 NoC 从 Versal 应用处理单元 (APU) 访问 AXI BRAM。

设计示例是使用 Vivado 2020.2 版本创建的,评估板使用的是 VCK190 评估板。

Versal

Versal 架构将“Scalar Engine”(标量引擎)、“Adaptable Engine”(自适应引擎)和“Intelligent Engine”(智能引擎)这三种不同类型的引擎与丰富的连接和通信功能以及片上网络 (NoC) 有机结合,从而支持实现覆盖整个器件的无缝式存储器映射访问。

智能引擎包括:

SIMD VLIW AI 引擎,适用于自适应推断和高级信号处理计算

DSP 引擎,适用于定点运算、浮点运算和复杂的 MAC 运算。

自适应引擎将可编程逻辑块与存储器有机结合,它具备专为应对高计算密度需求而设计的架构。

标量引擎包括 Arm Cortex-A72 和 Cortex-R5 处理器,支持计算密集型任务。

片上网络 (NoC)

片上网络 (NoC) 是一个 AXI 互连网络,用于在可编程逻辑 (PL)、处理器系统 (PS) 和其它硬核块中的 IP 端点之间共享数据。

此基础架构覆盖整个器件,基于专有的切换开关形成高速集成的数据路径。

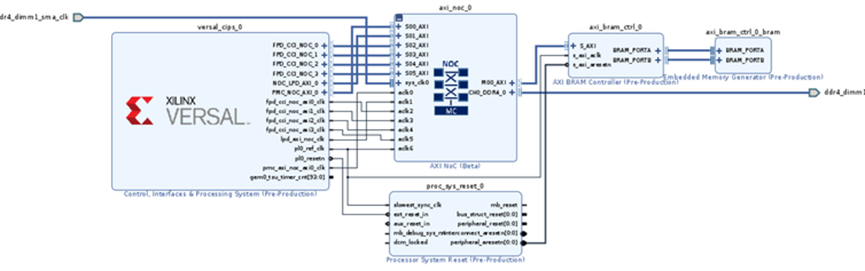

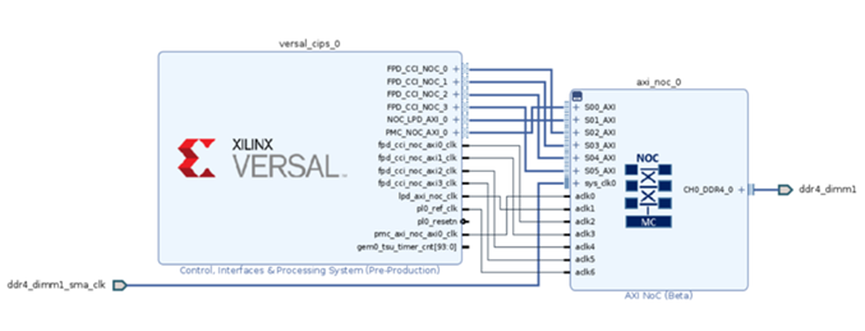

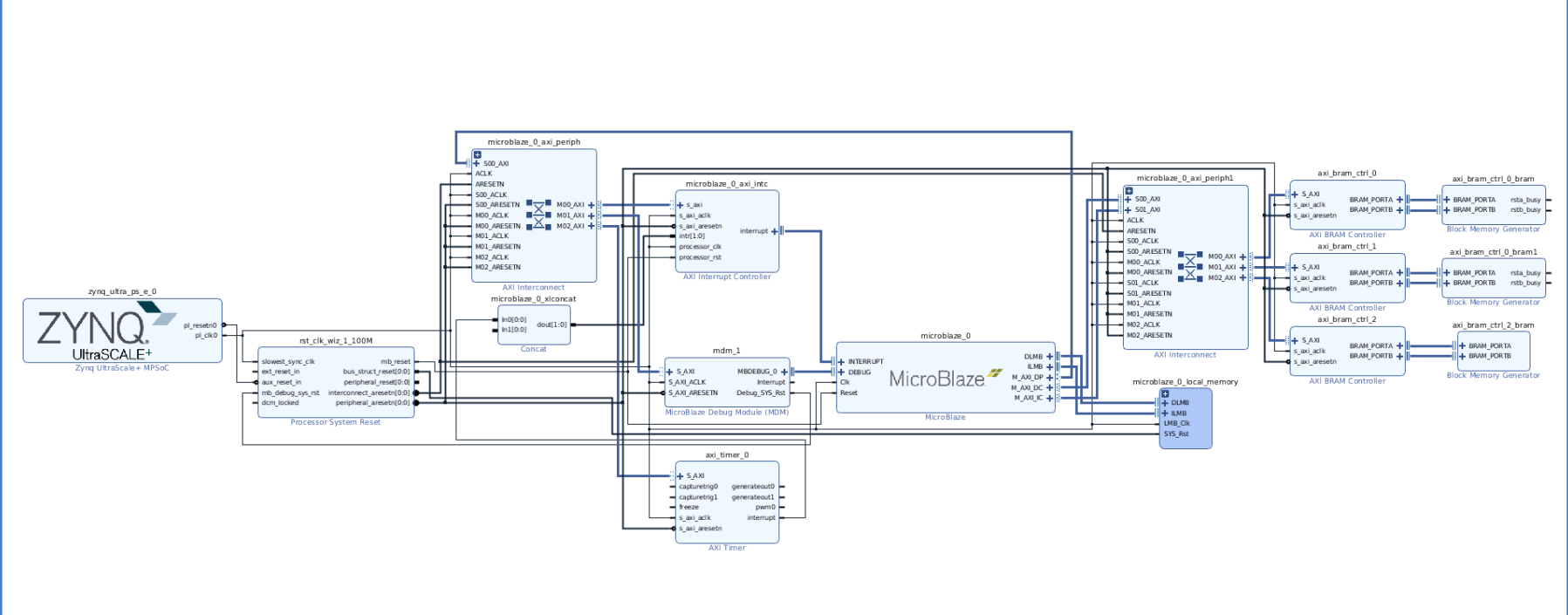

模块框图

Vivado 步骤

步骤 1:

以 VCK190 评估板为目标创建工程,并在 IP integrator 内创建块设计。

步骤 2:

添加 versal_cips IP (Control, Interfaces and Processing System),并运行块自动化设置。在设置中配置 NoC 的存储器控制器 (DDR4),并将 PL 时钟和 PL 复位的数量配置为 1。

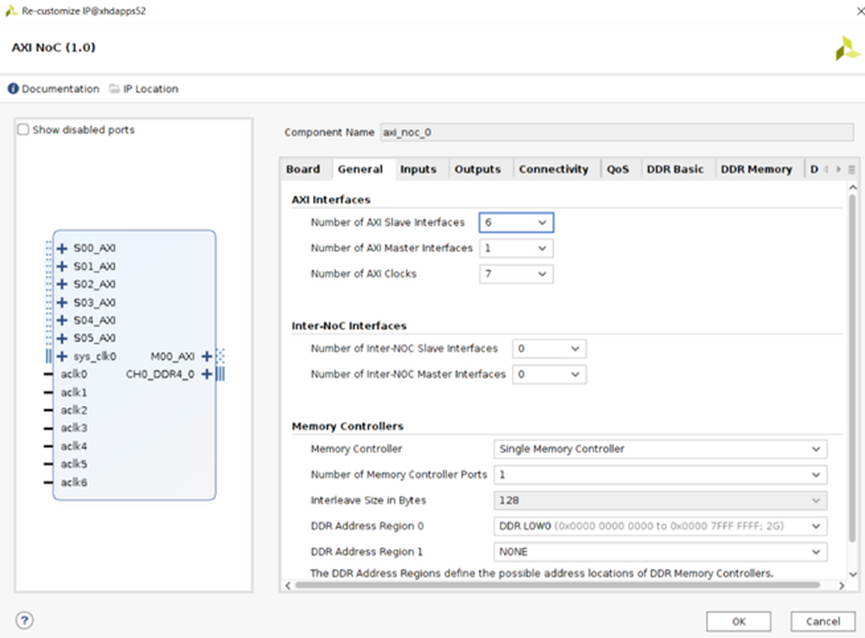

步骤 3:

双击打开 NoC IP,在“General”(常规)选项卡中进行以下设置:

Number of AXI Master Interfaces(AXI 主接口数)= 1

Number of AXI Clocks(AXI 时钟数)= 7

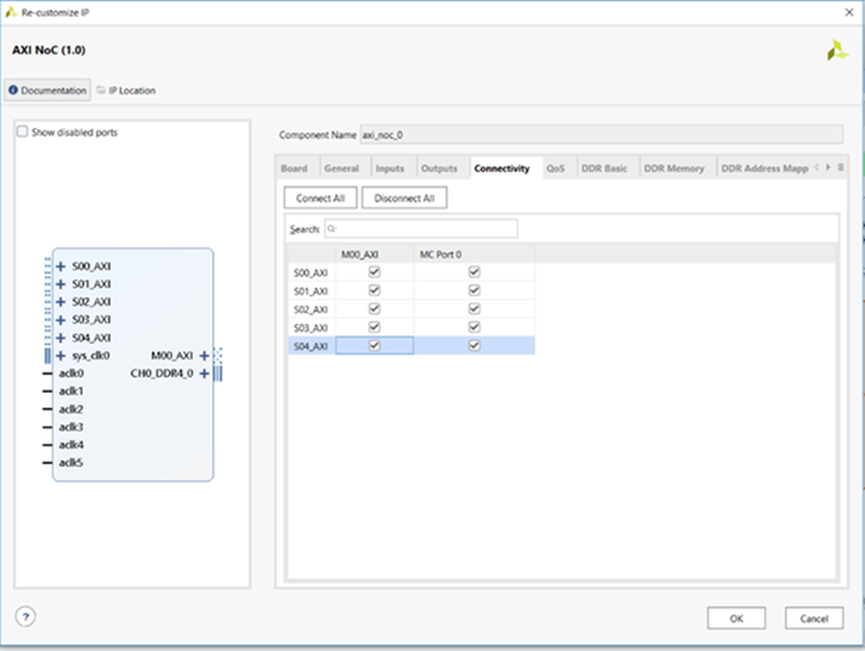

步骤 4:

转至“Connectivity”(连接)选项卡,检查 S0xAXI 与 M00_AXI 之间的连接,然后单击“OK”(确定)。

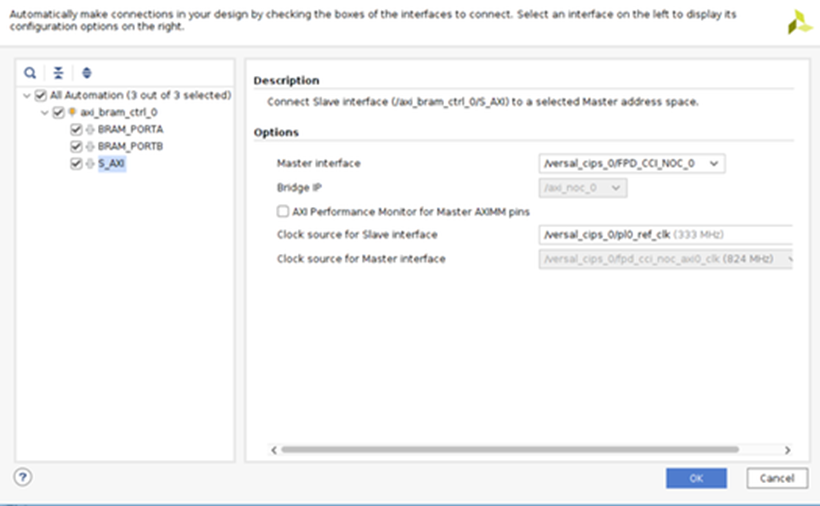

步骤 5:

将 AXI BRAM 添加到块设计中,单击“Run Connection Automation”(运行自动连接),然后选中 pl_clk0 作为从接口的时钟源。

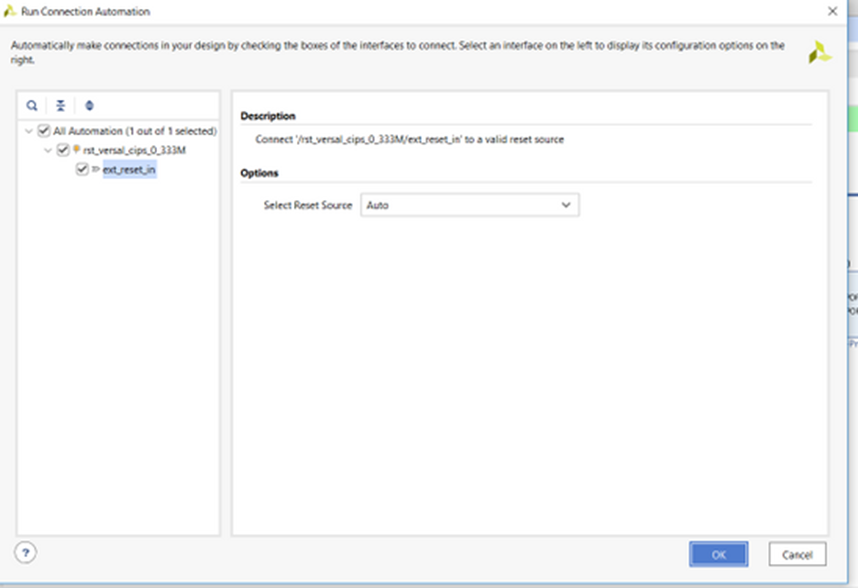

步骤 6:

再次运行“Run Connection Automation”,配置 ext_reset_in接口。

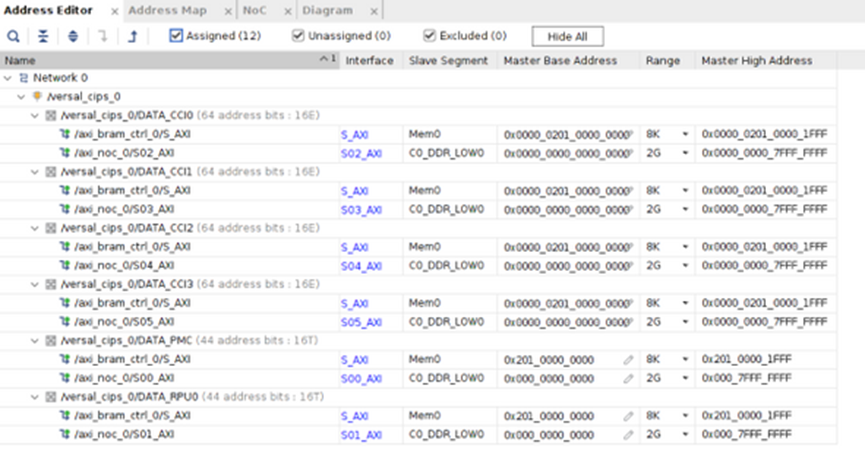

步骤 7:

运行“validation”(确认)步骤,确认成功后,检查“Address Editor”(地址编辑器)选项卡。

步骤 8:

为 BD 创建顶层文件,运行综合与实现,然后生成器件镜像。

步骤 9:

导出硬件设计以获取 XSA 文件。

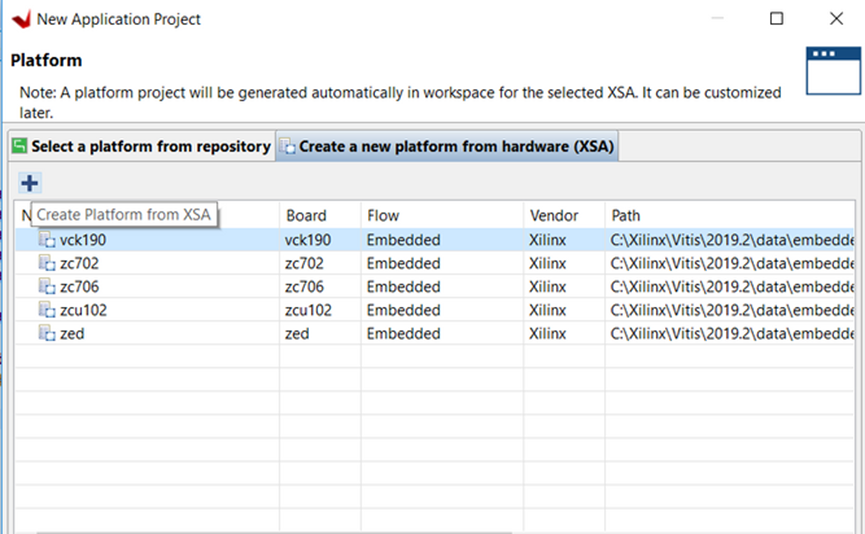

Vitis 步骤

步骤 1:

在 Vitis 中创建新的应用工程,然后切换至“Create a new platform from hardware”(基于硬件创建新平台)选项卡。

单击“+”,选择从 Vivado 导出的 XSA 文件。

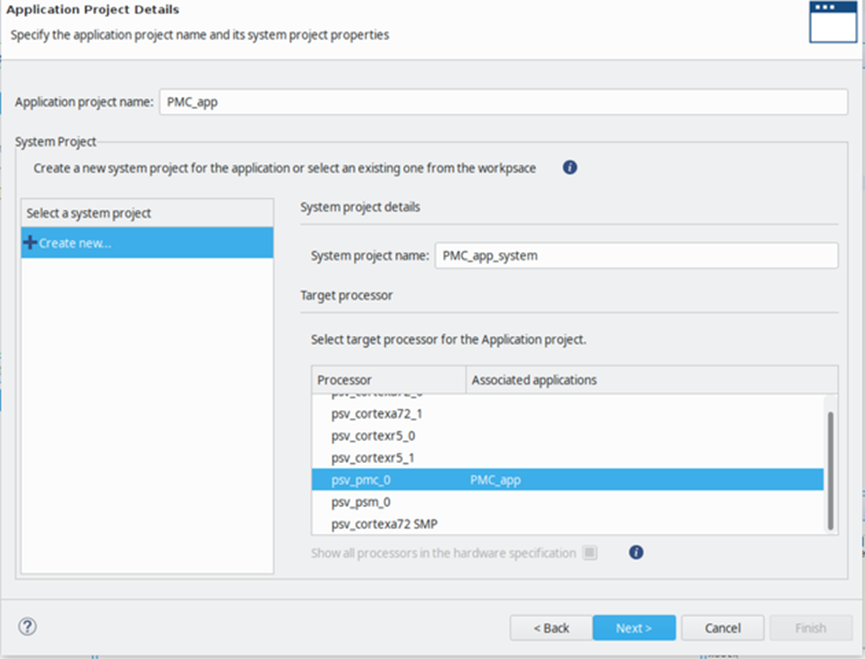

步骤 2:

提供工程名称,并选择处理器。

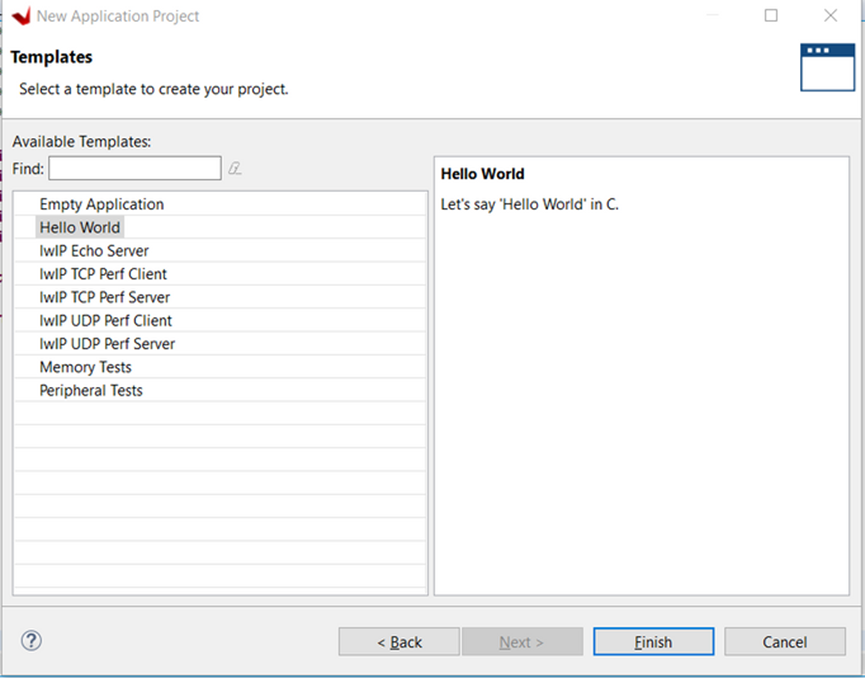

步骤 3:

选择 Hello World 模板,然后单击“Finish”(完成)。

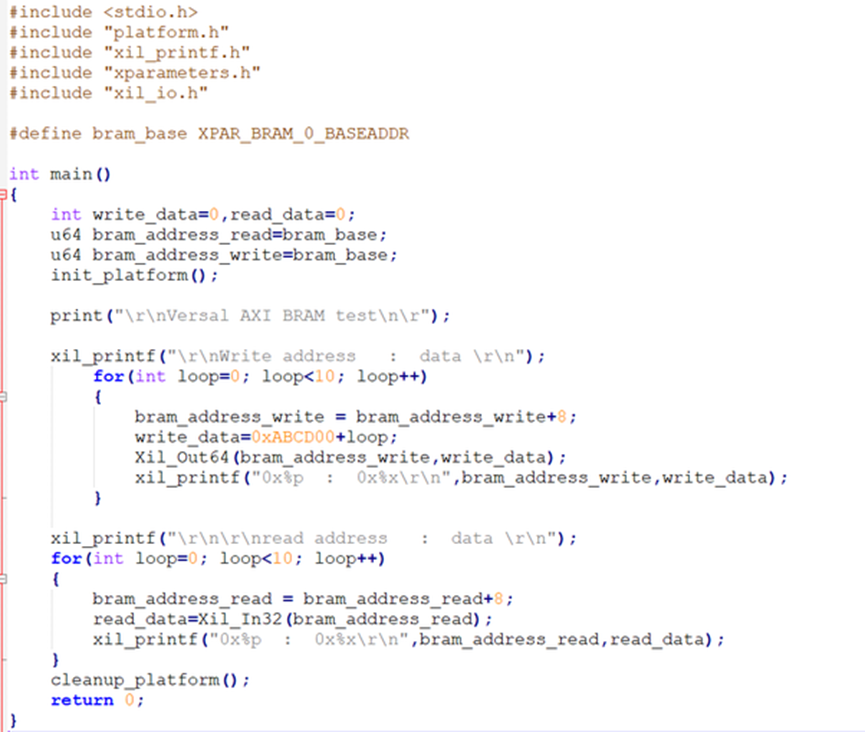

代码修改

创建完应用工程后,在 main.c 中修改代码对 AXI BRAM进行读写。

Xil_Out64 函数用于将数据写入 64 位地址,而Xil_In32 函数则用于地址中读取 32 位数据。

示例:

写入数据 API

Xil_Out64(bram_address_write,write_data);

读取数据 API

read_data=Xil_In32(bram_address_read);

代码快照:

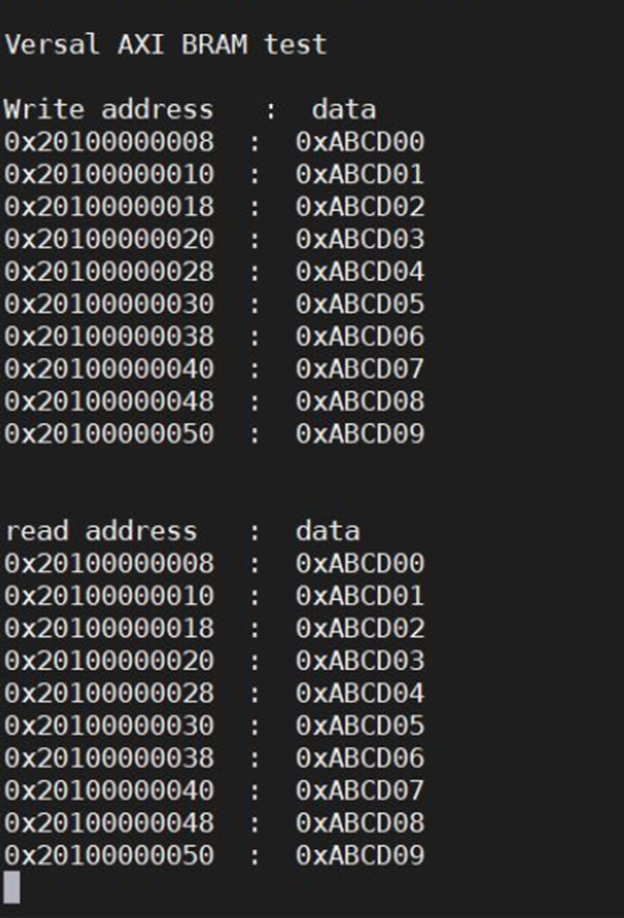

运行设计

连接到VCK190 评估板,并设置启动模式为 JTAG 启动模式,然后运行应用。

控制台输出示例:

审核编辑:汤梓红

-

NoC

+关注

关注

0文章

38浏览量

11734 -

AXI

+关注

关注

1文章

127浏览量

16625 -

Versal

+关注

关注

1文章

158浏览量

7658

原文标题:开发者分享|在 Versal 中通过 NoC 从 PS-APU 对 AXI BRAM 执行基本读写操作

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【FPGA ZYNQ Ultrascale+ MPSOC教程】33.BRAM实现PS与PL交互

怎么使用AXI CDMA从OCM/DDR写入BRAM

请问如何通过MicroBlaze访问BRAM?

【正点原子FPGA连载】第十四章基于BRAM的PS和PL的数据交互领航者 ZYNQ 之嵌入式开发指南

利用NoC资源解决FPGA内部数据交换的瓶颈

如何利用NoC资源去支撑FPGA中的创新设计

ZYNQ的ARM和FPGA数据交互——AXI交互最重要的细节

如何通过NoC 从 Versal应用处理单元访问AXI BRAM

如何通过NoC从Versal应用处理单元(APU)访问AXI BRAM

FPGA系列之“Zynq MPSoC PS-PL AXI Interfaces”

如何通过NoC从Versal™应用处理单元(APU)访问AXI BRAM呢?

Versal CPM AXI Bridge模式的地址转换

在Versal中通过NoC从PS-APU对AXI BRAM执行基本读写操作

在Versal中通过NoC从PS-APU对AXI BRAM执行基本读写操作

评论