作者:RICK HEARN,RICH JAENICKE

虽然多核处理器为安全关键型航空电子设备的设计人员提供了更小尺寸、更低功耗和更高性能的显著优势,但事实证明,将这些优势带到安全关键型系统中具有挑战性。这主要是由于验证和认证多核软件和硬件架构的复杂性。主要关注的是在一个内核上运行的应用程序如何干扰在另一个内核上运行的应用程序,从而对确定性、服务质量以及最终的安全性产生负面影响。

正在努力简化多核处理器的安全关键型实施。已经更新了几个标准来解决多核问题。

其中包括ARINC 653,它涵盖了安全关键航空电子应用的实时操作系统(RTOS)的空间和时间分区。ARINC 653 于 2015 年更新(ARINC 653 第 1 部分补充 4),以解决单个应用程序的多核操作,称为“分区”。开放组的未来机载能力环境 (FACE) 技术标准版本 3.0 通过要求遵守补充协议 4 来解决多核支持问题。此外,由 FAA、EASA、TCCA 和其他航空当局支持的认证机构软件团队 (CAST) 发布了一份立场文件,其中包含名为 CAST-32A 的多核系统指南。这些文档共同提供了成功将多核解决方案用于可认证高达 DAL A 的应用程序的要求,DAL A 是安全关键型软件的最高 RTCA/DO-178C 设计保证级别。

多核的优势

多核架构的好处很多,而且引人注目:

更高的吞吐量:在多个内核上运行的多线程应用程序可扩展吞吐量。多个单线程应用程序可以通过每个应用程序同时在自己的核心中运行来更快地运行。最佳核心利用率使吞吐量能够随核心数线性扩展。

更好的 SWaP [尺寸、重量和功耗]:应用程序可以在单个多核处理器中的单独内核上运行,而不是在单独的单核处理器上运行。对于机载系统,较低的SWaP可降低成本并延长飞行时间。

未来增长空间:多核处理器的更高性能支持未来的需求和应用。

更长的供应可用性:大多数单核芯片已经过时或接近过时。多核芯片在其供电寿命开始时提供处理器。

安全关键型应用中多核面临的挑战

在单核处理器中,通过在托管应用程序之间对内存空间和处理器时间进行可靠分区,多个安全关键型应用程序可以在同一处理器上执行。内存空间分区将内存的非重叠部分专用于在给定时间运行的每个应用程序,由处理器的内存管理单元 (MMU) 强制执行。时间分区将固定时间间隔(称为主帧)划分为一系列固定子间隔(称为分区时间窗口)。为每个应用程序分配一个或多个分区时间窗口,窗口的长度和数量是应用程序最坏情况执行时间 (WCET) 和所需重复率的因素。操作系统 (OS) 确保每个应用程序在其分配的时间内都可以访问处理器的核心。将这些安全关键技术应用于多核处理器需要克服几个复杂的挑战,最困难的是内核之间通过共享资源进行干扰。

磁芯之间的干扰

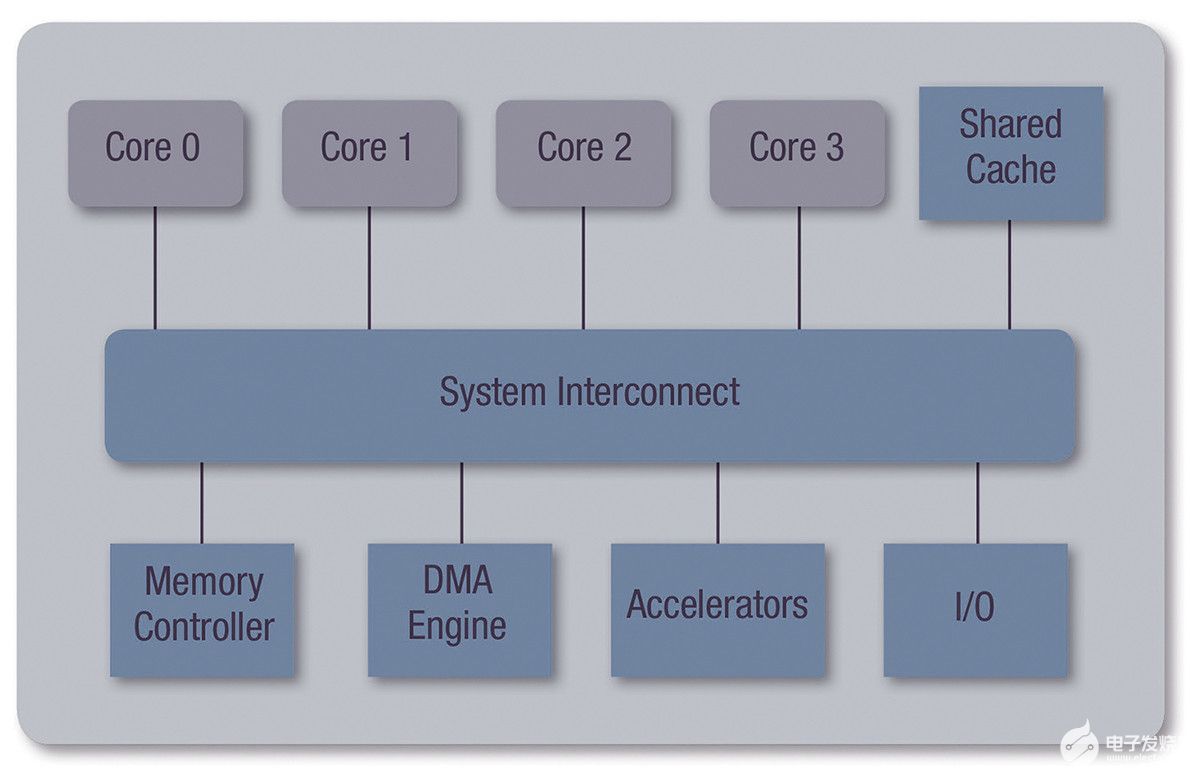

在多核环境中,每个处理核心的专用资源有限。所有多核硬件架构还包括共享资源,例如内存控制器、DDR 内存、I/O、缓存以及连接它们的内部结构(图 1)。当多个内核尝试同时访问同一资源时,会导致争用。这种情况意味着较低关键性的应用程序/分区可能会阻止较高关键性的应用程序/分区执行其预期功能。在四核系统中,内核仅通过互连访问 DDR 内存(即没有 I/O 访问),来自多个内核的多个干扰源显示 WCET 增加了 12 倍以上。由于DDR控制器中的共享资源仲裁和调度算法无法保证公平性,干扰影响通常是非线性的。事实上,测试表明,单个干扰核心可以将另一个核心上的WCET增加8倍。

图1:单独的处理器内核(灰色)共享许多资源(绿色),范围从互连到内存和 I/O。

CAST-32A 为解决多核处理器中的干扰问题提供了认证指导。一种方法是基于对每个应用程序/分区的 WCET 测试和分析及其对共享资源的最坏情况利用率创建一个特殊用例。但是,特殊用例解决方案可能会导致供应商锁定和重新验证整个系统,并更改任何一个应用程序/分区,从而使这种方法成为集成模块化航空电子设备(IMA)系统实施和维护的重大障碍。如果没有操作系统机制和工具来支持减轻干扰,维持成本和风险非常高。对任何一个申请的更改都需要对所有综合申请进行完整的WCET重新验证活动。

更好的方法是让操作系统根据解决 CAST-32A 目标的 DAL A 运行时机制、库和工具的可用性有效地管理干扰。这为系统集成商提供了有效、灵活和敏捷的解决方案。它还简化了新应用程序的添加,而无需对系统架构进行重大更改,减少了重新验证活动,并有助于消除 OEM 供应商锁定。

将单核软件设计移植到多核

虽然将现有安全系统移植到多核平台可提供更多计算资源,但由于访问共享资源的延迟较长或来自其他内核的干扰,给定应用程序的 WCET 可能会增加。需要新的分析来确定其他资源(如内存、内存控制器和内核间通信)是否会成为新的瓶颈。虽然资源可能运行得更快,但相对性能的变化可能会导致应用程序停止工作或以不确定的方式运行。

有效利用多核资源

为了实现多核解决方案的吞吐量和 SWaP 优势,软件架构需要支持可用处理器内核的高利用率。必须支持所有多核功能,从启用内核的并发操作(相对于可用内核在启动时被迫进入空闲状态或保持重置状态)到提供确定性负载平衡机制。软件多处理架构越灵活,系统架构师实现高利用率的工具就越多。

软件多处理架构

与多处理器系统一样,多核处理器上的软件体系结构可以根据访问来自其他处理器或内核的内存的方式以及每个处理器或内核是否运行自己的操作系统副本进行分类。对于基于多核的系统,最简单的软件架构是非对称多处理 (AMP),其中每个内核独立运行,每个内核都有自己的操作系统或虚拟机管理程序之上的来宾操作系统。每个内核运行不同的应用程序,在调度方面内核之间很少或根本没有有意义的协调。由于缺乏负载均衡、难以缓解共享资源争用以及无法跨内核执行协调活动(如全面内置测试所需的活动),这种解耦可能会导致利用率不足。

现代替代方案是对称多处理 (SMP),其中单个操作系统控制所有资源,包括哪些应用程序线程在哪些内核上运行。这种架构易于编程,因为所有内核都“对称”访问资源,从而使操作系统能够将任何线程分配给任何内核。

不知道哪些线程将在哪些内核上运行是一个重大挑战,也是关键系统中确定性操作的风险。为了解决这个问题,CAST-32A引用了绑定多处理(BMP)的使用。BMP 是一种增强且受限的 SMP 形式,它将应用程序的任务静态绑定到特定内核,使系统架构师能够严格控制多个内核的并发操作。BMP 直接遵循 ARINC 653 补充 4 第 2.2.1 节中的多核要求,其中指出:“计划在不同处理器内核上同时执行的分区内的多个进程。

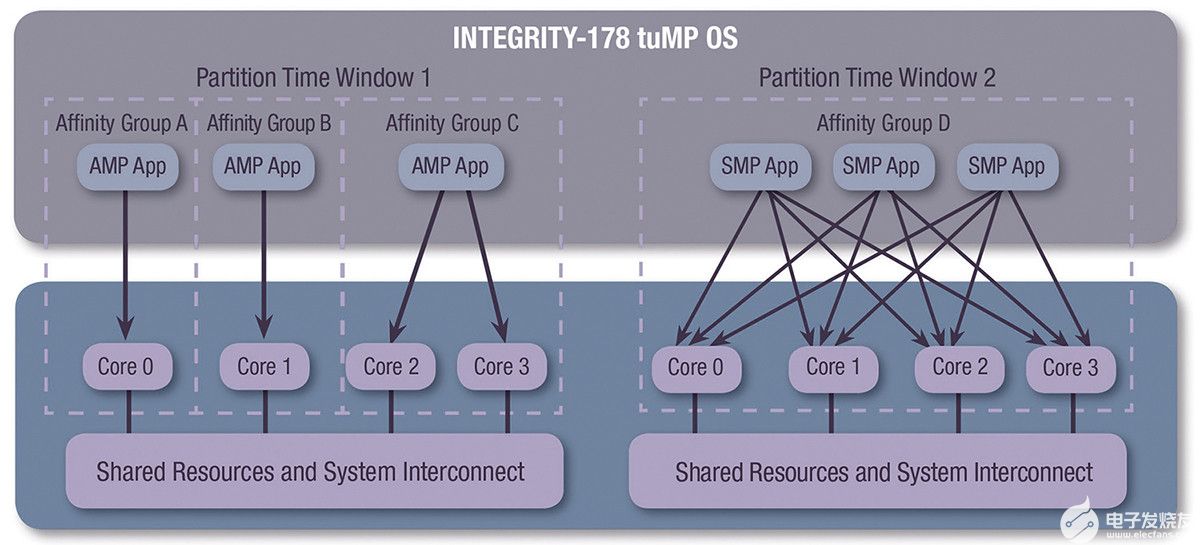

用于安全认证的多核实时操作系统的一个例子是Green Hill的INTEGRITY-178 tuMP,它是一个统一的多核RTOS,支持AMP,SMP和BMP的同时组合。RTOS 的时变统一多处理 (tuMP) 方法为将安全关键型和安全关键型应用移植、扩展和优化到多核架构提供了灵活性。它从跨所有内核运行的时间分区内核开始,该内核允许将 AMP、SMP 和 BMP 应用程序的任意组合绑定到称为关联组的一个或多个内核组(图 2)。

图2:INTEGRITY-178 TuMP 的时变功能支持将应用程序与不同分区时间窗口的核心进行不同的绑定。

然后,它会添加时间差异,以便分区时间窗口不需要在内核之间对齐。INTEGRITY-178 tuMP还包括带宽分配和监控(BAM)功能,根据DO-178C DAL A目标开发。BAM 旨在使系统集成商能够识别和减轻基于多核的系统的干扰,直接解决 CAST-32A 指南并降低集成和认证风险。

硬件角度:DO-254 可认证的多核硬件

除了DO-178软件外,飞机的全面安全认证还需要硬件的DO-254认证。当前和新兴的航空航天需求要求硬件处理能力能够支持具有混合安全关键级别的多种功能和应用。这些要求,以及包括多核处理器在内的密集计算需求和架构,突出了对能够防止性能下降和共享资源争用的RTOS技术的非常明确和迫切的需求。

包含多核处理技术的硬件体系结构必须专门设计为设置活动内核的数量和执行频率,指定激活哪些 MCP 外设,并确定对共享内存和缓存的硬件支持。在安全关键型应用中,必须仔细选择多核处理器,并根据几个关键因素构建其主机板,包括处理器的服务历史、制造可用性和质量数据、I/O 功能、性能水平和功耗。

Curtiss-Wright 基于 NXP QorIQ T2080 电源架构处理器的 VPX3-152 是专为支持安全关键型多核应用而设计的单板计算机 (SBC) 的一个示例。四核 T2080 以相对较低的功耗水平满足许多 DAL A 应用的性能要求。T2080 的 16 个可用 SerDes 通道有效地将可从处理器直接提供服务的功能数量增加了一倍,从而简化了整体电路板设计和认证工作。

这些多核处理器的全部功能在与RTOS相辅相成时得以实现,RTOS使系统设计人员和集成商能够以高保证的方式利用处理器内核的所有可用计算能力。使用安全关键型多核 SBC 和提供确定性、用户定义内核和调度分配的 RTOS 可以确保完全实现多核硬件的性能功能。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

20332浏览量

254914 -

操作系统

+关注

关注

37文章

7437浏览量

129616 -

RTOS

+关注

关注

25文章

869浏览量

123212

发布评论请先 登录

BlackBerry QNX与NVIDIA深化合作:重构安全关键型边缘AI系统的技术范式

Altair OptiStruct:重构结构研发逻辑,引领工业仿真与优化新纪元

米尔RK3506核心板SDK重磅升级,解锁三核A7实时控制新架构

基于CW32 MCU的I2C接口优化稳定读写EEPROM关键技术

针对AES算法的安全防护设计

如何对蜂鸟e203内核乘除法器进行优化

在TR组件优化与存算一体架构中构建技术话语权

ADI建议电源开发优先考虑电源架构的优化

QNX QOS 8.0助力构建复杂任务关键型嵌入式应用

树莓派更新:确保系统安全且优化的关键步骤!

知识分享 | 评估模型架构——如何实现?

CAN XL安全实践:深度防御下的密钥协商优化

针对安全关键型应用优化多核架构

针对安全关键型应用优化多核架构

评论