近日,有消息称,由于“3nm制程的N3工艺某预定大客户”临时取消订单,台积电因而大砍供应链订单,涉及再生晶圆、关键耗材、设备等供应链领域。但台积电并不承认,而是回应称:N3制程进度并无改变,预期2023年将平稳量产。

不管这个砍单的大客户是不是苹果,不管手机市场不景气是否给台积电的多位大客户们带来压力——即使台积电3nm制程的进度未受拖累,但其产能大概率也将无法再现7nm、5nm时代的辉煌。台积电原定年底3nm初步量产后,月产能能到4.4万片,但目前预计年底产能仅能维持1万片左右。

而2022年11月相继发布的联发科天玑9200和高通骁龙8G2两款旗舰处理器,采用的都是台积电4nm工艺,并没有使用3nm工艺。而台积电4nm工艺本质上是台积电发布于2020年的5nm工艺节点改进版改名而已,这一幕其实在台积电6nm工艺时就发生过,6nm本质上也是7nm工艺节点的改进。

悄悄改名字的小心机背后,是晶体管微缩技术发展的放缓。这也让人们好奇,摩尔定律要止步于1nm了吗?在“后摩尔时代”,Chiplet(芯粒)这种不受限于晶体管制程、而是将各种技术进行异质整合的先进封装技术开始大放异彩,又能否助力中国芯片产业破除或者缓解“卡脖子”难题?

Chiplet技术源起

Chiplet技术所依托的异构设计思路很早就有,戈登·摩尔早在1964年提出“摩尔定律”的同时就预测了摩尔定律“终结”之后的小芯片异构互联思路,他指出:届时用多个独立封装的小功能单元互连构建大型系统的方法可能会更经济。

但Chiplet量产时间较晚,也就最近几年才在半导体行业流行开。海思2014年采用台积电16nm FinFET工艺的网络芯片CoWoS,就是海思第一片公开的Chiplet设计。此后海思设计的晟腾910 等芯片也采用了Chiplet设计。

而Marvell公司创始人周秀文博士在2015年的国际固态电路峰会(ISSCC) 上,则提出了模块化芯片(MOChi TM)概念:采用 DRAM 存储器、CPU、GPU 计算元件、LTE Modem、WiFi、南桥等“模块化”裸芯片,通过异构封装堆叠成手机、电脑的处理器。

2017年,美国国防高级研究计划局(DARPA)在名为 CHIPS(Common Heterogeneous Integration and IP Reuse Strategies)的项目中,邀请英特尔、美光、新思科技以及波音、洛克希德等公司参与研发一种可以替代SoC的模块化裸芯方案,也即Chiplet。Chiplet以“搭积木”的方法,采用先进封装堆叠连接成“多芯粒模组”(MCM),从过去芯片的组装变为基于芯粒的异构集成。

就以手机SoC芯片为例,其CPU、GPU、基带等不同部件在制造上往往要选择相同的工艺节点,因为在单硅片系统只能在一个工艺节点上实现。然而不同部件的工艺需求不同,比如逻辑芯片更青睐先进制程,而模拟芯片如果采用先进制程可能会导致漏电、噪声等问题。

但以往设计SoC时,芯片设计企业从不同的 IP 供应商购买IP,再结合自研NPU等模块,统一都使用先进制程集成为一个SoC,这不仅徒增成本,也会导致性能上的可能隐患。

而Chiplet模式则可以自由选择不同裸芯片的工艺,然后通过先进封装来进行组装。那么对于某些IP,厂家既可以购买之后自己设计、流片,也可以买其他企业实现好的硅片然后在一个封装里集成起来。总之,相比以往相同工艺节点的SoC芯片制造,Chiplet模式更具灵活性。

尽管英特尔、AMD等X86芯片巨头都在下注研发Chiplet技术,但将Chiplet发扬光大的,还是AMD。

2017年,AMD推出了其第一代Epyc服务器处理器Naples重返数据中心市场,基于Zen架构核心,最高32核心/64超线程,32核产品采用多芯片模块(multi-chip module,MCM)架构,由4个晶片(die)构成,每个晶片包括 8 个核心及其他部件。MCM架构可谓是Chiplet的前代,但仍有着核心数扩展不易、I/O 器件占比过高等缺点。

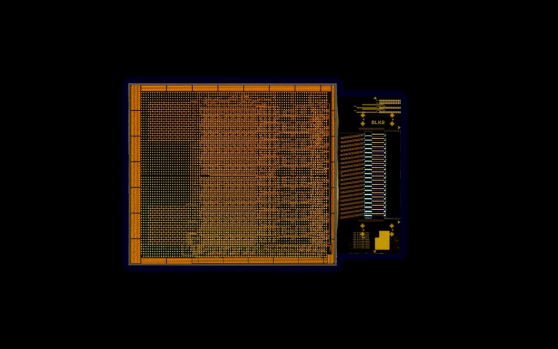

2019年AMD又推出了第二代EPYC处理器Rome,基于Zen2架构核心,第一次采用了Chiplet设计。也就是把DDR内存控制器、Infinity Fabric 和 PCIe 控制器等 I/O 器件集中到一个单独的晶片里,即I/O Die(IOD),采用成熟的14nm制程;两边布置多达8个 CCD(Core Complex Die,核心复合晶片),CCD 内部的核心、Cache 等所占面积高达 86%,可以从7nm 制程中获得较大的收益。

从第一代的4晶片结构,到第二代的9晶片结构,Chiplet技术功不可没。

到2021年推出第三代EPYC处理器时,经过三代产品的接力,AMD仅用五年时间,其CPU在服务器市场上的份额就从2017年底的0.8%,回升到2021第四季度的10.7%。

而且,服务器市场AMD新品迭发,份额还在迅速增长。基于Zen4架构的下一代EPYC霄龙数据中心处理器“Genoa”(热那亚)就官宣11月11日发布,最多96核心192线程。而英特尔受制于Intel 7工艺的拖累,原定去年就发布的下一代60核心至强处理器Sapphire Rapids量产时间一拖再拖,延迟到了2023年上半年。集邦咨询预计,AMD 2022年底在x86服务器市场上的份额有望上涨到15%,2023年第四季度甚至可能会超过22%。

AMD资深副总裁、产品技术架构师Sam Naffziger就曾在ISSCC 2021峰会上解释了AMD重用Chiplet技术的主因,一方面自然是晶圆工艺节点进展缓慢,另一方面则是较小尺寸裸晶具有更高的良率。

通过Chiplet技术,处理器核心可以最先进的工艺节点,而内存和 I/O 控制器功能则可以使用上一代甚至更早的工艺节点,从而在性能和成本之间取得平衡。AMD也就是借助Chiplet疯狂堆核心,在和英特尔的多年恶斗中少有地占领了一时上风。

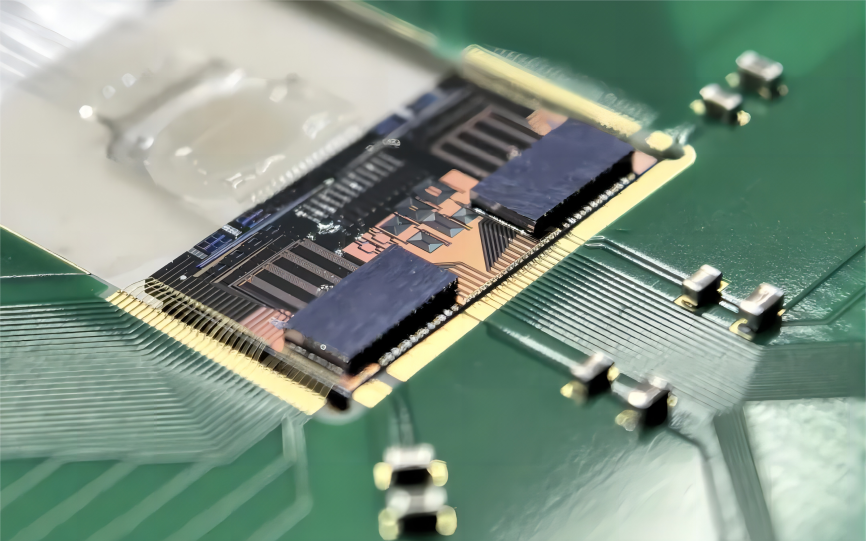

苹果等企业同样重视Chiplet。2022年3月,苹果自研的M1 Ultra,具有 1140 亿个晶体管,成为 Apple 迄今为止最大的硅芯片。而这种芯片尺寸,超出了光刻掩模版尺寸,也自然只能通过Chiplet技术进行系统级封装(System on Package,SoP)——M1 Ultra正是由两枚 M1 Max 晶粒通过UltraFusion 封装架构内部互连而成。

Chiplet与中国封测产业

在芯片设计、晶圆制造和芯片封测三大芯片上下游产业链中,中国最弱的是晶圆制造环节,而在芯片设计、芯片封测领域,则距离第一梯队其实差距并不大。

“幸运”的是,Chiplet技术从半导体产业链分工上,属于先进封装技术。要实现 Chiplet这种高灵活度、高性能、低成本的IP 重用模式,首先就要具备先进的芯片集成封装技术。

而中国封测产业一大批企业还是具有技术先进性的。长电科技、通富微电、华天科技、晶方科技、伟测、利扬、华润微电子封装测试事业群等封测厂商均有着不俗实力。2021年长电科技市占率位居全球第三,通富微电、华天科技也分别位列全球第五、六名。

也因此,很多人都对借助先进封测技术,来缓解晶圆代工上先进制程的卡脖子之难抱有期待。

华为2021年年报发布会上,华为轮值董事长郭平就表示,用面积换性能,用堆叠换性能,使得不那么先进的工艺也能持续让华为在未来的产品里面,能够具有竞争力。这也被很多人解读为,华为在Chiplet技术上在着手准备。

随着行业进入后摩尔时代,Chiplet等技术也确实带来更多想象力。

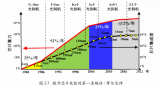

浙江大学微纳电子学院院长吴汉明就指出,从制造成本上来看,28nm以前的工艺制造成本下降速度较快,但28nm之后制造成本下降趋缓;能性能上看,2002年以前芯片每年可以提升52%,2002年到2014年,每年提升降为12%,而2014年之后,性能每年仅能提升3.5%左右。

英特尔被网友戏称为“牙膏厂”,也正是因为2014年之后酷睿一直在14nm工艺节点止步不前、每代酷睿IPC提升大都是个位百分数。

为了在后摩尔时代实现芯片算力的持续增长,吴汉明提出了三条突破途径:三维异质集成晶圆级集成、存算一体范式、可重构计算架构。实际上,上述三种技术路径,都与Chiplet技术有着千丝万缕的关系。

长电科技CEO郑力在2021年的一场演讲中就指出,后道成品制造在产业链中的地位愈发重要,有望成为集成电路产业新的制高点,如先进封装就可能成为后摩尔时代的重要颠覆性技术之一。

清华大学教授魏少军也指出,虽然封测业看似仍以加工为主要特点,一度被认为技术含量不高,但未来,以三维混合键合技术为代表的微纳系统集成有可能改变整个产业格局,前道后道工序相结合,甚至在前道工艺当中嵌入后道,后道当中集成前道,将成为一种大的趋势,这给封测业、设计业、制造业提出了全新的挑战。

这也意味着,封装产业中先进封装的占比将会越来越高。调研机构 Yole预计,2021年先进封装的市场规模约为350亿美元,占全部封装(约777亿美元)的比例约为45%;2025年占比将增长到49.4%,将成为全球封装市场的主要增量。

先进封装比例的提高,也意味着封装、测试产业整体占集成电路产业的份额也会提高。中国半导体行业协会统计数据显示,2021年中国集成电路产业销售额为10458.3亿元。其中设计业、制造业、封测业的占比为43.2%:30.4%:26.4%。而世界集成电路产业三业结构合理占比(设计:晶圆:封测)为3:4:3,随着Chiplet技术在封测行业中的更多应用,也许中国封测产业的占比将在短期内就达到、超过30%。

异构集成能否助力弯道超车

Chiplet技术作为一种异构集成的封装方案,在摩尔定律接近极限之时,被很多人寄予厚望:既然先进制程被卡脖子,那么能否借助Chiplet等新技术,使用国产化程度更高的成熟制程实现高算力来破除卡脖子难题?

思考这个问题之前,其实可以思考另一个问题:AMD从被英特尔按在地上摩擦,到有反身之力,靠的更多是Chiplet技术,还是台积电的先进制程?

2017年,AMD借助Zen架构的锐龙处理器再次回到舞台,但是第一代Zen架构虽然优秀,并未给到英特尔压力。第一代Zen微架构的处理器主要都是在格罗方德位于美国纽约州的Fab 8厂制造,制程工艺14nm LPP。但格罗方德的14nm工艺并不足以与当时英特尔改进数代的14nm工艺相比,AMD不得不在2017年又以1亿美元的代价修订与格罗方德的合同,不再排除让三星、台积电代工制造的可能。

实际上,正是在台积电7nm先进制程下的加持下,Zen3架构的芯片性能才真正超过英特尔。甚至于Zen3用一代处理器扛住了英特尔基本同时期的三代酷睿(10代、11代、12代):完全碾压10代、大幅超越11代、甚至与12代还能互有胜负,直到英特尔13代酷睿才大幅领先Zen3架构。

而近日,AMD正式发布了新一代旗舰GPU RX 7000系列,采用RDNA3内核GPU。苏姿丰特别强调说,RDNA3是全球第一款“Chiplet”游戏GPU,将一组有不同特定功能的独立芯片裸片分别制造,然后封装集成在一起,从而实现更具弹性的设计、更高良率和更低成本

此前AMD凭借制程工艺的优势,在芯片频率、能效比方面较英伟达同代产品具有一定技术优势,但市场竞争中依然不敌英伟达。但英伟达RTX40系列显卡也将从三星换用台积电4nm,英伟达在补齐了能效比方面的短板后,失去先进制程优势的AMD要用什么对抗拥有垄断地位的英伟达?

怪不得苏姿丰拿Chiplet技术作为AMD最新GPU的一个亮点去介绍了。但GPU岌岌可危,CPU同样不容乐观,英特尔13代酷睿对比AMD的Zen4架构又拉开了不少差距,Zen3时代借助台积电先进制程优势带来的“AMD,YES”,恐怕难以再现。

显然,Chiplet技术帮助AMD雪中送炭,但却没有帮助AMD进一步锦上添花,以对抗用更多小核心耍花招的英特尔。

但Chiplet技术,对于亟需突破先进制程封锁的中国半导体产业而言,却不能雪中送炭,而是可以帮助中国芯片设计企业、晶圆代工企业在异构集成技术上有一定积累之后的锦上添花。这一点恰好与Chiplet技术在AMD上的效果相反。

在核心的处理上,对次级晶圆屏蔽部分核心区分于高端芯片,是常见的做法,不过一般都会保持对称的偶数核心。但AMD更加大胆,再将没有达到要求的核心屏蔽掉,就有了原生四核架构的双核、甚至“三脚猫”三核CPU,如Phenom II X3和X2系列处理器。

既然能够屏蔽核心,也同样可以用Chiplet形式增加核心。或许AMD对于Chiplet技术的热衷,就与其从屏蔽核心时代走来有关。毕竟在屏蔽核心上,AMD比英特尔玩出过更多花样。

先进制程的重要性,是Chiplet技术难以弯道超车的。哪怕Chiplet技术允许先进制程和成熟制程异构连接,但也需要不同核心中性能取向部分采用先进制程。如果都采用成熟制程“搭积木”,尽管可以取得部分成效,但也难以替代先进制程。

业内专家莫大康也指出,从国际上Chiplet技术较为领先的企业来看,Chiplet技术并目前非由封装企业来主导,而是由Fabless企业主导,外加代工产业的大力支持。这是由于Chiplet技术涉及很多不同的产业,例如,涉及如何分割、分割后的联结、RDL技术、重新布线等。

对于中国半导体产业而言,由于封装技术往往是由封装企业来主导,因此,Chiplet等先进技术仅由封装厂来操作就有一定的困难,缺乏国际上Fabless企业、晶圆代工企业互相配合积累的“know-how”,预计还需要较长时间磨合。

不过,半导体产业有着“需求产生-供不应求-价格上涨-扩充产能-产能过剩-价格下跌-重新洗牌”的周期规律。我们也并不会把弯道超车的念想放在一项Chiplet技术上。在行业周期下行之时,更多半导体企业只要找准新技术风口,抓住重新洗牌的机会,未尝不能超车。

-

芯片

+关注

关注

455文章

50699浏览量

423064 -

3nm

+关注

关注

3文章

231浏览量

13981 -

芯粒

+关注

关注

0文章

59浏览量

128

发布评论请先 登录

相关推荐

谷景科普解决电感量允许值过大或者过小问题的方法

知存科技邀您相约第二届集成芯片和芯粒大会

Imec牵头启动汽车芯粒计划

强势入局芯粒技术链 东方晶源PanSys产品重磅发布

“苹果智能”将错过iOS 18首发

高压输电线路导线弧垂在线监测装置 绝缘子风偏角实时监测 弧垂过大或过小智能预警

国信光电子创新中心发布首款2Tb/s硅光互连芯粒

荷兰AI芯片设计公司Axelera计划推出新型汽车芯粒AI架构

什么是锂电池的内阻?锂电池内阻过大或过小对电池有什么影响?

奇异摩尔以互联解决方案,共建可持续、开放的芯粒生态

错过大芯片,可不能再错过小芯粒了

错过大芯片,可不能再错过小芯粒了

评论