为了应对对集成电路(IC)破坏的日益担忧,纽约大学(NYU)的网络安全研究人员正在开发可以监控自身计算并标记缺陷的IC。

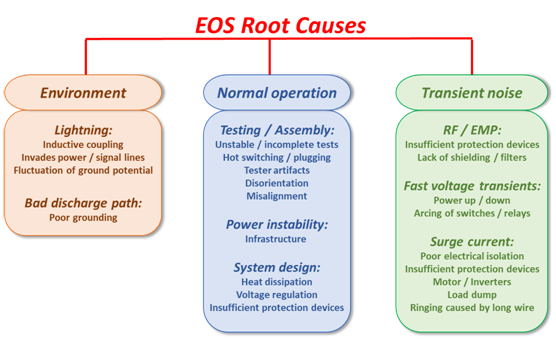

五角大楼的微电子制造供应链已经走向全球——它不再是严格意义上的美国制造商的领域。这种微芯片设计和制造的外包增加了秘密安装恶意电路的几率。

过去,外部供应商访问IC蓝图或电路的机会相对较少,但外包为欺诈者和恶意行为者提供了更多的篡改芯片的访问点。秘密插入硬件中的“后门”可以使攻击者在特定时间更改或秘密接管设备或系统。

为了战胜“坏人”和越来越多的破坏活动,纽约大学坦登工程学院电气和计算机工程助理教授Siddharth Garg和其他网络安全研究人员正在努力开发一种“可验证的计算”方法,旨在密切关注芯片的性能并发现恶意软件的迹象。

它是如何工作的?纽约大学团队的方法涉及一个带有两个模块的芯片:一个嵌入式芯片证明其计算是正确的,另一个外部模块用于验证第一个模块的证明。关键部分是可以与芯片分开制造的验证处理器。

“使用由受信任的fabrica-tor制造的外部验证单元意味着我可以去不受信任的代工厂生产芯片,该芯片不仅具有电路执行计算,而且还具有提供正确性证明的模块,”Garg解释道。

然后,芯片设计人员可以求助于受信任的代工厂来构建一个单独的、不太复杂的模块:专用集成电路(ASIC),其工作是验证不受信任芯片的内部模块生成的正确性证明。

根据Garg的说法,这种安排为芯片制造商和最终用户提供了一个安全网。“在目前的系统下,我可以从带有嵌入式特洛伊木马的代工厂取回芯片。它可能不会在制造后测试期间出现,所以我会把它发送给客户,“他继续说道。“但两年后,它可能会开始行为不端。我们解决方案的好处是我不必信任芯片。每次我给它一个新的输入,它都会产生输出和正确性的证明,外部模块让我不断验证这些证明。

另一个好处是,外部代工厂制造的芯片比值得信赖的额定ASIC更小,更快,更节能 - 有时是几个数量级。因此,可验证的计算设置可能会减少生成证明所需的时间、精力和芯片面积。

“对于某些类型的计算,它甚至可以胜过替代方案 - 直接在可信芯片上执行计算,”Garg指出。

研究人员的下一步是探索技术,以减少生成和验证证明对系统施加的开销,并降低“证明者和验证者”芯片之间所需的带宽。“对于硬件,证据总是在布丁中,所以我们计划用真正的硅芯片来制作我们的想法原型,”Garg说。

同样值得指出的是,这并不是Garg在该领域的第一次重大贡献:2015年,他在一种流行的伪装电路以防止知识产权(IP)被盗的方法中发现了严重的安全漏洞。这些伪装电路可以在几分钟内进行逆向工程,因此他开发了一种新方法,使芯片的功能依赖于掺杂硅的杂质浓度的微小波动。用于“去层化”芯片以进行IP盗窃的光学工具无法识别通过这种方法保护的芯片的功能。

此外,Garg还因帮助创建一种有远见的“分裂制造”技术而被引用,该技术旨在挫败在制造过程中破坏IC的企图。设计计划不是让代工厂访问完整的芯片蓝图,而是在几个代工厂之间拆分和分配,这使得恶意行为者更难改变电路的功能。

审核编辑:郭婷

-

芯片

+关注

关注

456文章

50984浏览量

425148 -

集成电路

+关注

关注

5390文章

11579浏览量

362447 -

嵌入式

+关注

关注

5087文章

19150浏览量

306332

发布评论请先 登录

相关推荐

破坏性物理分析(DPA)技术在元器件中的应用

CMOS逻辑IC的使用注意事项

亿铸科技荣登中国潜在独角兽企业榜单

主线科技荣登中国潜在独角兽企业榜单

实力登榜!广域铭岛入选中国潜在独角兽企业

润芯微科技荣获中国潜在独角兽企业

钙钛矿太阳能电池中的潜在诱导降解(PID)分析

智取潜在的IC破坏

智取潜在的IC破坏

评论