来源:《半导体芯科技》杂志10/11月刊

作者:Farzaneh Sharifi, Branden Bates; CLASSONE TECHNOLOGY; Elie Najjar,Wenbo Shao博士;Erik Yakobson博士, Brian Gokey; MACDERMID ALPHA ELECTRONIC SOLUTIONS

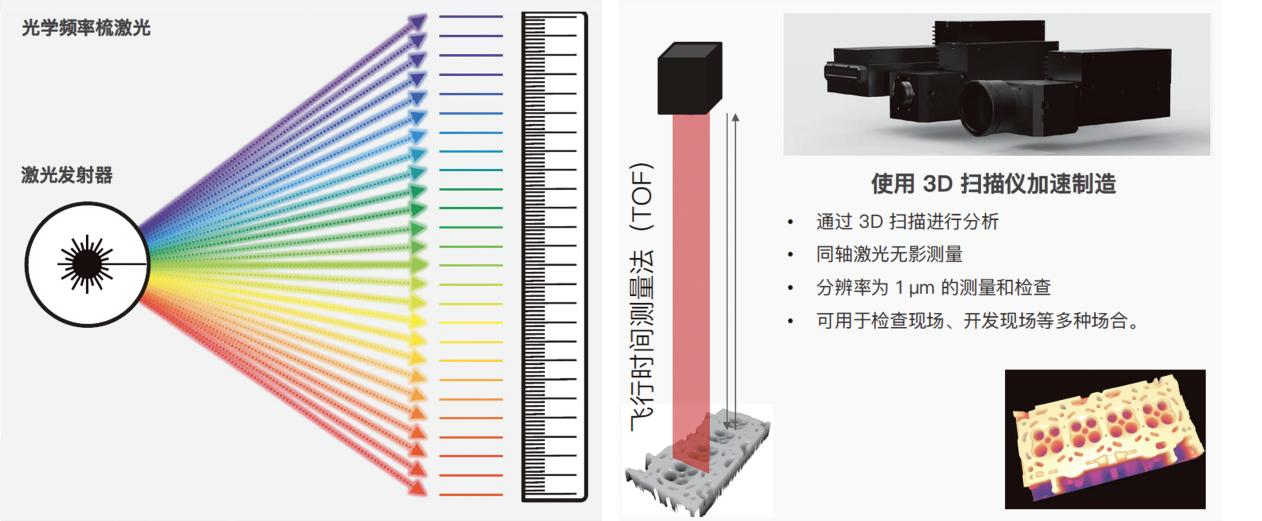

倒装芯片键合对于混合集成(hybridization)至关重要,混合集成是将来自不同技术的芯片组合成高性能模块的过程,例如激光雷达和其他成像应用中的混合像素探测器。曾经用于倒装芯片接合的锡焊料正在被包括铟在内的无铅替代品所取代。然而,使用传统方法制备对于形成键合必不可少的铟“凸点”是一项挑战。ClassOne Technology的专家们确信,一种新的电镀工艺可以解决铟凸点刚玉(corundum)的问题。

混合集成像素探测器广泛用于从高能物理到军事、环境和医疗等方面的成像应用。混合集成像素检测器将像素传感器芯片与读出集成电路(ROIC)相结合,从而允许对检测器中的每个像素进行电子访问。像素传感器由高电阻率硅制成,而ROIC则需要低电阻率材料。混合集成允许每个元件独立制造,然后通过称为倒装芯片或凸点键合的工艺耦合在一起。

倒装芯片键合创建了一个触点,可提供很高的输入/输出(I/O)密度以及传感器像素和ROIC之间的短互连距离,从而实现高性能器件。在倒装芯片键合期间,焊料凸点熔化从而形成这种连接。混合集成探测器中的像素放置在一个阵列中,它们之间的距离或间隙小于100微米。这种高连接密度需要更精细、更高精度的凸点和非常高良率的倒装芯片工艺,以确保每个像素都能够连接到IC。

倒装芯片的演变

传统的倒装芯片组装首先是使用铅基焊料凸点实现的,但由于其毒性,现在全球禁止在电子产品中使用这些材料,从而不得不重新审查这些材料。然而,无铅替代品,如纯锡或各种锡基无铅合金,例如SnAgCu(锡-银-铜,或SAC),在像素探测器中也面临挑战,因此寻找一种可行的替代品就摆在人们的面前。

由于读出芯片和传感器芯片由不同的材料制成,因此需要低温制造工艺来减少因热膨胀系数(CTE)不匹配而对传感器芯片造成的热影响。此外,传感器可能面临从严酷辐射到低温的极端环境。总之,所有这些挑战都需要一种具有特定性能的新型焊料。我们建议将铟作为此类首选候选材料之一。

为什么是铟?

铟是一种软质金属(比铅软),熔点低(156℃),具有很高的延展性和拉丝性,并且在极低的温度(甚至低至绝对零度,-273℃)下仍能保持这些特性。这使得铟成为低温和真空应用的理想选择。

就化学性质而言,铟仅在较高温度下才与氧发生反应,不溶于酸,和其他金属之间有良好的附着力,并具有浸润玻璃的能力。其良好的导电性、延展性和低温稳定性使其成为混合集成像素探测器应用中的理想选择。

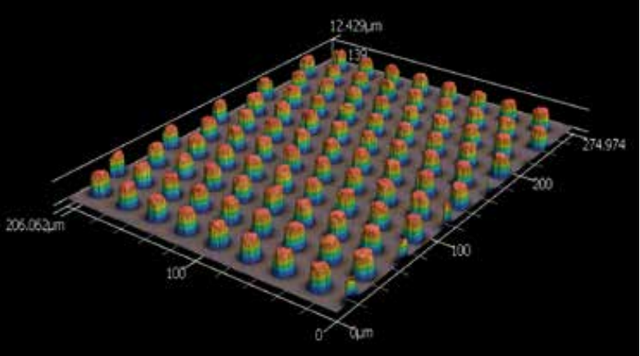

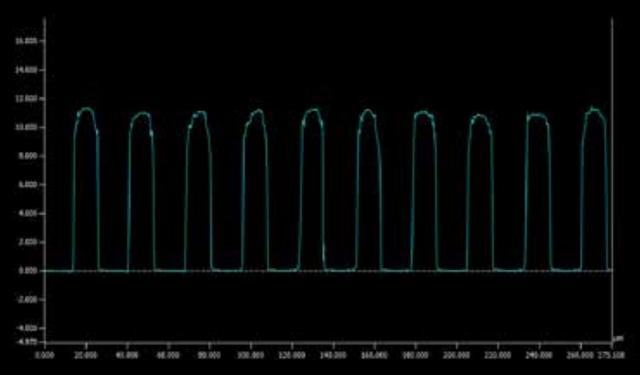

△图1:共聚焦显微镜数据-(a)铟的特征形貌图,(b)轮廓测量。

以前的方法

铟凸点以前是通过热蒸发或溅射制造的,这种方式能够形成具有良好凸点结构控制的高度均匀的凸点。然而,这种方法不能产生适合半导体行业当前需求的具有更小间隙的小凸点(更高的纵横比)。

此外,铟溅射需要昂贵的蒸发设备;仅限于具有高蒸气压的材料;需要复杂的制造工艺;由于掩模与晶圆的不匹配,不太适合更大的晶圆尺寸;因为它会产生更多污染,因此环境安全性较差;并且仅适用于小规模生产。

相比之下,具有高纵横比、低成本和简单制造工艺的电镀凸点,特别是针对于大规模生产是可以实现的方式。但是传统的电镀需要优化,因为不均匀的凸点会导致制造过程中的失效并降低混合集成芯片的可靠性。用于超精细间隙的铟凸点的蒸发既困难又耗时。此外,光刻胶掩模上的材料浪费使该工艺不具有成本效益,通过这种方法可实现的最小间距尺寸为30毫米。

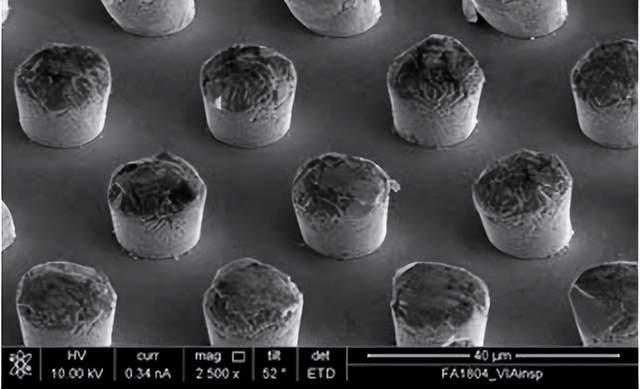

△图2:铟凸点的扫描电子显微镜图像。

电镀挑战

镀在用于制造倒装芯片键合凸点时面临多重挑战:它必须在晶圆级和高良率下实现所需的电镀凸点的均匀性和一致性、超精细间隙。随着间隙缩小和凸点数量增加,其挑战性将会急剧增加。随着晶圆特征尺寸的缩小,凸点尺寸将从50微米减小到15微米,间隙尺寸将从100微米减小到25微米。我们的目标是验证电镀能够产生高质量和高良率的高密度铟凸点。我们的工作证明,使用适当的工具和材料组合可以实现更小的凸点尺寸和更小的间隙。

随着晶圆特征尺寸的缩小,凸点尺寸将从50微米减小到15微米,间隙尺寸将从100微米减小到25微米。我们的目标是验证电镀能够产生高质量和高良率的高密度铟凸点。我们的工作证明,使用适当的工具和材料组合可以实现更小的凸点尺寸和更小的间隙。

工艺步骤

在硅晶圆上沉积凸点下金属化(UBM)之后,我们电镀铟凸点。对于UBM,需要一个阻挡层和粘合层(例如钛),然后是铟的可浸润层(例如镍或金),因为镍倾向于快速氧化。铟球的高度由铟的体积和可浸润性UBM焊盘的直径决定。在我们的测试中,我们使用铜作为UBM的最外层。在125℃左右的温度下,一些微量的铟与铜形成金属间相;然后,对于更高的温度,应使用阻隔金属,如镍-金或镍-铜。

去除UBM顶部层(我们测试中的铜)后,将晶圆加热到电镀铟凸点由于表面张力形成球体的温度。回流的目的是通过将铟重新塑造成球体来增加凸点高度,并帮助倒装芯片键合对准。

在回流之前,用与水混合的硝酸蚀刻掉铜种子层。钛是一种不浸润的材料,用于防止铟在回流期间扩散到整个表面。铟对UBM的顶层(铜)具有良好的粘附性,但对周围的材料(Ti)则不是。

回流必须在无氧环境中进行,即炉体中需要有受控气氛;否则,会形成氧化铟,阻碍铟凸点的形成。在我们的研究中,凸点在大约200℃的温度下和表面吹氮气的条件下在热板上回流。

回流后,像素传感器和ROIC在室温下通过低压进行配对。在工业应用中,在倒装芯片工艺之后会进行第二次回流,以实现与熔融铟的表面张力的自对准,并且使之具有高的强度。

影响凸点质量和良率的因素包括不均匀的UBM、蚀刻工艺、回流温度分布和回流后的清洗。在光刻过程中,光刻胶的准确对准对于获得高质量的凸点至关重要,但没有在蒸发工艺中那么关键。电镀工艺中的电流分布和物质传输是电镀中决定铟沉积物生长和影响凸点形状演变的主要因素。

实验方法

在这项工作中,我们尝试电镀超精细间隙铟凸点(特征尺寸为10μm,像素间隙为5μm和7.5μm),并有非常均匀的高度。我们使用6英寸的硅晶圆作为基板,其上带有铜种子层和17μm厚的光刻胶,以曝光形成所需的图案。光刻胶厚度需要严格控制以确保良好的凸点轮廓。我们使用真空预浸润工艺来去除气泡和预浸润小的图案,并选择纯铟板作为阳极,确保100%的阳极效率。

通过直流(DC)、脉冲和脉冲反向电流波形进行铟凸点电镀。脉冲和脉冲反向电流的平均电流密度保持与直流条件相同,以便进行直接比较。

电解质的作用

迄今为止,已有各种化学物质用于铟的电镀。由于析氢、大晶粒和结节导致的光刻胶损坏是传统铟电镀电解液造成的主要缺陷。MacDermid Alpha Electronics Solutions公司开发了一种铟电解质来克服这些致命缺陷。

Novafab IN-100是一种酸性电解质系统,用于低温、无铅焊接互连。这种专有电解质的配方可高效沉积铟金属,并且与传统的铟电镀浴不同,由于其创新的化学成分,不会产生析氢。

在电镀过程中,金属-溶液界面处的pH值保持稳定,消除了可能导致光刻胶剥离和损坏的pH值急剧升高。因此,Novafab IN-100因其固有的光刻胶兼容性而适用于光刻胶图案化晶圆电镀。它产生细粒度、无结节的亚光沉积物,铟纯度>99.5%,并表现出卓越的附着力。该溶液是完全可解析的,并且与可溶性和不溶性阳极系统兼容。

结论

电镀凸点的高度是使用共聚焦显微镜测量的,如图1所示。为了消除非优化回流工艺的影响,高度测量在电镀之后和回流工艺之前进行。在我们使用的三种波形中,具有高开启时间与关闭时间比率的脉冲电镀产生了最好的结果。测量凸点的高度,我们能够在整个晶圆上获得不到10%的非均匀性。

在我们的演示过程中,凸点表面确实形成了氧化铟层,因此我们无法在回流后获得完美形状的球体,但观察到凸点开始变圆并形成球体。

在ClassOne的Solstice单晶片平台上,铟电解质的特性与倒装芯片工艺相结合,展示了一种将铟用于倒装芯片电镀工艺的可行方法。

审核编辑 黄昊宇

-

电镀

+关注

关注

16文章

478浏览量

25891 -

键合

+关注

关注

0文章

107浏览量

8304 -

倒装芯片

+关注

关注

1文章

124浏览量

16868

发布评论请先 登录

高频超声键合技术:引线键合工艺优化与质量检测方法

半导体封装引线键合技术:超声键合步骤、优势与推拉力测试标准

超声键合技术是什么?芯片封装的工艺原理与应用解析

NTC热敏芯片键合工艺介绍

IGBT 芯片平整度差,引发键合线与芯片连接部位应力集中,键合失效

芯片制造中的键合技术详解

什么是引线键合?芯片引线键合保护胶用什么比较好?

电镀创新实现超精细铟键合

电镀创新实现超精细铟键合

评论