packed union相比unpacked union最大的一个区别就是,在packed union中,所有成员的大小必须相同,这就保证了不管union中存储了哪一个成员,最终这个union的大小是一样的。也正是加了这个限制,所以packed union是可综合的。

类似于packed struct,我们可以对这个union整体进行算法、切分等运算。

typedef union packed {

int a;

bit [31:0] c;

} data;

上面的union声明加入了packed关键字。因为两个成员的大小相同:“int”是32位,“bit [31:0] c”是32位。所以声明为unpacked union是没问题的。

typedef union packed {

logic [9:0] data;

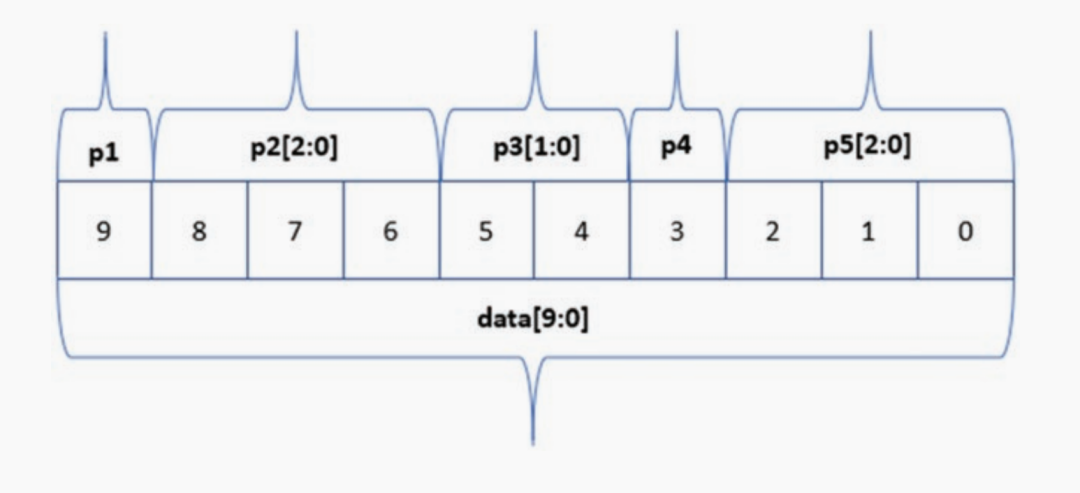

struct packed {

bit p1;

bit [2:0] p2;

bit [1:0] p3;

bit p4;

bit [2:0] p5;

} p_modes;

} myUnion

myUnion Union1;

在上面的union中有2个成员,分别都是10比特大小 “struct” “p_modes” 和“data” ,在物理内存中分配如下:

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Verilog

+关注

关注

28文章

1355浏览量

110870 -

System

+关注

关注

0文章

165浏览量

37230 -

union

+关注

关注

0文章

10浏览量

4330

原文标题:SystemVerilog中的Packed Union

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

union 的概念及在嵌入式编程中的应用

union 在中文的叫法中又被称为共用体,联合或者联合体,它定义的方式与 struct 是相同的,但是意义却与 struct 完全不同,下面是 union ...

发表于 02-07 11:30

•0次下载

SpinalHDL中Bundle数据类型的转换

SpinalHDL中Bundle与SystemVerilog中的packed struct很像,在某些场景下,与普通数据类型之间的连接赋值可以通过asBits,assignFromBi

unpacked数组和packed数组的主要区别

unpacked数组和packed数组的主要区别是unpacked数组在物理存储时不能保证连续,而packed数组则能保证在物理上连续存储。

SystemVerilog中的Packed Structure

一个packed structure有很多的bits组成,这些bit在物理上连续存储。packed structure只允许包含packed数据类型。

Systemverilog中的union

SystemVerilog union允许单个存储空间以不同的数据类型存在,所以union虽然看起来和struct一样包含了很多个成员,实际上物理上共享相同的存储区域。

SystemVerilog中的tagged Unions是什么

tagged union包含一个隐式成员,该成员存储tag,也就是标记,它表示这个union最终存储的到底是哪一个成员。

SystemVerilog中的Semaphores

SystemVerilog中Semaphore(旗语)是一个多个进程之间同步的机制之一,这里需要同步的原因是这多个进程共享某些资源。

union和union all有什么区别

Union和Union All是SQL中的两个关键字,它们用于将两个或多个SELECT语句的结果集合并在一起。这两个关键字虽然有相似的功能,但在实际使用中有一些重要的区别。下面将详细介绍Uni

SystemVerilog中的Packed Union

SystemVerilog中的Packed Union

评论