1. 什么是8b/10b编码?

8b/10b最常见的是应用于光纤通讯和LVDS信号的。由于光模块光模块只能发送亮或者不亮,也就是0或者1这两种状态这种单极性码,那么这会存在一个问题,如果传输中出现较长的连0或者连1(例如111111100000000),那么接收端将没有办法正确的采样识别信号,另外还会由于单极性码含有直流分量,这种直流成分会随数据中1和0的随机变化也呈现随机性,这会引起接收端的基线漂移导致接收端误判。LVDS信号一样会存在这个问题,随着线路上的信号频率越来越高,如果线路上的0和1数量不均衡(直流不平衡)那么线路上的基电压会出现偏移,一样会导致解码错误。

总之一句话,8b/10b是为了解决直流平衡而推出的。

8B/10B编码是加扰二进制码的一种,在此之前这种技术已得到应用,只是没有像8B10B那么普遍。目前采用8b/10b编码的串行高速接口总线有IEEE 1394b、SATA、PCI Express、Infini-band、Fiber Channel、RapidIO、USB3.0、MIPI M-phy 等。

将8bit编码成10bit后,连续的1或者0不能超过5位,所以10b中0和1的位数只可能出现3中情况:

• 有5个0和5个1

• 有6个0和4个1

• 有4个0和6个1

**不均等性:**这样引出了一个新术语“不均等性”(Disparity),就是1的位数和0的位数的差值,根据上面3种情况就有对应的3个Disparity0、-2、+2。

2. 为什么引入8b/10b编码?

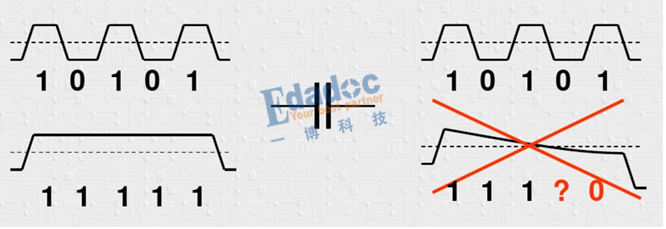

首先,为什么要编码?原来的码型有什么不好的地方吗?其中最主要的原因用下面这个图来进行解释:

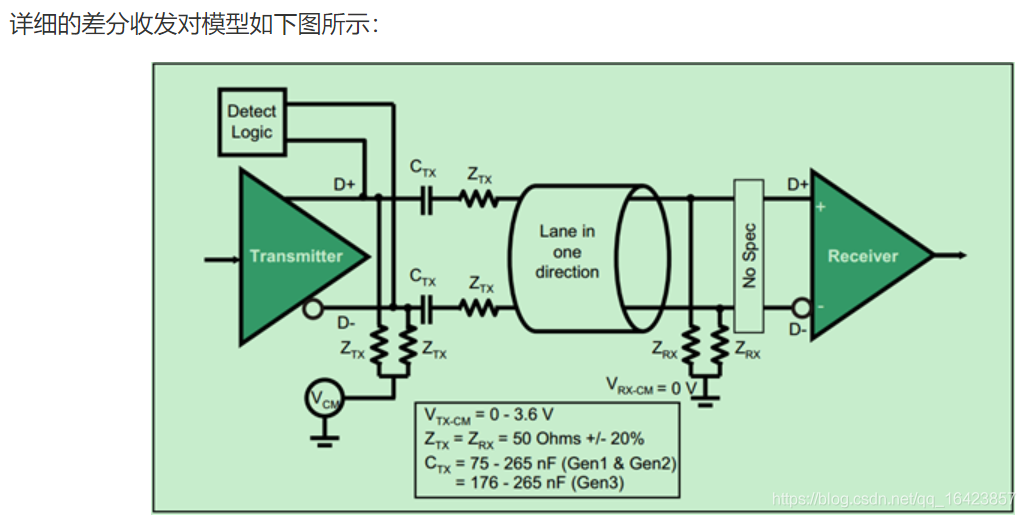

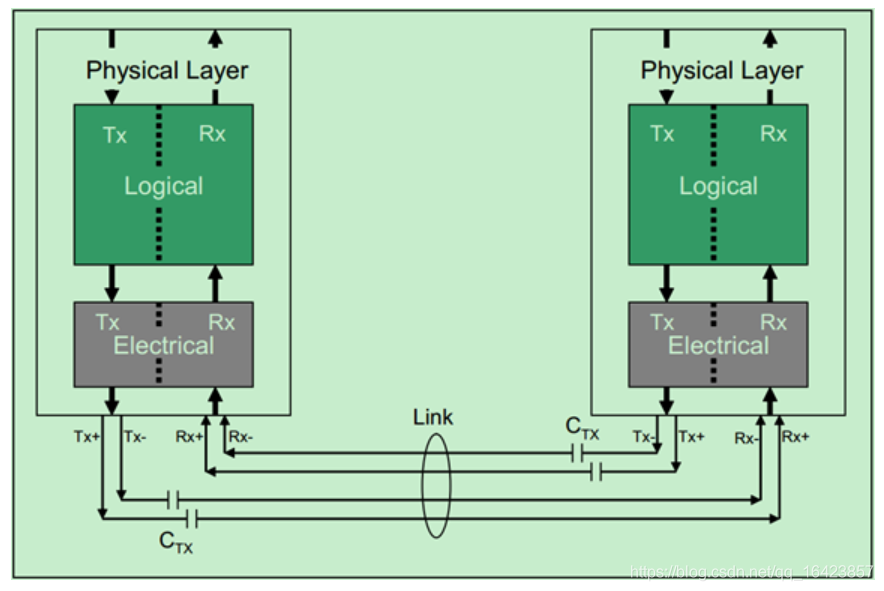

大家看明白了吧,由于我们的串行链路中会有交流耦合电容,我们知道理想电容的阻抗公式是Zc=1/2πf*C,因此信号频率越高,阻抗越低,反之频率越低,阻抗越高。因此上面的情况,当码型是高频的时候,基本上可以不损耗的传输过去,但是当码型为连续“0”或者“1”的情况时,电容的损耗就很大,导致幅度不断降低,带来的严重后果是无法识别到底是“1”还是“0”。因此编码就是为了尽量把低频的码型优化成较高频的码型,从而保证低损耗的传输过去。

3. 8b/10b的编码算法

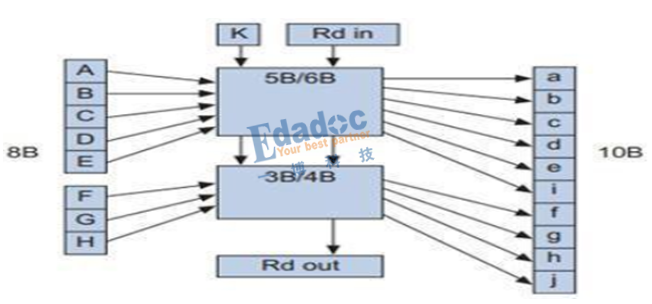

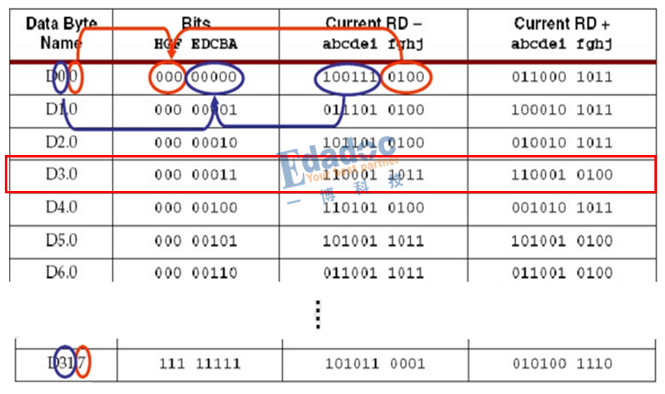

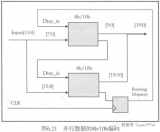

如上图,关于8B/10B编码算法有下面几点需要理解:

1, 低5位(ABCDE)中间加一位,进行5B/6B编码,高三位(FGH)中间加一位,进行3B/4B编码;

2, 编码后的bit仅会出现这三种情况:5个“0”与5个“1”、4个“0”与6个“1”、6个“0”与4个“1”;

3, 有两个术语要知道:不均等性(disparity)和极性偏差(running disparity,RD)。

不均等性是指编码后的码型数据是“1”多还是“0”多,如果是“1”多,则极性偏差RD为RD-,如果是“0”多则为RD+。

那定义+/-RD有什么意义呢?+/-RD代表着同一个码型的两种编码方式。我们本身就是编码的目标就是为了缓解长“0”或长“1”的影响,因此在编码后如果“1”多的话,我们下一次的编码就要把这种码型做一个修正,因此从-RD码型变成+RD码型。如果是“0”和“1”一样多,极性则不用变,如下图:

4, 我们怎么知道编码后映射成什么码型呢?因此会有一个专门的编码表,我们只需要在上面找到我们的原始码型,然后就一目了然了。编码表如下所示(部分截图):

说了那么多,还不如举个例子更直观。

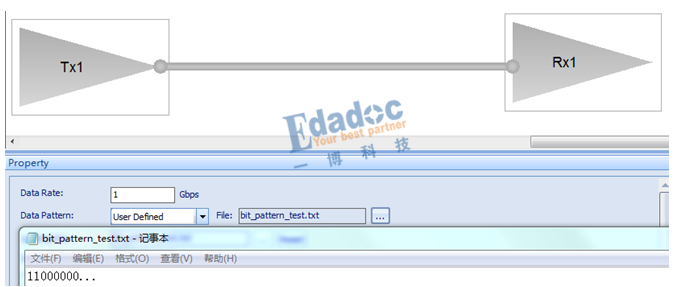

我们以上面的D3.0码型进行仿真验证:

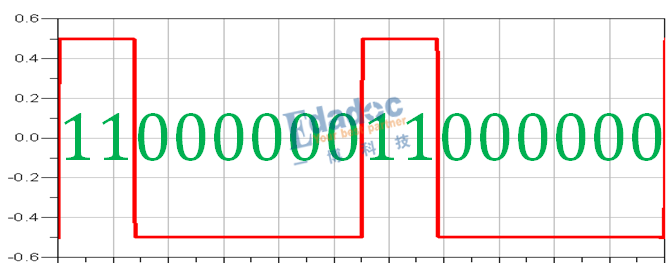

原始的码型如下:

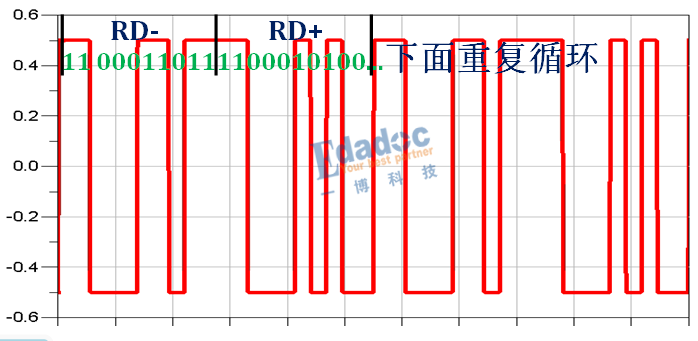

仿真得到8B/10B编码后的码型如下:

对照上面的编码表,结果完全相同,从RD-的模型出发,编码后RD-的码型“1”比较多,因此极性变成RD+的编码码型,接着RD+的编码码型“0”比较多,极性又变回RD-,因此码型就是RD-和RD+之间循环下去。

-

lvds

+关注

关注

2文章

1042浏览量

65787 -

编码

+关注

关注

6文章

940浏览量

54810

原文标题:8b/10b编码

文章出处:【微信号:硬件测试杂谈,微信公众号:硬件测试杂谈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

USB3.0与USB2.0编码方式的区别

8b10b编码verilog实现

Aurora 8b/10b IP核问题

收发器向导中启用8b/10b编码器的方法是什么?

如何使用Aurora 8B / 10B建立仅传输?

怎么禁用Aurora IP Core 8B / 10B中的时钟补偿功能?

基于FPGA的8B/10B编解码设计

基于PRBS的8B/10B编码器误码率为0设计

基于Virtex-6 的Aurora 8B/10B,PCIe2.0,SRIO 2.0三种串行通信协议分析

高速串行通信常用的编码方式-8b/10b编码/解码解析

一文详解8b/10b编码

一文详解8b/10b编码

评论