摘要

比较SiC开关的数据资料并非易事。由于导通电阻的温度系数较低,SiC MOSFET似乎占据了优势,但是这一指标也代表着与UnitedSiC FET相比,它的潜在损耗较高,整体效率低。

博客

谚语说:“不怕低,只怕比”。这条谚语首次出现在1440年约翰·利德盖特的《马鹅羊之间的辩论》中。疲于比较的不仅仅是文章中的动物,现代功率转换器设计师们也不得不拼命从大量竞争性主张中尝试找出适合他们的应用的功率开关,并进行比较,以获得“最佳性能”。如果继续以农牧业来比喻,这个问题就像是将一个苹果与一堆苹果相比较,因为如果不考虑与其他指标的权衡取舍,就不能评价任何单个电子参数的好坏。开关导通电阻就是一个好例子,你必须在相同的额定电压下,在各个制造商的建议栅极驱动电压下,在相同的结温和漏极电流下,在相同的封装中比较零件,才能了解这个参数。

Si-MOSFET、SiC-MOSFET和SiC FET竞争上岗

在不低于几百伏的较高电压下,Si MOSFET、SiC MOSFET和UnitedSiC FET是同一个位置的有力竞争产品,它们的数据资料中通常标明特定额定电压、结温和栅极驱动电压下的RDS(ON)值。例如,UnitedSiC最近推出的零件UJ4C075018K4S就提供了在VGS = 12V、温度为25°C至175°C、漏极电流为20A时的导通电阻值。从中,您可以轻松获得该零件在给定温度下的RDS(ON)温度系数数值,在Tj =125°C时,该数值约为+70-75%。

650V SiC MOSFET的拥护者可能会指出,他们发现其他类似器件在Tj =125°C下的该数值通常为+20-25%。这能说明SiC MOSFET比其他器件好三倍吗?恐怕不能这么武断。首先,部分正温度系数值是必要的,可以迫使晶粒中的单元分担电流,而不会出现热点和热散逸。同理,设计师依靠正值才能并联器件,并自然分流。

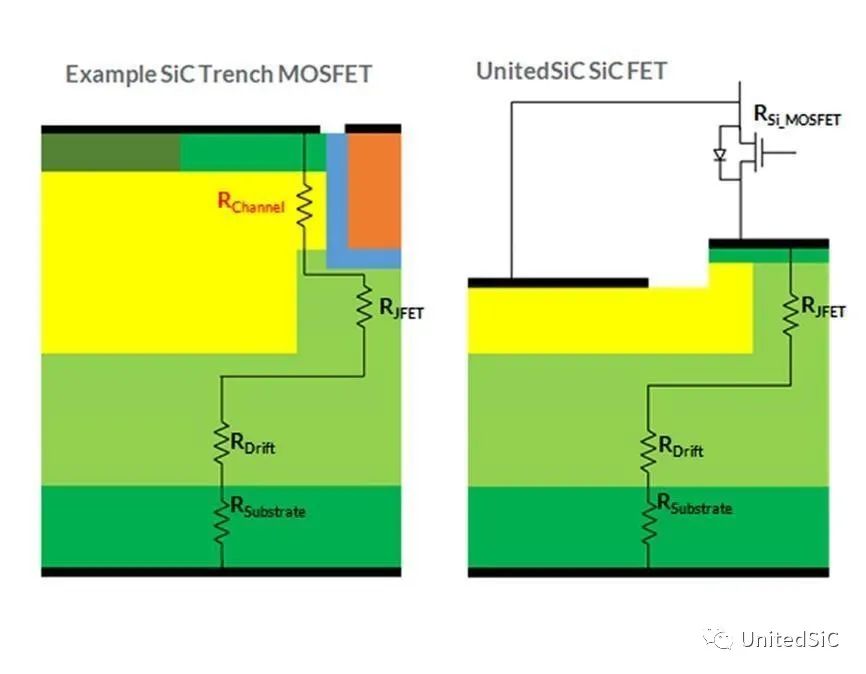

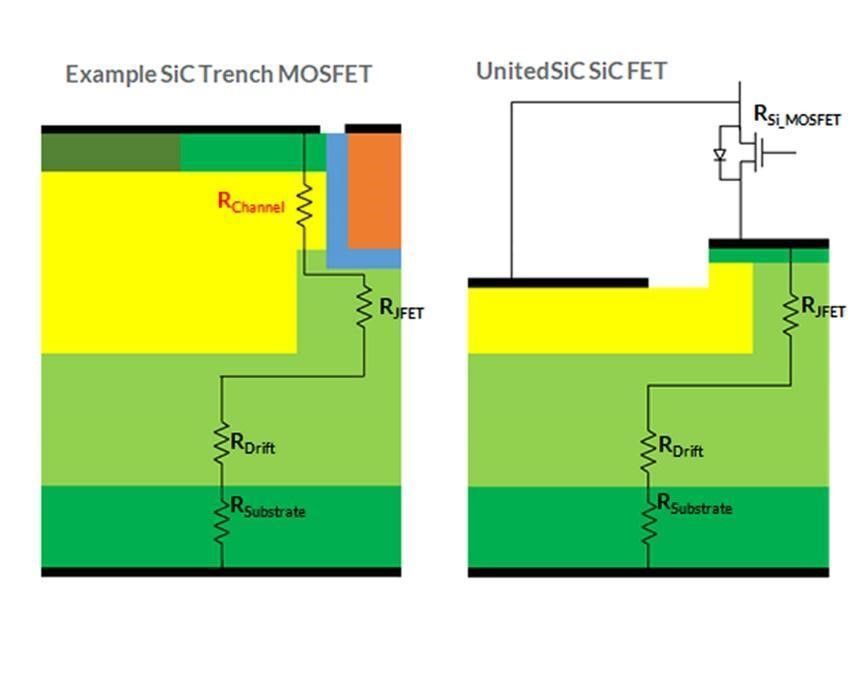

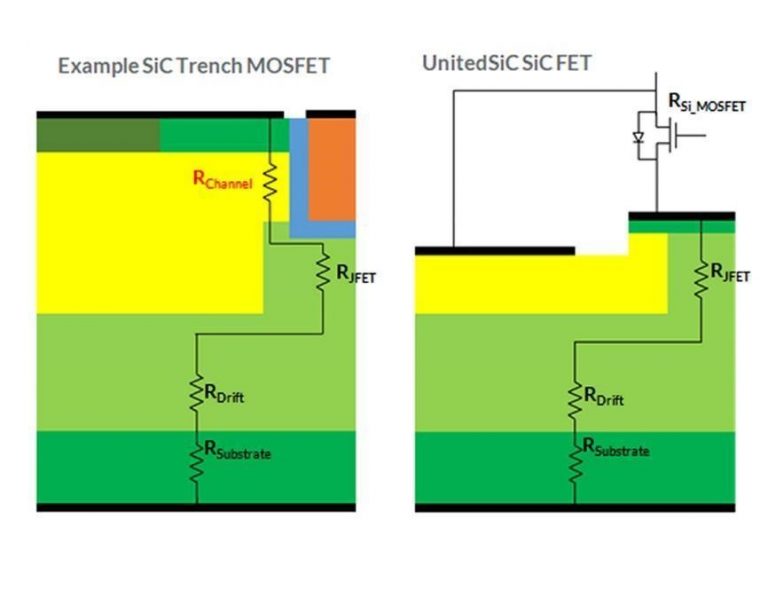

SiC MOSFET的电阻由其反型沟道决定

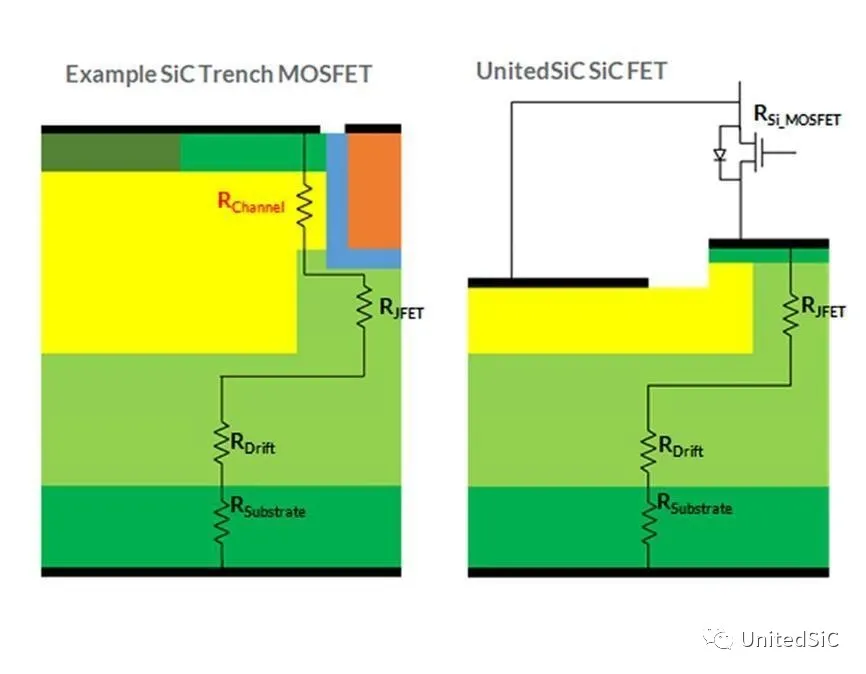

SiC MOSFET较低的RDS(ON)温度系数值实际上表明会出现较深层次的影响。MOSFET和JFET是“单载流子”器件,电子流会经过不同区(基质、漂移层、JFET区和沟道等)。在650V SiC MOSFET中,反型沟道决定了总电阻,而总电阻实际上会随着温度降低。沟道电阻与自由载流子数和反型层电子迁移率的乘积成反比。随着温度升高,阈值电压会降低,而沟道中的自由载流子数会增加,因而电阻会降低。其余器件区(即JFET、漂移层和基质电阻)的正温度系数会抵消这种影响,从而产生不高的净正Tc值。在SiC JFET中,没有反型沟道来抵消JFET、漂移层和基质的正温度系数。同时,低压Si MOSFET仅占总导通电阻的一小部分,这解释了为什么采用它时的Tc值比采用SiC MOSFET时要高,不过有说服力的一点是,SiC FET中不存在由不理想的SiC反型层造成的损耗(图1)。

【图1:典型的SiC MOSFET沟槽结构和没有大损耗SiC MOS反型沟道的UnitedSiC FET,后者有较高的导通电阻温度系数,但是损耗较低】

SiC FET的整体导电损耗较低

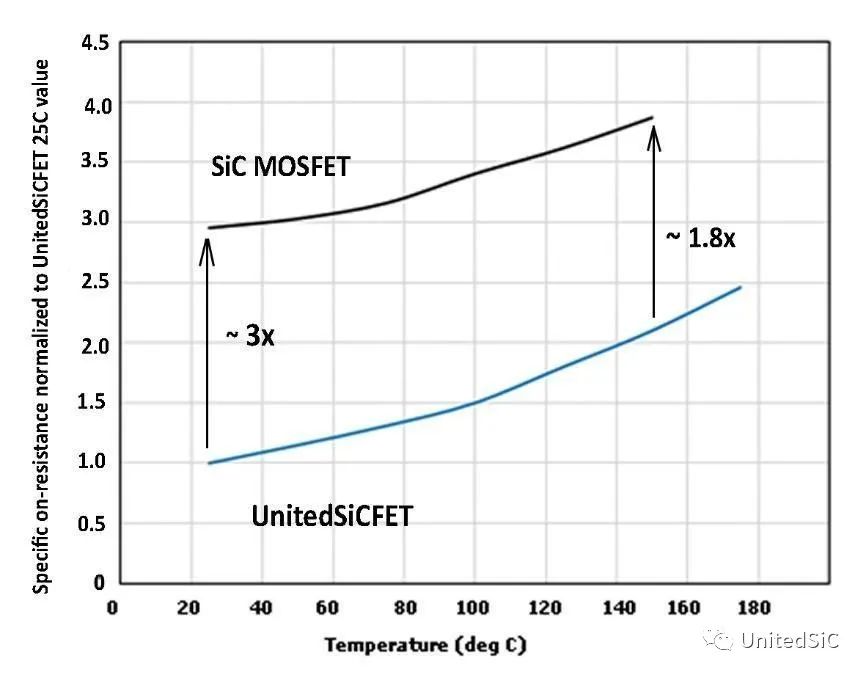

如果审视绝对值,则会发现决定性的证据。如图2所示,在比较650/750V器件的RDS(ON)时,在25°C时,UnitedSiC FET的导通电阻大约是SiC MOSFET的三分之一,优势最明显,在150°C时,仍比后者好2倍左右,在相同有效晶粒面积下,前者带来的导电损耗大约是后者的一半。

【图2:UnitedSiC FET导通电阻的Tc较高,但是绝对值较低】

采用UnitedSiC FET的最终效果是整体导电损耗较低,且RDS(ON)的正温度系数十分健康,可确保单元和并联器件之间实现有效分流。很明显,确保合理进行比较并理解这种效果背后的机制是值得的,它揭示了什么才是真正重要的,那就是较低的整体损耗。

审核编辑:汤梓红

-

MOSFET

+关注

关注

147文章

7176浏览量

213382 -

FET

+关注

关注

3文章

634浏览量

62970 -

SiC

+关注

关注

29文章

2823浏览量

62668

原文标题:【技术贴】在正确的比较中了解SiC FET导通电阻随温度产生的变化

文章出处:【微信号:UnitedSiC,微信公众号:UnitedSiC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

在正确的比较中了解SiC FET导通电阻随温度产生的变化

在正确的比较中了解SiC FET导通电阻随温度产生的变化

在正确的比较中了解SiC FET导通电阻随温度产生的变化

评论