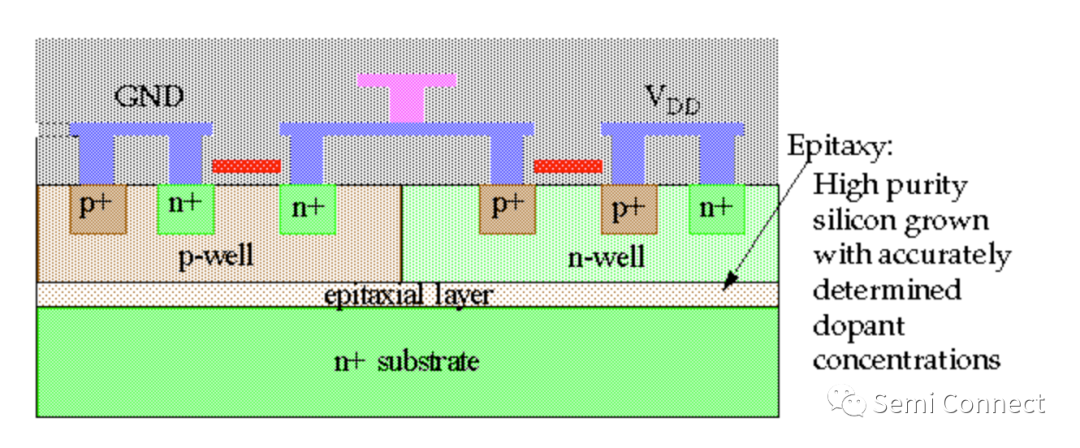

CMOS集成电路的基础工艺之一就是双阱工艺,它包括两个区域,即n-MOS和p-MOS 有源区,分別对应p阱和N阱,如图所示。

在进行阱注入时,产业内的主流技术多数采用倒掺杂技术来调节晶体管的电学特性,即首先采用高能量、大剂量的离子注入,注入的深度约为 1um,注入区域与阱相同,随后通过大幅降低注入能量及剂量,控制注入深度和掺杂剖面。阱的注入掺杂不仅可以调节晶体管的阈值电压,也可以解决CMOS 电路常见的一些问题,如闩锁效应和其他可靠性问题。

双阱 CMOS 工艺是当前集成电路的标准工艺之一,它最初是在 n-MOS工艺和 p-MOS 工艺的基础上发展起来的。

早期的双阱 CMOS 工艺没有高能量大剂量的注入,只是用中能量和中剂量离子注入n阱和p阱的区域,然后热退火形成独立的n阱和p阱。

随着离子注入技术的发展,高能量大剂量的注入不再成为离子注入的难题,并且高能量大剂量的注入形成的倒置阱效果很明显,所以才逐步形成现在的标准双阱工艺。

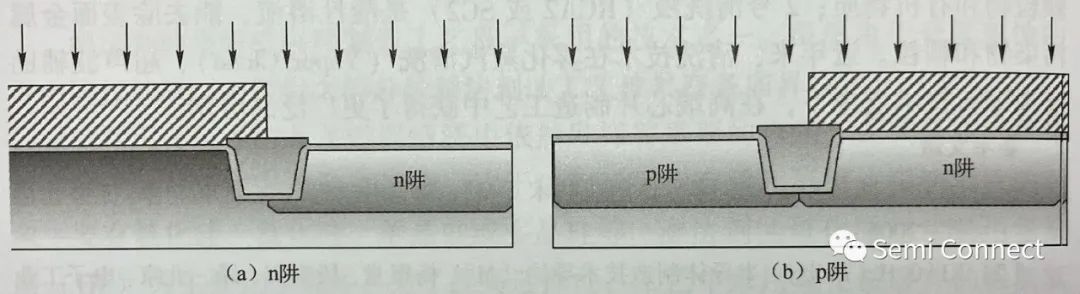

双阱工艺常见的基本制造步骤是先制作n阱,包括牺牲氧化层生长,n阱区域光刻,n阱注入,然后退火;p阱的形成与其类似。

确定双阱工艺的基本条件是确保器件电学特性满足要求,包括阱之间的击穿电压、有效的电学隔离、避免闩锁效应、合适的阈值电压等。

另外,衬底材料的掺杂情况也对阱的形成条件有很大影响。

审核编辑:刘清

-

集成电路

+关注

关注

5391文章

11618浏览量

362956 -

CMOS

+关注

关注

58文章

5735浏览量

235997 -

晶体管

+关注

关注

77文章

9744浏览量

138791

原文标题:模块工艺——双阱工艺(Twin-well or Dual-Well)

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

CMOS集成电路使用时的技术要求

怎么采用标准CMOS工艺设计RF集成电路?

集成电路与MCU简析

混合集成电路CMOS工艺中LowDose率对寄生双极结构的影响分析概述

CMOS集成电路的双阱工艺简析

CMOS集成电路的双阱工艺简析

评论