今年10月,IBM发布了旗下首款人工智能计算单元(Artificial Intelligent Unit,AIU)片上系统。

这是一种专用集成电路 (ASIC),旨在更快、更高效地训练和运行需要大规模并行计算的深度学习模型。

AIU:专为现代AI计算打造

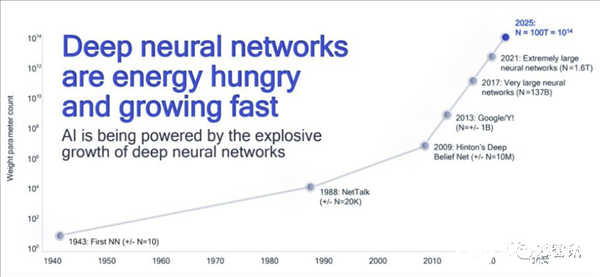

在过去多年来,业界主要是利用CPU、GPU来运行深度学习模型,但是随着人工智能模型的数量正呈指数级增长。

同时深度学习模型也越来越庞大,有数十亿甚至数万亿的参数,需要的算力也是越来越高,而CPU、GPU这类传统架构的芯片的AI算力增长已经遇到了瓶颈。

△深度神经网络对于算力的需求增长迅速

根据 IBM 的说法,深度学习模型传统上依赖于 CPU 和 GPU 协处理器的组合来训练和运行模型。

CPU 的灵活性和高精度非常适合通用软件应用程序,但是,在训练和运行需要大规模并行 AI 操作的深度学习模型时,CPU却处于劣势。

GPU最初是为渲染图形图像而开发的,但后来该技术发现了在AI计算中使用的优势。

但是,CPU和GPU都是在深度学习革命之前设计的,现在他们的效率增长已经落后于深度学习对于算力的指数级增长,业界真正需要的是针对矩阵和向量乘法运算类型进行优化的通用芯片来进行深度学习。

基于此,IBM Research AI Hardware Center在过去五年中一直专注于开发下一代芯片和人工智能系统,希望以每年将人工智能硬件效率提高 2.5 倍,并能够在 2029 年以比 2019 年快1000倍的速度训练和运行人工智能模型。

最新AIU芯片则是IBM推出的首款针对现代 AI 统计数据定制的芯片。

IBM表示,AIU是专为加速深度学习模型使用的矩阵和向量计算而设计和优化。AIU 可以解决计算复杂的问题,并以远远超过 CPU 能力的速度执行数据分析。

那么IBM AIU是如何实现针对深度学习优化的呢?答案是:“近似计算”+“简化人工智能工作流程”。

拥抱低精度,采用近似计算

从历史上看,很多AI计算依赖于高精度 64 位和 32 位浮点运算。IBM 认为AI计算并不总是需要这种精确度。

它有一个降低传统计算精度的术语——“近似计算”。在其博客中,IBM 解释了使用近似计算的基本原理:

“对于常见的深度学习任务,我们是否需要这种准确度?我们的大脑是否需要高分辨率图像来识别家庭成员或猫?当我们输入一个文本线程进行搜索时,我们是否需要第 50,002 个最有用的回复与第 50,003 个最有用的回复的相对排名的精度?答案是,包括这些示例在内的许多任务都可以通过近似计算来完成。”

基于此,IBM 首创了的一种称为近似计算的技术,可以从32位浮点运算下降到包含四分之一信息的混合8位浮点(HFP8)计算格式。这种简化的格式极大地减少了训练和运行 AI 模型所需的数字运算量,并且不会牺牲准确性。

更精简的位格式还减少了另一个对速度的拖累:只需将更少的数据移入和移出内存,即运行AI模型对于内存的占用更少了。

IBM在其新的AIU芯片的设计当中融入了近似计算技术,使得AIU芯片的精度需求大幅低于 CPU 所需的精度。较低的精度对于在新的 AIU 硬件加速器中实现高计算密度至关重要。

AIU使用混合 8 位浮点(HFP8)计算,而不是通常用于 AI 训练的32位浮点或16位浮点运算。较低精度的计算使芯片的运行速度比 FP16 计算快 2 倍,同时提供类似的训练结果。

虽然低精度计算对于获得更高的密度和更快的计算是必要的,但深度学习 (DL) 模型的精度必须与高精度计算保持一致。

简化人工智能工作流程

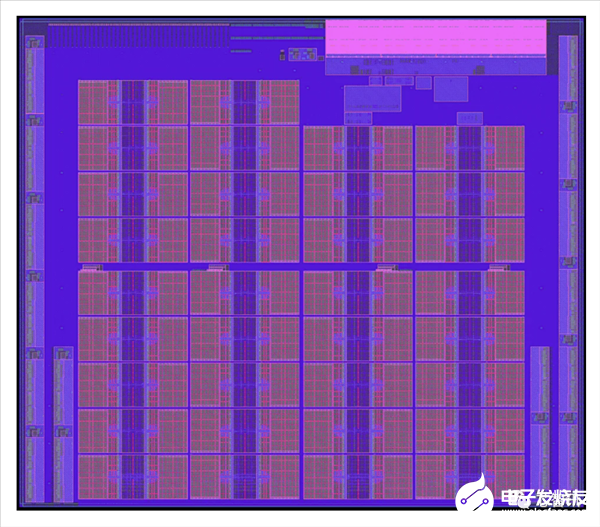

由于大多数 AI 计算都涉及矩阵和向量乘法,因此IBM AIU芯片架构具有比多用途 CPU 更简单的布局。

IBM AIU还针对将数据直接从一个计算引擎发送到另一个计算引擎进行设计,从而节省大量能耗。

据IBM介绍,其AIU芯片是一个完整的片上系统,是基于IBM此前的Telum芯片(7nm工艺)中内置的经过验证的 AI 加速器的扩展版本,并且采用了更先进的5nm制程工艺,具有 32 个处理内核并包含 230 亿个晶体管。

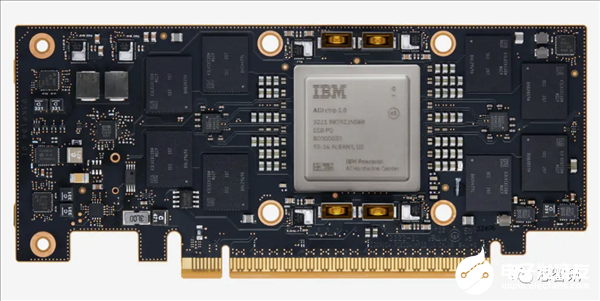

IBM AIU 还被设计为像显卡一样易于使用。它可以插入任何带有 PCIe 插槽的计算机或服务器。

IBM表示:“部署 AI 对照片中的猫和狗进行分类是一项有趣的学术活动。但它不会解决我们今天面临的紧迫问题。我们要让 AI 解决现实世界的复杂性——比如预测下一个飓风伊恩,或者我们是否正在走向衰退——我们需要企业级的工业级硬件。我们的 AIU 让这一愿景更近了一步。”

IBM AIU表现如何?

IBM并未在其官网公布更多关其AIU芯片的技术信息。不过,我们可以通过回顾 IBM在 2021 年国际固态电路会议(ISSCC)上展示其早期 7nm 芯片设计的性能结果时的初始原型演示来对其性能有所了解。

IBM 用于会议演示的原型不是 32 个内核,而是一个实验性的 4 核 7nm AI 芯片,支持 FP16 和混合FP8 格式,用于训练和推理深度学习模型。

它还支持用于扩展推理的 int4 和 int2 格式。2021 年 Lindley Group通讯中包含了原型芯片性能的摘要,该通讯报道了 IBM 当年的演示:

在峰值速度下,使用 HFP 8,该7nm芯片实现了每秒每瓦特 (TF/W) 1.9 teraflops。

使用INT4进行推理,该实验芯片达到16.5 TOPS/W,优于高通低功耗Cloud AI模组。

考虑到IBM AIU是该测试芯片的扩展版本,并且制程工艺也升级到了5nm,因此预计其整体能效将进一步提升,同时随着核心数量由4核上升到32核,其整体的峰值算力有望提升超过8倍。

Forbes的分析师认为,由于缺乏信息,无法将IBM的AIU与目前被用于AI计算的GPU相比较,但是,预计该芯片的价格将会在1500 美元到 2000 美元之间。

-

IBM

+关注

关注

3文章

1885浏览量

77172 -

5nm

+关注

关注

1文章

343浏览量

26692

发布评论请先 登录

晶体管达林顿光耦:核心特性驱动的技术优势与应用价值

晶体管输出特性曲线的构成与核心区域

电压选择晶体管应用电路第二期

晶体管的定义,晶体管测量参数和参数测量仪器

IBM AIU芯片揭秘:5nm 32核心、230亿个晶体管!

IBM AIU芯片揭秘:5nm 32核心、230亿个晶体管!

评论