集成电路是由很多晶体管组成的,各个晶体管的工作状态也不尽相同,如果不进行有效的隔离,就会形成相互干扰,集成电路就不能正常工作。所谓隔离技术,就是阻断器件有源区之间的电流和电压信号互相干扰,从而保证器件和电路正常工作的技术,通常有pn 结隔离、介质隔离,以及pn 结介质混合隔离,其中介质隔离包括局部氧化 (Local Oxidation of Silicon, LOCOS)隔离和浅槽隔离 (Shallow Trench Isolation, STI)。

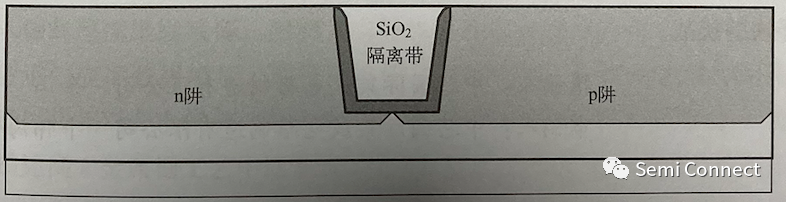

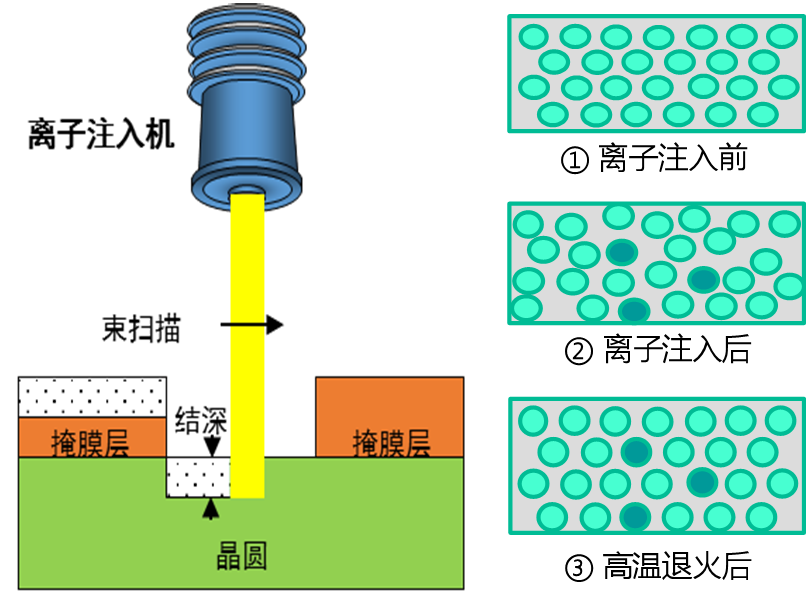

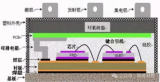

最早的隔离技术是 pn 结隔离,因为加上反向偏压,pn结就能起到很好的天然隔离作用。但是,由于其需要较宽的耗尽层,面积占比和电容均较大,响应速度慢,不适用于集成电路的隔离。随着平面工艺的发展,LOCOS隔离技术开始用于实现有源区的有效隔离。它的基本工艺原理是,使用氮化硅 (Si3N4)作为硅(Si)氧化的阻挡层,在有源区之间的场区热氧化形成 SiO2介质层,然后通过热磷酸高刻蚀选择比去除 Si3N4,从而实现有源区的隔离。由于热氧化存在横向氧化,LOCOS 隔离所用面积仍然较大,自0.25um 技术代开始,STI 技术取代LOCOS隔离技术成为超大规模集成电路的主流隔离技术,如图所示。

STI的基本工艺步骤是,在需要隔离的区域上用干法刻蚀形成 300~400nm 的硅槽,然后经过氧化表面处理,沉积 SiO2,填充硅槽,最后采用 CMP 去掉表面多余的SiO2,并实现平坦化。由于 STI 区域的尺寸差异较大,对CMP 的平面化工艺有所挑战。此外,STI 的沟槽的角度和深度等都会对器件特性造成很大的影响。

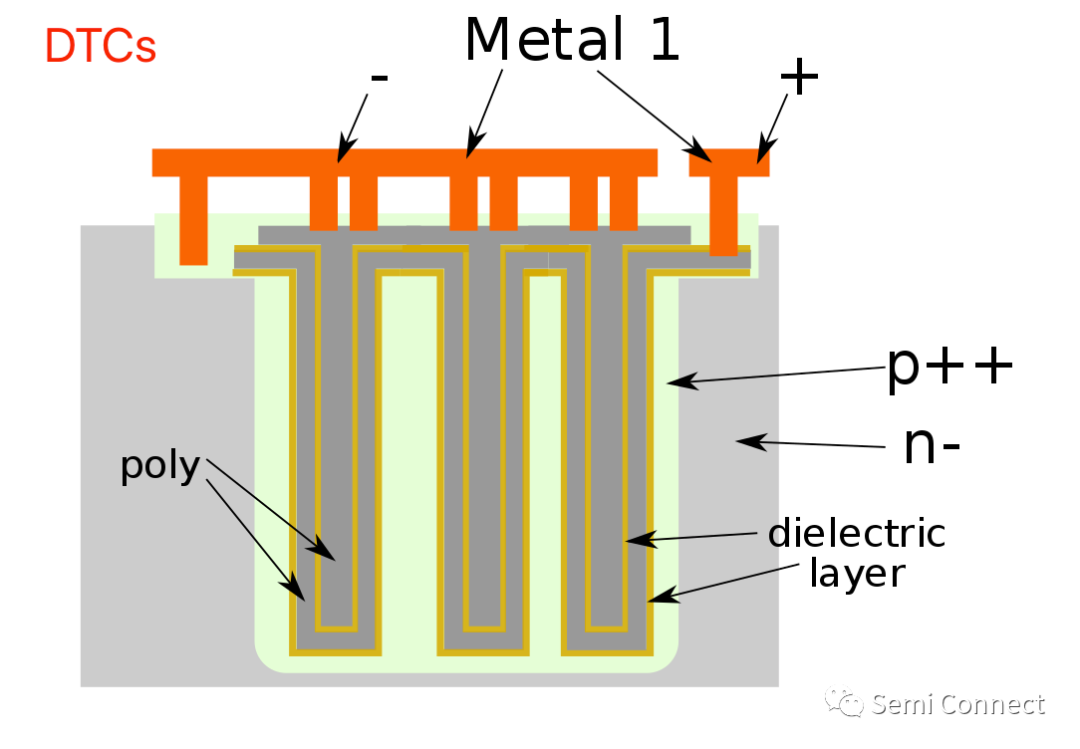

随着集成电路工作速度提升至 RF 频段甚至微波频段,对各种噪声和干扰的要求越来越严,在一些区域的 STI 无法满足要求,因此深槽隔离或其他隔离方式逐渐得到了发展。

审核编辑 :李倩

-

集成电路

+关注

关注

5388文章

11541浏览量

361718 -

工艺

+关注

关注

4文章

593浏览量

28783 -

晶体管

+关注

关注

77文章

9685浏览量

138127

原文标题:模块工艺——隔离工艺(Isolation)

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

IMD4工艺是什么意思

ILD工艺的制造流程

功率模块封装全攻略:从基本流程到关键工艺

碳化硅特色工艺模块简介

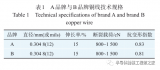

功率模块铜线键合工艺参数优化设计方案

模块工艺——隔离工艺(Isolation)

模块工艺——隔离工艺(Isolation)

评论