为了实现未来的空间系统,并使太空更容易进入,首先,该行业必须解决抗辐射半导体的问题。太空级功率集成电路(IC)有许多主要的成本驱动因素需要解决。

空间应用所需的抗辐射集成电路(IC)体积大,价格昂贵,并且落后于最先进的性能十多年。推动这些现实的因素包括航天级部件所需的广泛测试、传统器件供应的减少、设计抗辐射集成电路的高成本以及密封陶瓷封装的高成本。

如何使功率抗辐射IC更实惠?我记得我最初几年在高可靠性产品线的业务开发工作,为空间应用开发IC。当我熟悉产品组合和客户时,我注意到我认为是“传统”产品的大量销售。其中许多部件 - 早在1980年代和1990年代设计 - 仍在设计到新系统中。此外,通常用于商业应用的功率IC在抗辐射领域售价超过2,000美元。

测试成本高

大多数抗辐射集成电路都经过 MIL-STD-883 和 MIL-PRF-38535 的测试和认证。这些是高可靠性行业已经使用了 20 多年的通用标准。

虽然这些标准帮助政府和供应商避免了有时为同一产品管理数百个定制规格,但由于航天级产品需要进行广泛的测试和筛选,与同等商业功能相比,定价仍然很高。

测试成本往往淹没了材料成本。一些IC测试可以在制造成本不到一美元的IC上运行数百美元。这种测试与制造成本的差异在塑料设备上更为明显。这种额外的测试应该可以提高组件的可靠性。

高可靠性行业一直在评估更可靠的商业流程,例如汽车(AEC-Q100)和增强塑料(V62),它们利用过程监视器使这些商业产品更加可靠,而无需航天级产品通常需要昂贵的100%筛选。

由于缺乏用于空间应用的最先进的电子设备,许多客户求助于升级商业设备。上筛 - 包括测试商用现货(COTS)部件,以查看它们是否符合军用规格 - 通常花费数十万美元,并且必须为每批新设备完成。也不能保证这些部件会工作;此外,上筛选过程本身可能导致可靠性问题,例如潜在缺陷。对于功率器件,找到“偶然抗辐射”且适合上筛选的商用IC更加困难。出现这种情况是因为功率IC受到更高的电压,并且容易受到太空中重离子引起的灾难性单事件效应和总电离剂量(TID)效应引起的退化的影响。

作为MIL-PRF-38535规范的一部分,正在努力标准化空间塑料流。政府机构和工业合作伙伴正在考虑“P级”标准。虽然该标准是朝着正确方向迈出的一步,但它确实计划纳入一些昂贵的筛选步骤,例如100%老化,100%X射线和序列化数据日志:所有这些手动完成的昂贵过程。

供应减少

许多较旧的航天级组件都在芯片组上,这意味着它们无法再制造,因此供应有限。供应限制通常发生在晶圆制造设施因缺乏业务可行性或出于升级目的而关闭工艺时。有时,这些工艺会被转移到新的制造工厂,但通常情况下,这些工艺会一起过时。即使在工艺转移到新设施的情况下,这种移动也可能导致IC在电上等效,但辐射性能却大不相同。

这些旧组件的供应减少意味着生产计划面临风险,组件价格将继续上涨。

密封陶瓷封装成本高

传统上,太空级元件采用密封陶瓷封装。密封封装可保护芯片免受潮湿影响,但通常比塑料封装贵 100 倍,并且还会对组件的性能产生负面影响。包括政府客户在内的客户正在花费数千万美元在更小、更高性能的工艺节点中开发数字应用专用IC(ASIC),但使用的是次优封装。这些陶瓷

IC封装通过其较长的引线和/或较大的再分布层引入大量电阻和电感。对于抗辐射功率IC,这些封装带来的性能下降更为明显。

对于最先进的组件,商业制造商几年前放弃了传统封装,选择了晶圆芯片级封装(WCSP)。晶圆芯片规模通过层和晶圆凸块的重新分布实现近乎理想的芯片到板连接。WCSP可降低寄生电阻和电感,从而对功率IC的效率和性能产生负面影响。不幸的是,由于芯片的热系数与用于飞行的电路板之间的差异,WCSP目前不被航天应用所接受。鉴定航天级器件所需的大量热循环导致 WCSP 的焊点可靠性。

为了降低成本并提高性能,必须为空间应用探索更新的封装技术。正在与各种供应商合作以改进包装,但他们尚未获得资格。展望未来,一些新的供应商决定只发布塑料的太空级部件 - 这是一个良好的趋势,在卫星和航天器开发商中得到更广泛的采用,特别是在新太空市场。

抗辐射IC设计成本高

即使是所谓的简单IC,设计和产品化也需要花费数百万美元。如果需要抗辐射,它至少会贵三倍。IC设计需要高度专业化、非常昂贵的计算机辅助设计(CAD)工具,这些工具使用制造现场开发的组件和模型,并且特定于工艺节点。IC有时有数百万个晶体管,分布在数百个原理图和子系统中。CAD工具以及适当的验证是复杂IC获得一次通过成功的机会很小的主要原因。

问题是抗辐射设计破坏了这些工具。抗辐射性能所需的独特布局和修改导致这些工具吐出数千个设计规则违规。在这数千条设计规则违规事件中,可能潜伏着一些关键的东西,比如短路或连接不良。除了设计规则检查器无法正常工作外,确保元件正确连接的布局与原理图检查也由于抗辐射修改而不起作用。如果没有适当的工作工具,成功的机会是02。这意味着抗辐射IC设计人员首先必须投入多年和数百万美元与制造设施合作,修改这些工具以正确用于抗辐射设计。

使用专有的TalRad[辐射晶体管调整布局]工艺,Apogee Semiconductor正在开发一种抗辐射混合模拟/数字PWM[脉宽调制]控制器,以驱动GaN [氮化镓]和硅FET[场效应晶体管],可与商业最先进的性能相媲美。这项工作部分由NASA资助,正在与美国宇航局喷气推进实验室合作开发。

即使降低了设计和封装成本,测试成本仍然主导着集成电路的经常性成本。这就是行业必须考虑使用汽车工艺流程使用的过程监控器并调整筛选流程以优化成本和可靠性的地方。好消息是,供应商正在努力降低抗辐射组件的成本,使New Space客户更容易获得它们。

审核编辑:郭婷

-

电源

+关注

关注

184文章

17573浏览量

249474 -

集成电路

+关注

关注

5381文章

11381浏览量

360843

发布评论请先 登录

相关推荐

李开复:中国擅长打造经济实惠的AI推理引擎

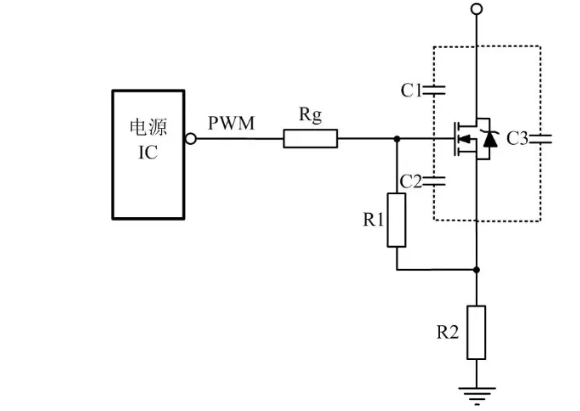

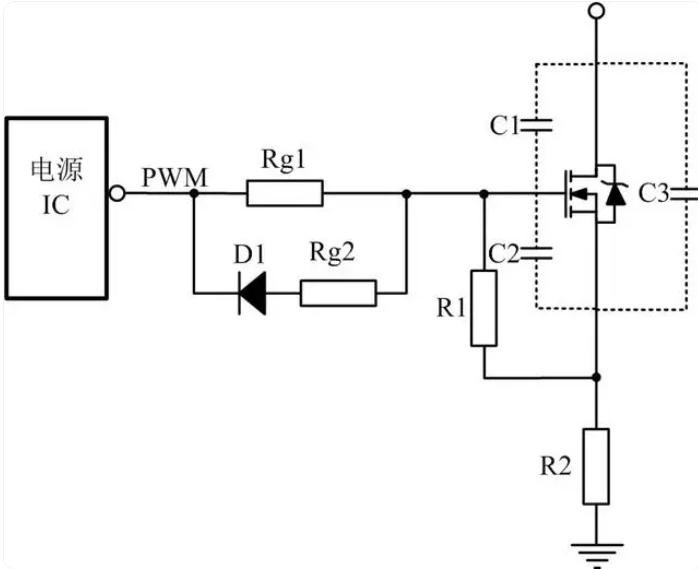

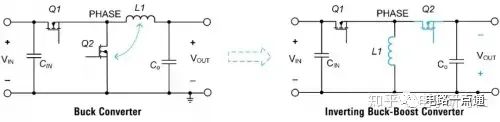

MOS管电源IC直接驱动电路

LED照明电源IC CY3783A产品概述

LED照明驱动电源IC U6117S介绍

德州仪器与台达电子合作开发下一代电动汽车车载充电和电源解决方案

TIDA-010074-适用于电信BBU和电动摩托车电池的经济实惠型锂离子电池组 PCB layout 设计

合科泰有哪些电源IC产品?合科泰半导体电源IC选型技巧分析

电源驱动ic的作用是什么 电源IC驱动电路设计图

介绍八种常见的电源管理IC芯片

代换IC技巧,让PCB电路设计更完美

电源IC过流检测端的贴片电容容量改大或改小会怎么样?

Microchip 的电源管理IC (PMIC) MCP16502

让电源IC更经济实惠

让电源IC更经济实惠

评论