IC 业务面临的最大挑战之一是寻找模拟人才来完成工作。由于模拟组件通常只是 SoC 的一小部分,因此与模拟工程师相比,对数字工程师的需求约为 10 比 1 至 20 比 1。对于模拟设计人员来说,更长的培训时间和更严格的学习曲线加剧了这种情况。此外,对片上模拟 IP 集成的需求也在不断增加。SoC 不断增加其复杂性和集成度,添加更多 PMU 组件、传感器组件、安全组件和时钟,以实现无数功能。模拟 IP 通常设计为特定的硅工艺选项,达到一定的规格。这给IP 供应商和 IP 客户带来了许多挑战。对于 IP 提供商来说,每个客户的要求都是定制的解决方案,完成的模拟 IP 很难转售。对于客户来说,许可模拟 IP 基本上是分包工作负载,很少享受 IP 重用的好处。然而,现实世界是模拟的,模拟IP 是数字领域和现实世界之间的重要接口。

是什么造就了一个好的模拟 IP?具体来说,创建一个好的模拟 IP 需要什么?合适的电路架构至关重要。对于商业产品,架构应该是稳定、健壮的,并且对工艺和生产变化有足够的容忍度。来自代工厂的最新 PDK(工艺开发套件)确保了模型与硅之间的良好相关性。在 PVT 角落进行彻底的行为和电路仿真,确保电路按预期工作。定制布局需要了解电路、工艺对性能的影响以及对布局和布线的细致关注。上述工作需要一个具有多领域知识的经验丰富的团队。例 如,模拟工程师需要对将影响电路性能的布局规则和工艺效应有一定的了解,布局工程师需要能够识别每条迹线(功耗、敏感或通用)和器件匹配的关键要求。凭借良好的电路架构、精确的 PDK、全面的仿真、详细的布局以及经验丰富的模拟设计流程团队,可以提供高质量的模拟 IP。

由于许多原因,例如难以找到模拟人才,迭代和手动密集型设计程序,工艺依赖性,也许只是习惯,客户经常要求“硅验证”模拟 IP 或需要“硅证明”来验证模拟 IP。在某些情况下, “硅验证”是 IP 质量的良好指标,但大多数情况下,您根本找不到适合您确切需求的 “硅验证” IP。“硅验证” IP 是已经制造并在硅上验证其功能的 IP。对于某些 IP,如 SerDes,PCIe 和 USB,“硅验证” 是一个非常好的质量指标。这些 “硅验证” IP 有几个共同的特征:

• 它们具有标准组织,定义了在项目之间不会更改的功能和特性;

• 它们是具有复杂功能和特性的大型 IP,通常可以作为独立产品(芯片)出售;

• IP 对应于特定的产品代系,通常在特定的工艺节点上设计;

• 迁移到新的流程节点时,IP 也会使用新的设计和功能进行升级

但是,对于所有项目、产品和跨过程节点通常需要的通用或“更简单”的模拟 IP(如 LDO、PMU 或传感器模块),这些IP 通常需要根据特定的项目规范进行优化或定制。在这些情况下,要求 “硅验证” 的 IP 是否仍然合理?“硅验证” IP 需要与新项目具有相同的工艺(和工艺选项),设计参数,功能和特性,以保持其 “硅验证” 状态。一个新项目很少与现有的 “硅验证” IP 完全匹配。用户有两个选择,第一个选择是使用可能过度设计或性能不足的现成 IP,这意味着项目的成本将增加,或者将不得不妥协 IP 的规格。第二种选择是根据项目要求修改现有知识产权,这相当于为项目开发新的知识产权;如果用户愿意,在将其集成到项目中之前,加倍努力将 IP 带到测试芯片并在芯片上进行验证。在现实世界中,很难获得完全符合您需求的“硅验证” IP。

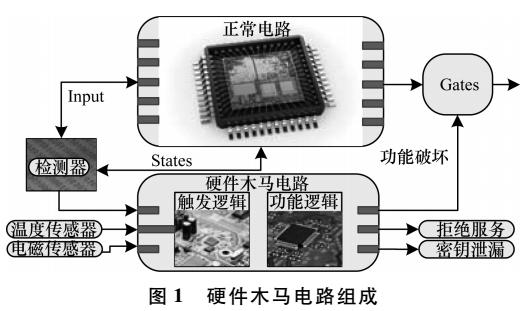

将模拟 IP 组合到一个宏 (macro) 中,可以简化维护和简化 SoC 集成。宏 (macro) 还可以设计为满足特定解决方案,并对 IP 中的组件进行单独个别优化。电源和时钟是 SoC 芯片的基本要求。由上电复位 (POR)、带隙和基准电压源(BG)、低压差稳压器 (LDO) 和 RC 时钟组成的 PMU 宏 (macro) 可以为整个芯片提供电源、基准电压源和基本时钟信号。SoC 项目可以轻松将 PMU 宏 (macro) 集成到其系统中,而无需单独集成每个模拟块,从而加快开发过程并降低人为错误的风险。另一个例子是片上安全性。SoC 需要能够检测从物理更改到 SoC 操作环境的可能 “攻击”。由电压脉冲干扰检测器、时钟监视器、温度传感器和独立电源组成的安全宏 IP 可以检测恶意黑客攻击导致 SoC 电源、时钟和/或温度 的意外变化。

Agile Analog 的核心技术是以“形式化流程” 方法实现模拟电路设计 “艺术” 。除了经验丰富的模拟设计团队外,凭借Agile Analog 的内部 ComposaTM 平台和专门的软件工程师团队,我们正在以革命性的方式开发和交付模拟 IP。我们的 方法定义了 IP 的 “什么”,也定义了 IP 的 “为什么” 和 “如何” 工作。Agile Analog 设计的 IP 可以在任何流程节点中生成,验证流程可确保每次交付的 IP 的性能和质量。Agile Analog 的 IP 生成引擎可以“完全按照客户需要的规格”提供模拟 IP,并针对面积和性能进行优化。它也可以反过来使用,评估不同过程节点或设备选项的 IP 性能。

举例来说,电源管理模块和传感器等基本 IP 是每个 SoC 中必不可少的模块,但对于模拟专家来说,这项任务通常是平 凡而无趣的。通过利用 Agile Analog 反复生成 IP 的能力,客户可以专注于他们的差异化设计,即他们产品的 “秘密武器”。例如,生成多个版本的 IP 以匹配客户 MCU 产品线的不同版本与生成一个版本所需的时间大致相同,从而显着缩短了开发时间。在新工艺上开发下一代产品时,Agile Analog 可以在新的工艺节点中无缝生成 IP,而无需寻找和鉴定新供应商。

数字化设计流程从设计模块化和自动化中受益匪浅。数字设计与流程无关,允许跨项目和流程完全重用 IP。全面的设计工具、设计流程和验证方法允许在流程的每个阶段检查数字项目的一致性和合规性,从而减轻设计人员的大量工作,从而提高生产力。设计过程高度自动化,即使对于最先进的过程节点,也期望从中生成复杂、高质量、一次成功使用的IC。另一方面,模拟设计高度依赖于电路模块、工艺节点和设计团队经验的复杂性。模拟设计流程自动化有几种方法,但通常它们都集中在特定方面,例如更容易移植到新的过程节点(基于现有设计),或者从原理图到布局的自动化。这些渐进式改进提高了模拟设计的效率,但距离我们在数字设计中看到的自动化还有很长的路要走。Agile Analog 的模拟 IP 生成过程,是模拟自动化的革命性方法。在 IP 开发过程中,Agile Analog 的 IP 不局限于特定的过程,可以为更广泛的客户群提供服务,从而在模拟领域实现真正的 IP 重用。

关于作者:

Michael Lei 是 Agile Analog 亚太地区的 FAE。于 2007 年作为射频电路设计师开始其职业生涯,曾在台湾和中国的多家 IC 设计公司设计射频电路、领导射频项目、领导 SoC 项目、推出新产品、管理客户项目并为新项目进行技术营销。主要专长是蜂窝、Wi-Fi、蓝牙及其在物联网应用中的使用的射频和模拟电路和系统。

编辑:黄飞

-

usb

+关注

关注

60文章

7945浏览量

264703 -

PCIe

+关注

关注

15文章

1239浏览量

82665 -

基准电压源

+关注

关注

1文章

140浏览量

20836

原文标题:浅谈模拟IP

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

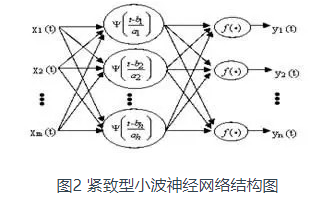

分形特征的模拟电路故障诊断方法

模拟电路故障诊断中的特征提取方法

什么是共同模拟

混合信号SoC助力模拟IP发展

模拟电路故障诊断中的特征提取方法

基于小波包特征熵和粒子群优化的模拟电路故障诊断

基于特征匹配的IP软核硬件木马检测

模拟电路诊断中故障特征的提取方法

背景场特征在电磁波模拟中有怎么样的应用

煤层开采覆岩破坏特征的数值模拟试验综述

浅谈IP网络广播系统

浅谈模拟IP的共同特征

浅谈模拟IP的共同特征

评论