性能就是消除瓶颈,以最大程度地减少延迟并最大化吞吐量。当今的高性能嵌入式计算 (HPEC) 系统集成了强大的处理子系统,每个子系统都可能是一个功能齐全的处理节点,需要与其他处理节点共享数据。为了最大限度地提高整体系统性能,需要最快、最高效的处理器到处理器数据路径。借助 VPX,嵌入式系统摆脱了 VMEbus 共享并行总线模型。

与当今基于串行结构的系统相比,VME 性能总体吞吐量较低。一个原因是数据总线传输速度慢。另一个问题是一次只有一个节点可以通信时发生的总线仲裁惩罚。对于基于现代串行架构的系统(如 VPX),以太网也可用于在节点之间传递数据。交换以太网架构使节点能够并行通信,几乎消除了共享总线的瓶颈。然而,当今的处理器速度和功能远远超过以太网速度,使数据路径和 CPU 密集型网络堆栈再次成为关键的性能瓶颈。

其他替代结构,如Serial RapidIO(SRIO)和InfiniBand,也有其自身的局限性:很少有芯片供应商支持SRIO,这意味着它的采用受到缺乏软件的阻碍。由于SRIO没有通用的软件API[应用程序编程接口]被广泛采用,因此系统设计人员通常需要编写自己的定制软件。对 SRIO 的操作系统支持也很少,这使得 SRIO 设备驱动程序也是一种定制开发。就其本身而言,InfiniBand在可部署防御系统中的吸引力也有限,因为对实时操作系统的软件支持有限。它还受到硅器件的高成本和单一来源供应商的有限支持的阻碍。

如今,几乎所有现代处理器都使用 PCI Express (PCIe) 总线作为板载外设的高速互连。在大多数处理系统中,PCIe 接口还提供进出处理器的最快数据路径。PCIe 接口支持多种数据速率:第 1 代接口以 2.5 Gbps 的速度运行,第 2 代接口将数据速率翻倍至 5.0 Gbps。 第 3 代接口将此速度提高到 8.0 Gbps,并且通过使用更有效的数据编码机制,有效数据传输速率成为第 2 代的两倍。PCIe Gen4标准的开发即将完成,Gen4设备将于2017年晚些时候开始从供应商处发货,再次旨在将性能提高一倍。

为什么使用 PCIe 绕过以太网或其他结构接口设备?用户报告了更低的延迟、更高的吞吐量和额外的附带好处,例如降低功耗、增加 MTBF [平均故障间隔时间] 和降低成本。然而,直到最近,使用 PCIe 技术支持主机到主机通信的好处需要复杂的设置 PCIe 设备和交换机的配置。它还要求定制PCIe共享内存驱动程序软件,大大降低了其可取性。

Dolphin Interconnect Solutions以其StarFabric技术而闻名,它为HPEC系统开发了一种具有巨大前景的解决方案。其 eXpressWare 软件套件使用 PCIe 连接来创建更快、更灵活的消息和处理器到处理器通信数据传输机制。该软件经过优化,可利用 DMA [直接内存访问]、PCIe 组播和多核处理等硬件功能。该软件隐藏了 PCIe 设置的复杂性,简化了主机到主机架构的设置和配置。

当支持所有必需的 PCIe 交换机配置时,该软件可以自动检测 PCIe 端点并将其配置为透明或非透明端口,设置消息队列和数据传输窗口,以及配置和管理数据传输资源(如 DMA 引擎)。此外,它还带有标准软件API接口,可以使用大多数软件开发人员已经熟悉的软件范例进行更快的软件应用程序开发。

Dolphin 的 eXpressWare 使 HPEC 系统设计人员能够利用最高水平的数据结构性能来满足国防工业的加固设备需求。为了获得使用 PCIe 向嵌入式系统设计人员进行节点到节点数据传输的好处,Curtiss-Wright 最近在运行 Linux 和 Wind River VxWorks 操作系统的嵌入式英特尔 SBC 和 DSP 引擎中添加了对 eXpressWare 的支持,并将这种支持扩展到基于 Power 架构的主板。坚固耐用的嵌入式系统依靠高性能结构来减少数据传输时间的延迟。PCIe 为实现低延迟、高吞吐量处理器到处理器性能提供了当今的最佳解决方案。通过提供通用软件 API 并屏蔽 PCIe 设备编程的复杂细节,eXpressWare 为 HPEC 系统设计人员带来了突破,并为嵌入式硬件带来了高速、低延迟的点对点通信。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19317浏览量

230098 -

芯片

+关注

关注

456文章

50892浏览量

424337 -

总线

+关注

关注

10文章

2890浏览量

88147

发布评论请先 登录

相关推荐

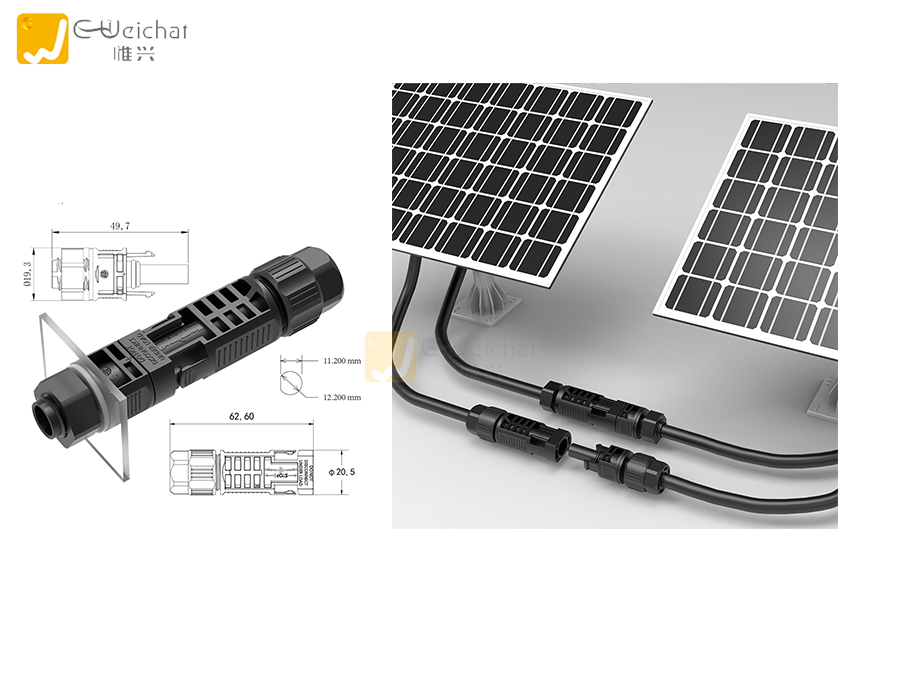

光伏连接器外壳:超越简单塑料的复杂性与重要性

KeyStone设备的PCI Express (PCle)常见问题

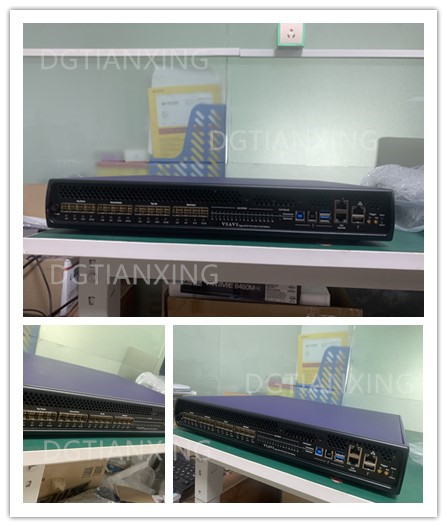

VIAVI Xgig 4K16 PCI Express 4.0 协议分析仪平台介绍

使用TI PCI-Express Gen5.0转接驱动器进行眼图扫描

LMK6H和LMKDB1xxx PCI Express合规性报告

DS50PCI401 2.5 Gbps/5.0 Gbps 4通道PCI Express中继器数据表

DS50PCI402 2.5 Gbps/5.0 Gbps 4通道PCI Express中继器数据表

XIO2001 PCI Express至PCI总线转换桥接器数据表

PCI总线PCB设计丨实现高效外围部件互连的关键要素

Teledyne LeCroy扩展CrossSync PHY技术到PCI Express 6.0

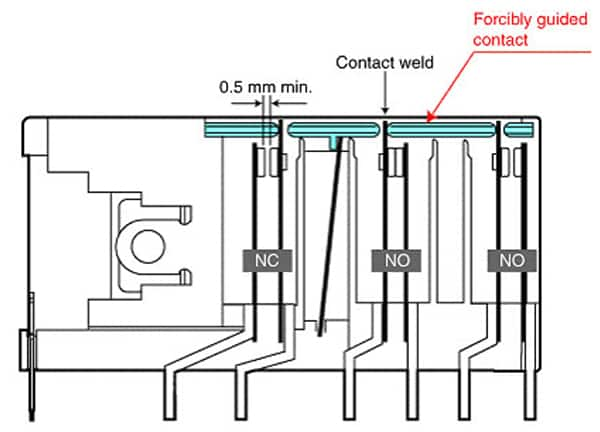

解决选择合适安全控制器的复杂性

消除PCI Express配置的复杂性,优化HPEC系统设计

消除PCI Express配置的复杂性,优化HPEC系统设计

评论