多晶硅栅的形成是集成电路工艺中最关键的步骤,因为它包括了最薄的栅氧化层的热生长(干氧和湿氧),形成多晶硅栅的先进且复杂的光刻技术和干法刻蚀技术,以及需要精确控制且复杂的侧墙工艺。

多晶硅栅结构通常是一代集成电路工艺中物理尺度最小的结构,也是形成晶体管的关键。多晶硅栅形成的一般流程是,首先使用高温热氧化生成栅氧化膜,膜的厚度约为 1~10nm(由于在集成电路中有不同工作电压的场效应晶体管,所以栅氧化层的厚度也不相同,需要采取多个步骤才能完成不同厚度的栅氧化层),然后进行多晶硅栅的化学气相沉积和掺杂(扩散或离子注入),最后进行光刻和干法刻蚀。

多晶硅栅光刻工艺使用的光刻机是同一技术代集成电路工艺线中最先进、最昂贵的设备,它采用 UV 光源进行曝光,波长从g线(436nm)到DUV(248pm 和 193nm),以及 193nm 浸没式;在光刻掩模版上采用了 OPC和PSM等技术;在光刻工艺中采用了抗反射层、硬光刻胶技术、多重曝光技术等。

多晶硅栅的刻蚀采用的是最精细的刻蚀设备和技术,通常采用 NF3、 SF6~HBr、CL2,等气体,要求与 SiO2有极高的选择比。多晶硅栅的检测技术也是最精细的检测技术,用于光刻和刻蚀完成后多晶硅栅线宽和形状等的检测。

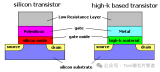

虽然在 45nm 以下的超大规模集成电路制造工艺中,为了解决多晶硅栅耗尽效应,以及多晶硅与高K介质高界面态密度等问题,多采用了高K金属栅工艺,多晶硅栅的重要性有所降低,但是多晶硅栅工艺仍然被认为是集成电路的标志性工艺之一。

审核编辑 :李倩

-

集成电路

+关注

关注

5400文章

11686浏览量

364513 -

多晶硅

+关注

关注

3文章

243浏览量

29446

原文标题:多晶硅栅(Poly-Si Gate)

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

TOPCon太阳能电池接触电阻优化:美能TLM测试仪助力LECO工艺实现25.97%效率突破

单晶圆系统:多晶硅与氮化硅的沉积

为什么采用多晶硅作为栅极材料

Poly-SE选择性多晶硅钝化触点在n-TOPCon电池中的应用

多晶硅的存储条件是什么

今日看点丨美国宣布提高中国太阳能硅片、多晶硅关税50%;联发科天玑 8400 芯片详细参数曝光

效率提升0.15-0.2%:双面Poly和Poly Finger技术在TOPCon电池中的创新应用

多晶硅生产过程中硅芯的作用

多晶硅栅工艺的制造流程

光伏多晶硅的应用领域有哪些

光伏多晶硅的分片方法及优缺点

Poly层厚度对N型TOPCon太阳能电池电学性能的影响

多晶硅栅耗尽效应简述

多晶硅栅(Poly-Si Gate)

多晶硅栅(Poly-Si Gate)

评论