everspin在此生产基于180nm,130nm和90nm工艺技术节点的MRAM产品。产品包装和测试业务遍及中国大陆,中国台湾和其他亚洲国家及其地区。

在平面内和垂直磁隧道结(MTJ)STT-MRAM位单元的开发方面处于市场领先地位。

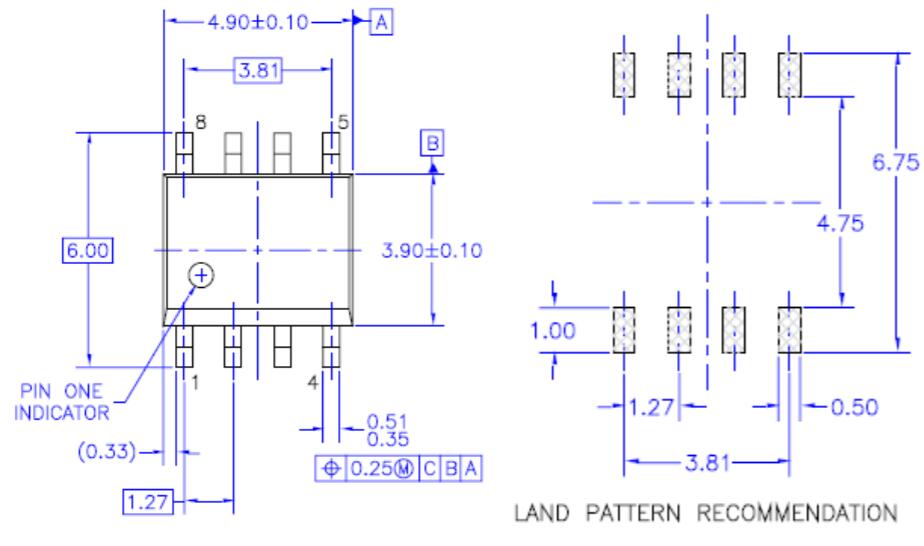

EVERSPIN的SPI产品系列中增加了具有2mm底部裸露焊盘的新型DFN8封装。这种新封装允许该器件既可用于JEDEC标准SOIC-8引脚又可用于DFN8 PCB焊盘图案。图1显示了典型的SOIC-8 PCB焊盘图案。

一些Everspin客户对Everspin“ DC” DFN封装的裸露底部焊盘(4.1mm焊盘)与SOIC-8封装的PCB焊盘之间的边际间隙表示担忧。 Everspin的新型2mm裸露焊盘DFN-8封装缓解了这种担忧。

图1代表了JEDEC标准SOIC-8封装的近似尺寸和建议的PCB焊盘图案(注意:以下尺寸为近似值,可能因供应商而异)

图2和图3分别是Everspin MR25HxxxDC(4.1mm裸露的底部焊盘)和MR25HxxxDF(2.0mm裸露的底部焊盘)的封装尺寸。

由于MR25HxxxDC的4.1mm裸露底垫与SOIC-8 PCB焊盘图案之间存在边际间隙,因此具有2.0mm裸露底垫(MR25HxxxDF)的新封装已获Everspin批准生产,并且与JEDEC兼容标准SOIC-8和DFN-8焊盘图案

。较小的底垫在底垫和SOIC-8的PCB焊盘图案之间提供足够的间隙。

图2-Everspin MR25HxxxDC封装的封装尺寸

图3-Everspin的MR25HxxxDF封装的封装尺寸

审核编辑:刘清

-

MRAM

+关注

关注

1文章

236浏览量

31735 -

PCB

+关注

关注

1文章

1808浏览量

13204

发布评论请先 登录

相关推荐

MR25H40驱动,求助!!

PIC32MM QFN36裸露焊盘怎么处理

一种小体积一体成型电感感量:0.33~10μH 尺寸:2.5mm*2.0mm

MM32SPIN25PF的特点有哪些

MM32SPIN25PF的相关资料推荐

T107A Series 2.5* 2.0mm TCVCXO

MR25HxxxDF的2.0mm裸露底垫新封装已获Everspin批准生产

DC509B LTC3729EUH演示板 | 5V至 14V, 2.5V (25A V)

采用2.0mmx 2.0mm VQFN封装的5V/6A 高效升压转换器TPS61230A数据表

DM505 SoC 15mm封装(ABF)器件版本2.0数据表

浅析MR25HxxxDF的2.0mm裸露底垫新封装

浅析MR25HxxxDF的2.0mm裸露底垫新封装

评论