在systemverilog中方法也可以声明为“static”。静态方法意味着对类的所有对象实例共享。

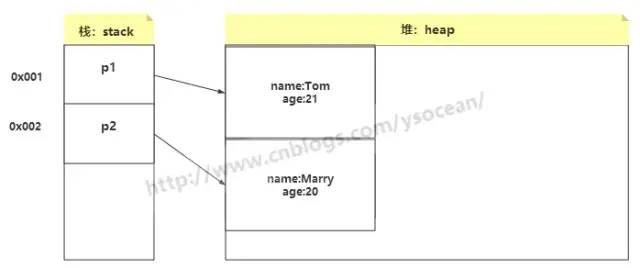

在内存中,静态方法的声明存储在一个同一个地方,所有对象实例都可以访问。

另外,静态方法可以在类外部访问,即使还没有实例化任何一个类对象。

静态方法只能访问静态属性。

从静态方法访问非静态属性会导致编译错误,静态方法也不能是virtual的,也不能使用“this”句柄。

module class_TOP( ); class base; static logic [31:0] data ; //static property logic [31:0] addr; //dynamic property static task munge; //Static method data = 32'h f0f0_f0f0; //OK to access static variable //addr = 32'h ff_0000; //NOT OK since 'addr' is not static $display("data = %h", data); endtask endclass : base base base1; initial begin base1.munge; end initial #10 $fnish(2); endmodule

仿真log:

data = f0f0f0f0 $fnish at simulation time 10 V C S S i m u l a t i o n R e p o r t

在本例中,我们在类“base”中声明了一个名为“munge”的静态方法。

我们访问“munge”可以使用尚未完成实例化的对象句柄“base1”。

需要注意的是,静态方法“munge”只能索引静态变量“data”,如果取消下面这行代码的注释,则会发生编译错误。

因为“addr”不是静态变量,需要实例化后使用对象的句柄才能访问。

//addr = 32'h ff_0000; //NOT OK since 'addr' is not static

静态函数访问非静态变量,会导致编译错误:

Error-[SV-AMC] Non-static member access testbench.sv, 9 class_TOP, "addr" Illegal access of non-static member 'addr' from static method 'base::munge'.

还可以使用类解析操作符访问静态方法,建议使用这种方法,因为它清楚地标识了我们正在访问一个静态方法。

class setIt;

static int k;

static function set (int p );

k = p + 100;

endfunction

endclass

module tbTop;

initial begin

setIt::set(10);

$display("k = %0d",setIt::k);

setIt::set(20);

$display("k = %0d",setIt::k);

end

endmodule

仿真log:

k = 110 k = 120 V C S S i m u l a t i o n R e p o r t

静态变量和静态方法隶属于一个类,而不是类的某个对象实例。如果在静态方法前面加上virtual,你会得到一个编译错误:

class base; virtual static task munge(); endtask endclass

编译log:

Error-[WUCIQ] Invalid qualifer usage testbench.sv, 32 Invalid use of class item qualifers. Cannot use virtual and static keywords together for method declarations.

审核编辑:刘清

-

Verilog语言

+关注

关注

0文章

113浏览量

8226

原文标题:SystemVerilog中的Static方法

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

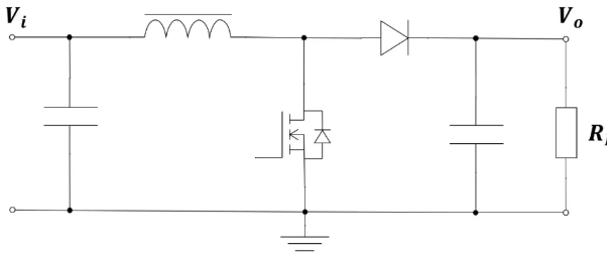

在Boost电源中该怎样去选择电容的型号和电容容量呢?

SystemVerilog 的VMM验证方法学教程教材

JAVA中static、final、static final如何区分

SystemVerilog的随机约束方法

Java中对static关键词的介绍

怎样去使用SystemVerilog中的Static方法呢

怎样去使用SystemVerilog中的Static方法呢

评论