随着晶体管尺寸的不断缩小,为保证栅控能力,需要维持足够的栅电容,因此要求栅氧厚度继续减薄。然而,当栅氧物理厚度减薄到低于 1.5nm时,由于直接隧道效应指数级增加,器件漏电随之大幅增加,从而导致器件无法实际工作。通过将相对介电常数(Relative Dielectrie Constant) 远大于 SiO2(K大约3.9)的高K栅介质材料导入集成电路工艺,如HfO2(相对介电常数为 24~40),可以在保证等效栅氧厚度(Equivalent Oxide Thickness, EOT)持续缩小的前提下,使栅介质的物理厚度相对较大,以抑制栅泄漏电流。然后用TaN、TiN 、TiAI、W 等金属合金或化合物叠层结构取代多晶硅栅,金属叠层具有功函数调节和降低电阻率等作用,可避免多晶硅栅的耗尽效应,同时保证高k栅介质材料与金属栅有较好的接触效果。

目前,高K栅介质与金属栅极技术已广泛应用于 28mmn 以下高性能产品的制造,它在相同功耗情况下可以使集成电路的性能大幅度提高,泄漏电流大幅下降。高K金属栅的应用经历了较长的探索过程:在很长的时间里,晶体管的栅氧化层都是采用高温干法或湿法热氧化硅形成氧化层;后来为了提高 氧化层的介电常数,在氧化过程中掺入N元素形成 SiON栅介质层;随着栅多晶硅厚度的降低,不仅导致电阻变大,还列起器件延迟和栅耗尽效应。在此背景下,在28nm这个工艺节点,工业界大多开始使用 HKMG 作为超大规模集成电路的标准工艺,虽然性能得到大幅提升,但也大大增加了工艺复杂度。

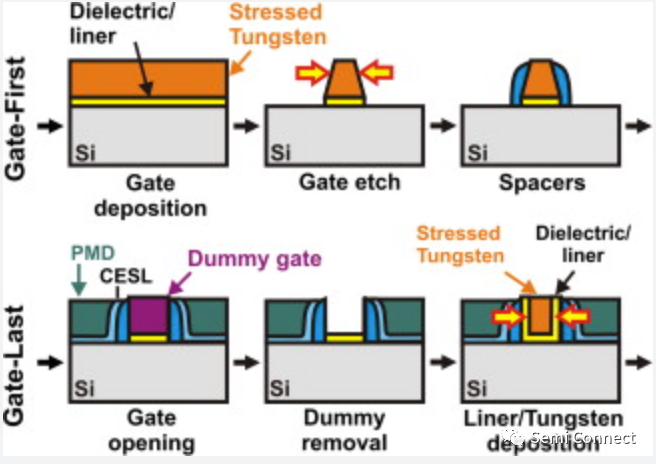

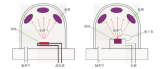

由于HKMG与 Poly/SiO2的 MOSFET结构有很大的不同,导致整个器件的工艺条件发生巨大变化,而且大量的 IP 核需要重新设计。 在最初的工艺开发阶段,业内存在两种制作HKMG 结构晶体管的工艺技术路线,分别是 Gate-Fiest(先栅极)工艺和 Gate-Last(后栅极)工艺。 Gate-First 工艺相对简单,但是 p-MOS 阈值电压很难控制;而 Gate-Last 工艺比较复杂,但它可以有效地调节栅极材料的功函数值,方便调节阈值电压,还可以在p-MOS 的沟道实现改善沟道载流子迁移率的硅应变力。在同时兼顾高性能与低功耗的情况下(如手机应用处理器和基带芯片等),Gate-Last 工艺逐渐取得优势,是目前大规模生产中的主流工艺。

审核编辑 :李倩

-

晶体管

+关注

关注

78文章

10439浏览量

148608 -

介电常数

+关注

关注

1文章

148浏览量

19213

原文标题:高K金属栅工艺(HKMG)

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

深入解析 onsemi FDC8602 双 N 沟道屏蔽栅 MOSFET

厚声RSF系列RSF1JB10K0电阻:高耐压与抗脉冲特性分析

集成电路制造中薄膜生长工艺的发展历程和分类

ISO5851:高可靠IGBT与MOSFET隔离栅驱动器解析

TDK SIOV-S10K***K11金属氧化物压敏电阻:小尺寸大作用

半导体金属腐蚀工艺

从DBC到AMB:氮化铝基板金属化技术演进与未来趋势

金属基PCB加工中热仿真与工艺设计应用

中芯国际 7 纳米工艺突破:代工龙头的技术跃迁与拓能半导体的封装革命

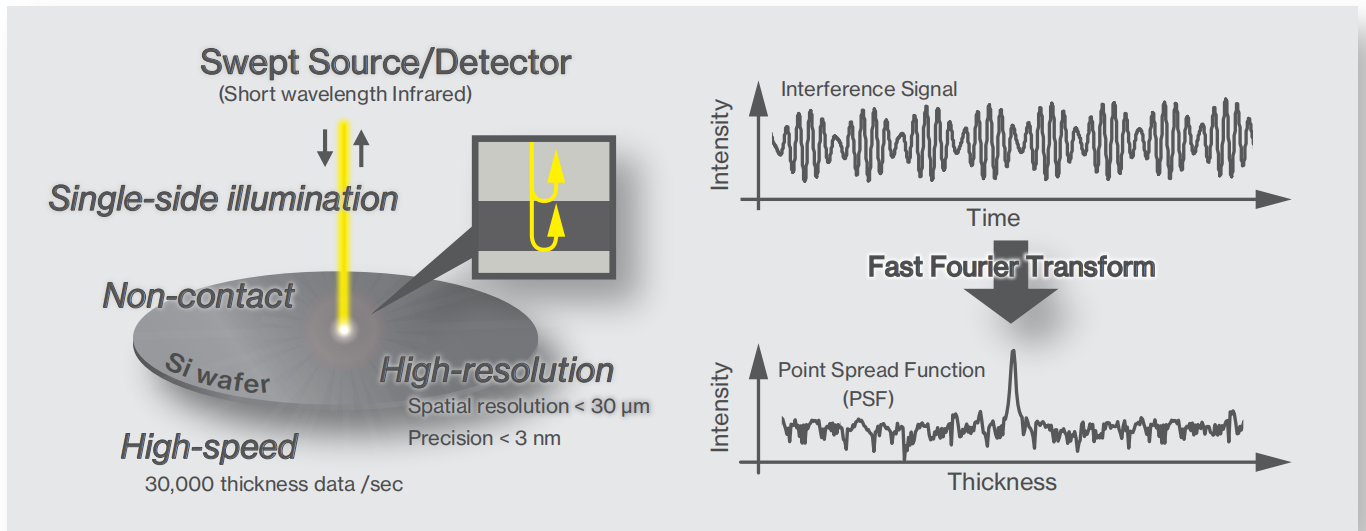

MICRO OLED 金属阳极像素制作工艺对晶圆 TTV 厚度的影响机制及测量优化

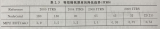

等效栅氧厚度的微缩

IPAC碳化硅直播季倒计时丨沟槽栅VS平面栅,孰是王者?

高K金属栅工艺(HKMG)

高K金属栅工艺(HKMG)

评论