说的是一块数字采集板的调试,主要器件也不多,主要是公司的ADC,ADI的时钟芯片和Xilinx的FPGA,还有一些DC-DC和LDO。

任务呢,也不复杂,就是把板子调通,然后能够通过软件,把ADC采集到的数据给取出来。

主要难点在于,调试的软硬件人员,对JESD204B都不太熟悉,算是临时拼凑出来的调试队伍。

王工,经验丰富的软件人员,擅长我很多我不会的东西,用的操作系统都是Linux的;可是没有调试过204B。

我,算是工作时间长的硬件人员,不过也没经历过204B的调试,就那采集板都是费了九牛二虎之力,所幸,虽然所花时间比较长,但是算是一版成,不需要返工。自己了解的那些204B知识,都是看ADI和TI的文档得来的,也是半懂不懂。

我们这两个人,就这样磕磕绊绊地开始了调试。

关于这个板子的调试,公司领导还特别重视,关键还是各个领导都很重视。所以,需要每日在群里汇报调试进展,要不然,各个领导都会到调试现场来看一下,那滋味其实也不好受。

经常在公司碰到领导们,都会问,板子调试的怎么样了?其实,公司领导们都还是很和蔼的,我也能理解,确实是很想知道板子的进展。

听多了,就需要对自己做做心里工作,比如说,领导们问,板子调试的怎么样了,就当他们在和你打招呼,就像见面问吃饭了没一样。要不然,被问一下心里抖一下,问一下抖一下,就没法静心调东西了。心静,遇到问题才能解决问题。

前期,调试都很顺利。

电源OK,电脑能识别出FPGA,也能给FPGA烧写程序。到这一步,我是稍微松了一口气。

你不知道,每次投完这种多层板回来,我都是战战兢兢的,总担心出现纰漏,导致板子返工,造成金钱和时间的浪费。

时钟芯片也很快配置成功,SYSREF和CLK输出都符合预期。但是很快问题出现了,204B不通。我查了一下微信记录,持续了差不多一周,204B才打通。

调试到最后,发现其实是204B的设计人员把datasheet给写错了,导致我们的寄存器配置错误。不过,也要感谢这个错误,让我俩,对204B都有了个更深层次的理解。要是一上电就调试成功了,就不会反复去看那些资料了。

我们俩,都把xilinx的那篇文档扎扎实实的看了一遍。

不说具体调试过程了,因为也有点忘了,只记得一些心得体会了。

像ADI,TI,Xilinx这些大厂的技术支持都很好,虽然像我们这种级别的公司,很难对接到原厂FAE来服务。但是,他们官网上的提问论坛都很好,给我印象很深的是TI。一般头天问的问题,第二天就会有答复。所以,如果对芯片使用上有什么问题,可以上去提问一下。

看xilinx的文档时,最好看和软件相匹配的版本,要不然,可能相同地址的寄存器,代表的意思不一样。我们就是出现这种情况,随便从bing上搜索了一下应用文档,见也是官方的,就看了起来。最后才发现,新版本上的寄存器的意思和老版本上有出入,被误导了不少时间。

有条件的话,还是两个人一起调试比较好。有时候对方不经意的一句话,都可能激发你的调试思路。更重要的是,可以避免一个人时思维僵化,自信心丧失。

王工和我,碰到问题,都会先从自己的设计找原因,这也使我俩合作的非常愉快。如果软硬件人员,互相推脱不是自己的问题,然后就不管了,非常影响项目的进度。

工程不是科研,时间到了,一般都能出个结果,所以调不出来的时候,也要用这个激励一下自己。

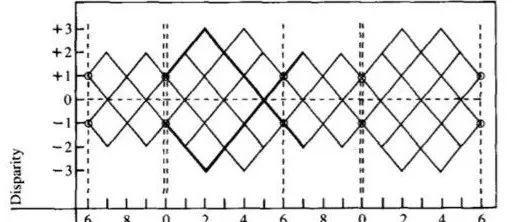

JESD204B之8b/10b编码

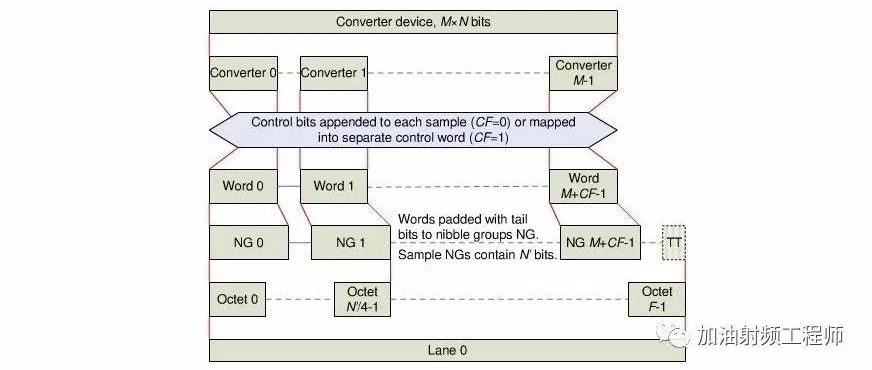

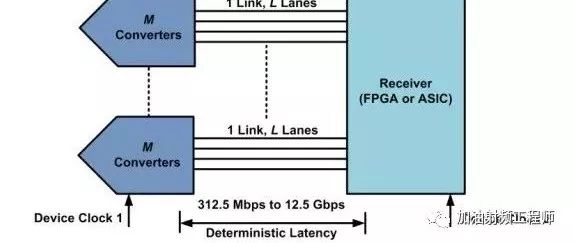

JESD204B传输层

JESD204标准阅读后的十项总结

JESD204B(一)

审核编辑:刘清

-

FPGA

+关注

关注

1631文章

21806浏览量

606688 -

ldo

+关注

关注

35文章

1955浏览量

154112 -

DC-DC

+关注

关注

30文章

1960浏览量

82131 -

CLK

+关注

关注

0文章

127浏览量

17247

发布评论请先 登录

相关推荐

调试ADS52J90板卡JESD204B接口遇到的问题求解

JESD204B的系统级优势

JESD204B串行接口时钟的优势

如何让JESD204B在FPGA上工作?FPGA对于JESD204B需要多少速度?

JESD204B协议介绍

JESD204B的优势

JESD204B SystemC module 设计简介(一)

JESD204B标准及演进历程

JESD204B使用说明

JESD204B具体调试过程

JESD204B具体调试过程

评论